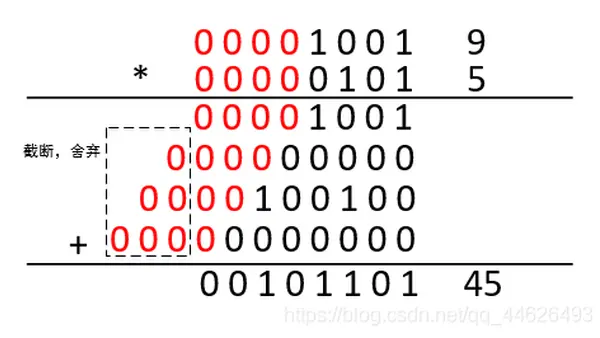

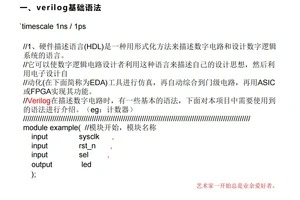

Verilog实现16bits有符号型乘法源代码

AHT10读取温湿度工程

基于FPGA的出租车计价器设计Verilog源代码

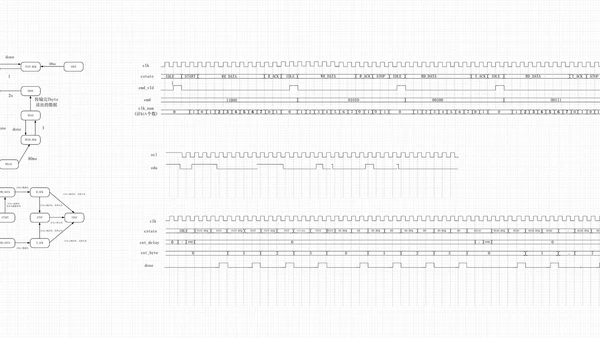

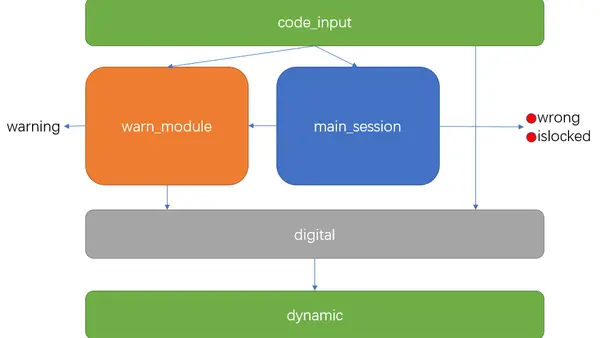

EGO1开发板-vivado2020.1-电子密码锁资源介绍

FPGA很有价值的27实例经典案例

基于FPGA的手动及红外循迹_王同学

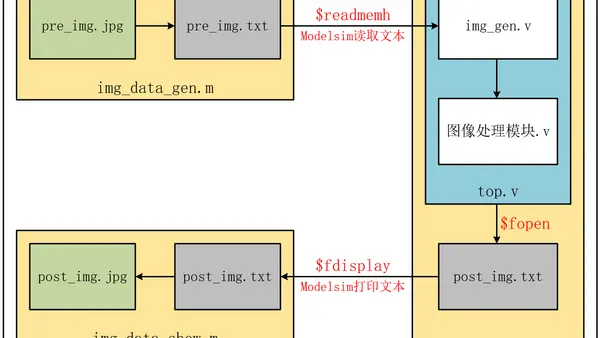

Modelsim联合Matlab搭建FPGA图像仿真平台

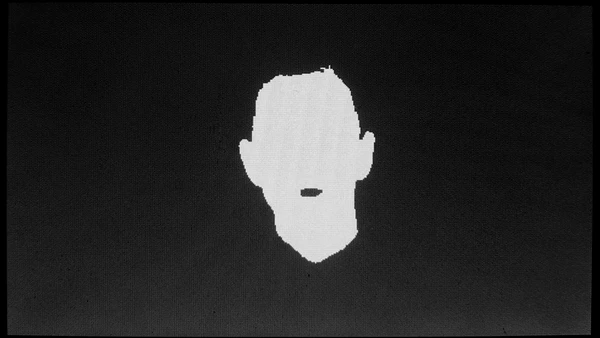

FPGA实现人脸检测

5天零基础做的第一个工程,赞

ZYNQ_MINI_REVB原理图.pdf

FPGA – 基于FPGA的HDMI显示

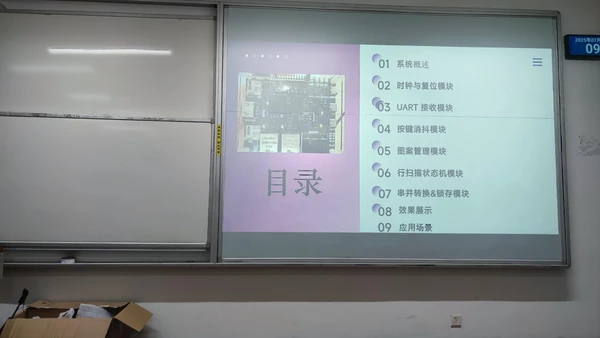

2024年夏令营学员项目代码展示(基于FPGA的广告点阵屏)

1

2

3

4

跳至