一、FPGA的核心组成与工作原理

1. 可编程逻辑单元(CLB)的结构与功能

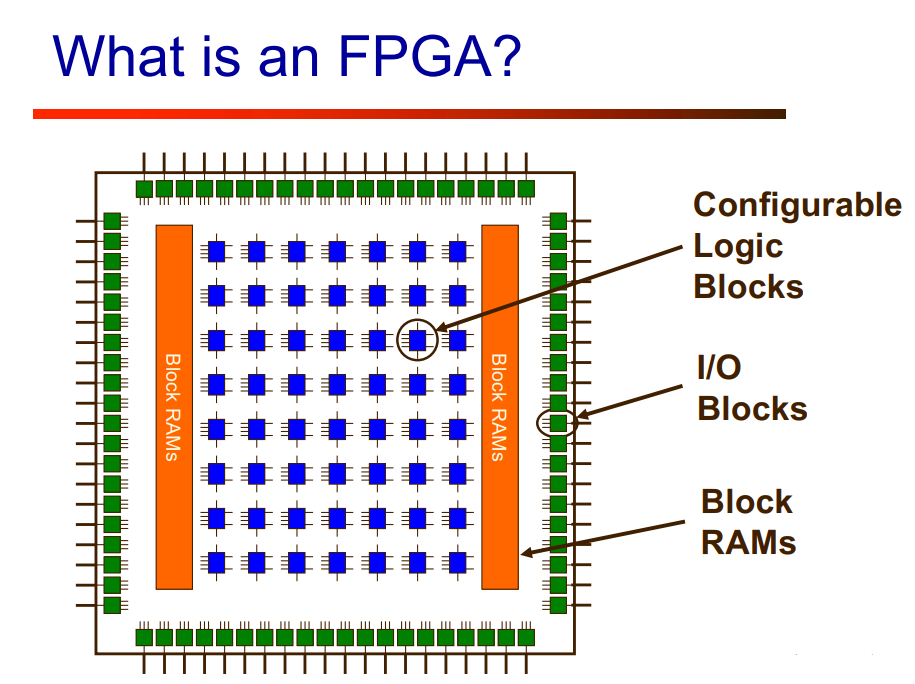

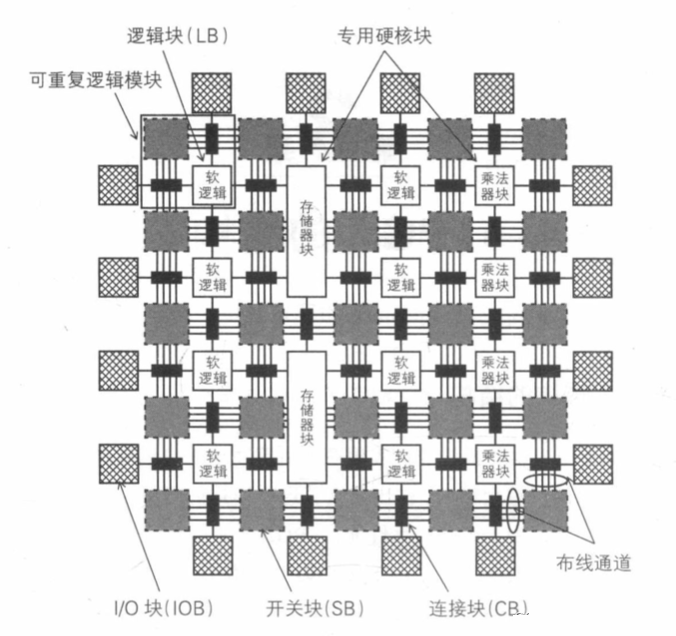

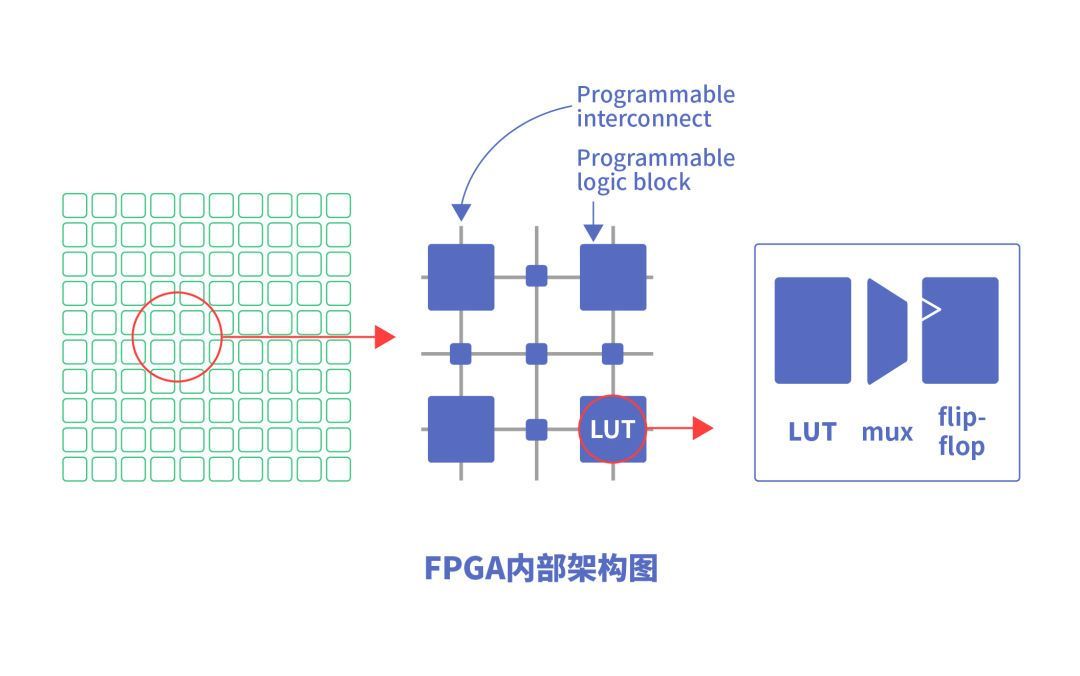

FPGA的核心功能实现依赖于可编程逻辑单元(CLB),其作用类似于可灵活拼接的“硬件积木”,通过配置可实现从简单逻辑门到复杂运算单元的各类功能。每个CLB通常由两个Slice组成,根据功能侧重分为SLICEL(逻辑型)和SLICEM(存储型),因此CLB也对应分为CLBLL和CLBLM等类型。CLB的内部结构以“查找表(LUT)+触发器+多路复用器(MUX)”为核心,辅以进位逻辑、算术逻辑等附加模块,形成兼具组合逻辑运算、状态存储和信号路由能力的基本单元。

查找表(LUT)是CLB实现组合逻辑的核心,本质是小型存储单元,通过预设输入-输出对应关系实现布尔函数运算。例如4输入LUT包含16个存储单元(对应2^4种输入组合),可存储任意4输入单输出逻辑函数的真值表,输入信号通过地址线选择对应存储单元的输出,实现实时逻辑计算。需要注意的是,LUT仅处理组合逻辑,无法存储状态,因此必须与触发器配合构成完整逻辑单元。

触发器(Flip-Flop)作为状态存储单元,负责保持数据或同步信号,其标准结构包含数据输入(D)、时钟(CLK)、时钟使能(CE)、复位(RESET)和输出(Q)端口。工作时,触发器在时钟边沿(可配置为上升沿或下降沿)锁存输入数据,时钟使能信号(CE)控制更新时机——仅当CE=1且时钟有效时写入新数据,否则保持当前状态;复位功能可强制将输出置为0或1,确保系统启动时的确定性。触发器与LUT的绑定是实现时序逻辑的基础,例如构成寄存器、计数器、状态机等模块。

多路复用器(MUX)则起到信号路由选择作用,通过可编程控制信号从多个输入源中选择特定路径,增强逻辑单元的灵活性。典型应用包括选择不同LUT的输出、切换触发器的输入来源(如直接数据输入或LUT运算结果),或实现状态机的跳转控制。MUX的可编程特性使单个CLB能动态适配组合逻辑、时序逻辑或混合逻辑设计,避免硬件资源浪费。

2. 可编程互连结构的配置机制与数据传输

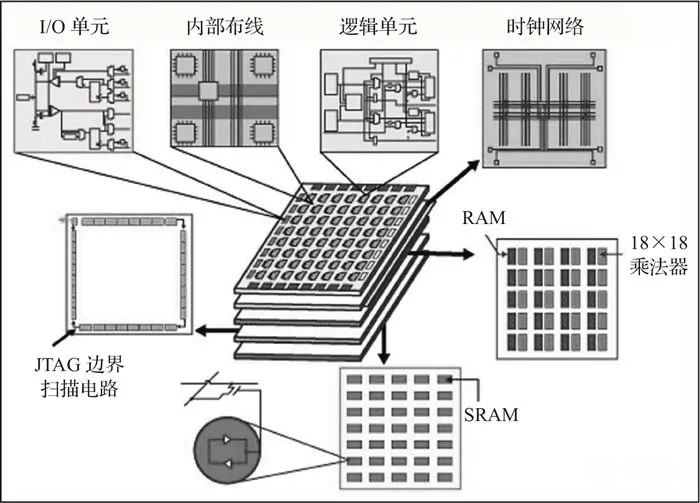

FPGA的可编程互连结构是连接各CLB与功能模块的“内部交通网络”,通过可配置线路实现信号的灵活路由。其配置机制主要分为主动配置、被动配置和JTAG模式三大类:主动模式下,FPGA通过内部控制器从外部存储器(如SPI Flash)读取配置数据并自加载;被动模式由外部设备(如单片机)控制配置过程,时钟信号由外部提供;JTAG模式则支持在线编程与调试,可与其他模式共存。配置数据宽度支持串行(1位)或并行(8/16/32位)传输,适应不同速率需求。

数据传输路径依赖于多层次布线资源,包括全局布线(传输时钟等全局信号)、局部布线(连接相邻CLB)和长线资源(跨区域信号传输)。布线资源通过可编程开关矩阵(PSM)实现动态连接,开关矩阵内部包含大量晶体管开关,通过配置信号控制导通状态,从而构建自定义的信号传输路径。例如,当需要连接两个距离较远的CLB时,配置工具会自动选择合适的长线资源,并通过开关矩阵打通中间节点,确保数据高效传输。这种动态路由能力使FPGA能适应任意逻辑拓扑,是硬件可编程性的物理基础。

二、FPGA的硬核模块与专用功能

1. 存储与运算加速模块

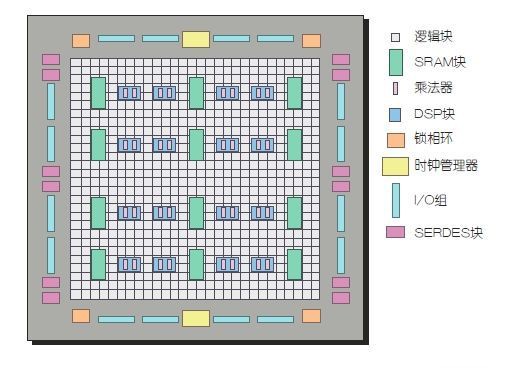

除基础逻辑单元外,FPGA通过集成专用硬核模块提升特定场景的处理效率,相当于为通用硬件平台加装“专用工具”。Block RAM(BRAM)是最核心的存储硬核,作为片上大容量存储器,其架构支持单端口、双端口、FIFO等多种配置。以Xilinx 7系列FPGA为例,36Kb BRAM基本单元可拆分为两个18Kb子模块,支持位宽与深度的灵活组合(如36Kb可配置为1024×36bit或2048×18bit),双端口模式下两个独立端口可异步读写不同地址,配合字节写使能(Byte Write Enable)支持局部数据更新,理论带宽可达21.6Gbps(300MHz×36bit×2端口),满足高速数据缓存需求。

DSP模块是数字信号处理的“加速器”,专为乘加运算(MAC)优化,广泛用于通信、图像处理等领域。其核心结构包含乘法器、加法器和累加器,支持定点/浮点运算,部分高端模块集成预加器和流水线寄存器,可实现多周期运算的并行执行。例如在5G基站信号处理中,DSP模块可并行完成多个子载波的调制解调运算,处理速率比纯CLB实现提升3-5倍,同时降低逻辑资源占用率。

2. 接口与时钟管理模块

外部存储器控制器作为连接片外存储的“桥梁”,支持SDRAM、DDR等主流存储器接口,通过硬件逻辑优化数据读写时序,解决FPGA与外部存储器的速率匹配问题。例如在视频处理系统中,控制器可实现每秒数GB的图像数据吞吐,确保高清视频流的实时缓存与回放。

PLL(相位锁定环)是时钟系统的“稳频器”,通过对比输入时钟与反馈时钟的相位差,动态调整输出频率,生成FPGA内部各模块所需的同步时钟。其关键参数包括频率范围(如10MHz-1.5GHz)、抖动指标(通常低于100fs)和倍频/分频系数,可通过配置工具精确调整,确保高速电路中各模块的时序协同。

SerDes(收发器)作为高速数据传输的“高速公路”,支持千兆以太网、光纤通道等协议,通过串并转换(Serializer/Deserializer)实现单通道10Gbps以上的传输速率。其内部集成均衡器、时钟恢复电路和纠错模块,可补偿高速信号传输中的衰减与噪声,是数据中心、通信设备中长距离高速互联的核心组件。

三、FPGA与ASIC的技术特性对比

1. 灵活性与开发周期差异

FPGA的核心优势在于全生命周期的可编程性,用户可通过更新配置文件动态修改硬件逻辑,即使设备已部署到终端场景,仍能远程升级功能或修复漏洞。例如某通信设备厂商通过FPGA实现5G协议栈,可在标准迭代后通过远程配置升级支持新频段,无需更换硬件。相比之下,ASIC(专用集成电路)的逻辑功能在流片后永久固定,设计缺陷只能通过重新制造掩膜解决,成本极高(单次流片费用可达百万美元级)。

开发周期方面,FPGA基于软件定义硬件,省去ASIC的物理设计(布局布线、时序签核)和制造流程,开发周期可缩短至ASIC的1/3-1/2。以雷达信号处理系统为例,FPGA原型验证可在3个月内完成,而同等复杂度的ASIC开发需12-18个月,包括RTL验证、物理实现和晶圆代工等环节。这种快速迭代能力使FPGA成为新技术验证和小批量产品的首选方案。

2. 成本效益的规模依赖性

成本层面,FPGA与ASIC呈现“规模敏感”的差异化优势。FPGA初始投入低,无需支付ASIC的一次性工程费用(NRE,包括掩膜、工具授权等),适合研发阶段和小批量生产(年产量低于10万片场景)。以某工业控制器为例,FPGA方案开发成本约50万元,而ASIC的NRE费用超过500万元,仅当产量超过100万片时,ASIC的单片成本(约10美元)才低于FPGA(约30美元)。

长期成本方面,ASIC通过硬件架构深度优化实现更低功耗(同等功能下功耗仅为FPGA的1/5-1/10),适合大规模部署场景(如智能手机SoC)。而FPGA因可编程布线资源和冗余逻辑,功耗与面积效率较低,更适合对成本不敏感但需快速迭代的场景(如科研设备、军工系统)。

四、FPGA的典型应用领域

1. 通信与信号处理

在通信领域,FPGA是高速协议实现的“万能平台”。5G基站中,FPGA用于物理层(PHY)处理,通过并行逻辑实现OFDM调制解调、信道编码(LDPC/Polar码)和波束赋形,支持100MHz带宽下的4096QAM高阶调制;数据中心中,FPGA部署于SmartNIC(智能网卡),卸载CPU的TCP/IP校验和计算、VXLAN隧道封装等任务,单卡吞吐量提升至100Gbps以上,降低服务器CPU占用率30%。

雷达与声呐信号处理中,FPGA的实时并行性优势显著。某机载雷达系统通过FPGA实现脉冲压缩、动目标检测(MTD)算法,在1ms内完成1024点FFT运算,距离分辨率达1米,同时跟踪50个目标,处理延迟比GPU方案降低60%。

2. 人工智能与自动驾驶

AI加速领域,FPGA凭借低延迟特性成为边缘计算的理想选择。在自动驾驶感知系统中,FPGA部署轻量化神经网络(如MobileNet),对摄像头、激光雷达数据进行实时处理,目标检测延迟控制在5ms以内,满足车辆决策的实时性要求(行业安全标准通常要求<100ms)。相比GPU,FPGA功耗降低70%,适合车载嵌入式环境。

工业AI质检场景中,FPGA与机器视觉传感器直连,通过硬件加速实现图像预处理(降噪、边缘检测)和特征提取,检测速率达1000帧/秒,错误率低于0.1%,同时支持产线切换时的算法快速重配置,适应不同产品的质检需求。

3. 工业控制与嵌入式系统

工业控制领域,FPGA的高可靠性和实时性使其成为核心控制器。在高端数控机床中,FPGA实现伺服电机的位置环控制,脉冲频率达1MHz,定位精度±0.1μm,同时通过EtherCAT协议与其他设备通信,周期刷新时间<100μs;新能源逆变器中,FPGA完成并网电流的PID调节和谐波抑制,响应时间<1ms,满足电网对电能质量的严格要求(THD<5%)。

嵌入式系统中,FPGA的异构计算能力被广泛利用。某便携式频谱分析仪通过FPGA实现信号采集(1GSPS采样率)、FFT分析和数据显示的一体化设计,整机功耗<15W,重量<2kg,相比传统基于PC的方案体积缩小80%,适合野外作业。

五、FPGA的开发工具与编程语言

1. 硬件描述语言(HDL)的特性对比

FPGA设计依赖硬件描述语言(HDL)定义逻辑功能,主流语言包括VHDL和Verilog。VHDL采用结构化设计思想,语法严谨,支持从系统级到门级的多层次描述,适合大规模团队协作和复杂系统建模。其强类型特性减少语法错误,标准化程度高(IEEE 1076标准),在航空航天、军工等对可靠性要求极高的领域应用广泛。

Verilog语法接近C语言,简洁灵活,支持行为级、数据流级和门级描述,适合快速原型开发。例如实现一个4位加法器,Verilog可通过assign语句直接描述组合逻辑(assign sum = a + b;),而VHDL需定义实体、结构体等更多模板代码。这种易用性使Verilog成为高校教学和中小规模设计的首选语言,目前约70%的FPGA项目采用Verilog开发。

2. 主流开发工具的流程与功能

FPGA开发工具提供从代码编写到硬件配置的全流程支持,Xilinx Vivado和Intel Quartus是行业主流平台。其核心流程包括:设计输入(HDL代码或图形化 schematic)、综合(将HDL转换为门级网表)、实现(布局布线,优化时序与资源)、生成比特流(配置文件)和下载验证。

Vivado针对高端FPGA(如UltraScale系列)优化,集成HLS(高层次综合)工具,支持C/C++代码直接转换为硬件逻辑,降低开发门槛;Quartus则以易用性著称,内置IP核库(如FFT、PCIe控制器)可直接调用,缩短开发周期。此外,第三方工具如ModelSim用于HDL仿真,Synplify Pro提供跨厂商综合支持,形成完整的设计生态。

六、FPGA技术的优势与挑战

1. 核心优势:灵活性与并行性能

FPGA的核心竞争力在于“可编程的并行硬件”,其优势体现在三方面:一是逻辑重构能力,同一硬件平台可适配不同算法(如从通信协议处理切换为AI推理),硬件利用率提升3-5倍;二是并行处理效率,通过空间并行架构( thousands of independent logic units)实现任务级并行,例如同时处理1000路信号的滤波运算,性能远超同功耗CPU的串行执行;三是低延迟特性,硬件逻辑直接映射算法,避免操作系统调度和指令流水线延迟,端到端处理延迟可低至纳秒级。

2. 现存挑战与技术突破方向

当前FPGA发展面临三大挑战:功耗控制、开发复杂度和成本优化。功耗方面,可编程互连资源和冗余逻辑导致FPGA功耗密度较高(约50-100mW/mm²),为解决这一问题,厂商推出异构架构(如Xilinx Zynq系列集成ARM处理器+FPGA逻辑),将控制类任务交给CPU,FPGA专注并行运算,整体功耗降低40%;开发复杂度方面,HLS工具通过自动代码转换缩短设计周期,但生成逻辑的资源利用率仍比手动优化低20-30%,需结合RTL级优化提升效率;成本方面,3D堆叠技术(如Intel Stratix 10采用EMIB封装集成高带宽存储器)在不增加芯片面积的前提下提升存储容量,单位功能成本降低30%。

未来,随着AI、5G等需求驱动,FPGA将向“软件定义硬件”方向演进:通过预集成AI加速引擎(如Xilinx AI Engine)、高速接口(如PCIe 6.0、CXL)和开发框架(如TensorFlow Lite for FPGA),进一步降低使用门槛,推动其在边缘计算、智能汽车等新兴领域的普及。

七、总结与展望

FPGA作为可编程硬件平台,通过“通用逻辑+专用硬核”的架构平衡灵活性与性能,在通信、AI、工业等领域发挥不可替代的作用。其核心价值在于缩短开发周期、支持动态升级和适应小批量场景,同时通过持续的架构创新(如3D堆叠、异构集成)和工具链优化(如HLS、AI模型自动映射),不断突破功耗、成本和开发复杂度的限制。

未来,随着芯片制程逼近物理极限,FPGA的“可编程性”将成为硬件创新的关键载体:在边缘智能领域,FPGA将作为AI算法的“试验田”,支持快速迭代与部署;在数据中心,FPGA通过SmartNIC、DPU等形态卸载CPU任务,提升算力效率;在工业4.0中,FPGA的实时控制能力将推动柔性制造的普及。可以预见,FPGA将与CPU、GPU、ASIC共同构成异构计算的核心支柱,为数字社会的智能化转型提供硬件基石。