一、FPGA基础概念与技术特点

1. 基本定义与发展历程

FPGA(Field-Programmable Gate Array,现场可编程门阵列)是在PAL、GAL、CPLD等可编程器件基础上发展的半定制集成电路,作为专用集成电路(ASIC)领域的灵活解决方案,既解决了定制电路开发周期长、成本高的问题,又克服了早期可编程器件门电路数量有限的缺点。其核心特性是允许用户通过编程定义内部逻辑模块和输入/输出(I/O)模块功能,实现从通用硬件到专用电路的现场重构。自20世纪80年代问世以来,FPGA经历了逻辑单元规模从数千门到数千万门的增长,集成资源从单纯逻辑单元扩展到存储、计算、高速接口等异构组件,已成为数字系统设计中不可或缺的核心器件。

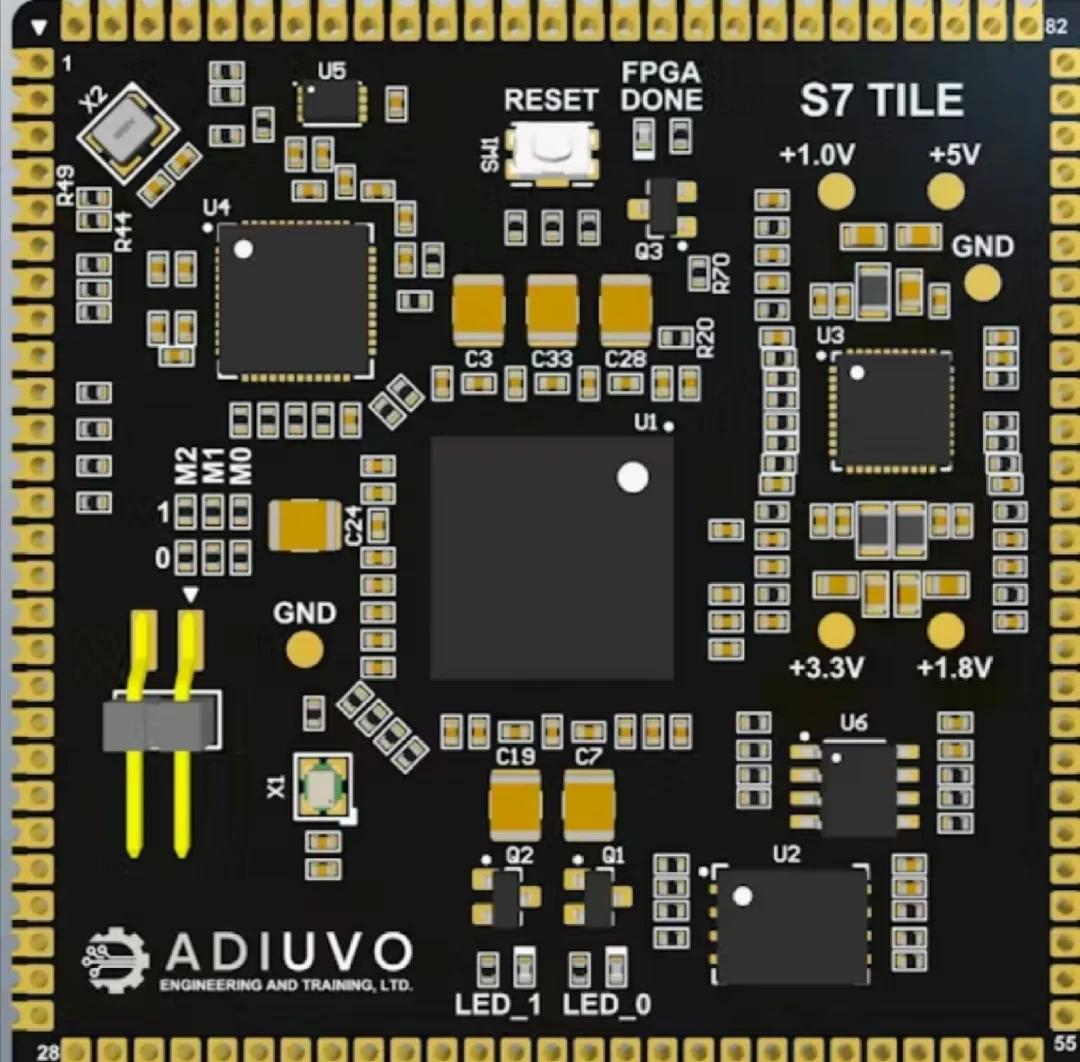

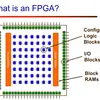

2. 核心结构组成

FPGA的硬件架构由五大关键部分构成。可编程逻辑单元(如CLB,可配置逻辑块)是基础逻辑单元,内部包含查找表(LUT)和触发器,可灵活配置为组合逻辑(如与门、或门)或时序逻辑(如计数器、寄存器),支持位宽自定义的数据处理。可编程输入/输出接口(IOB)负责连接外部设备,支持TTL、CMOS、LVDS等多种电平标准,可根据应用需求配置为输入、输出或双向模式。可编程内部互联结构通过开关矩阵和布线资源实现逻辑单元与I/O模块间的信号传输,确保电路模块间的灵活连接。块随机访问存储器(BRAM)作为片上存储资源,用于数据缓存和临时存储,典型容量从几KB到数百MB不等。时钟管理模块(CMM)提供稳定的时钟信号,支持相位调整和频率合成,满足高速电路对时序同步的要求。

3. 技术特点总结

FPGA的核心优势体现在三大方面。硬件可重构性是其最显著特征,用户可通过加载不同配置文件(Bitstream)实时修改电路功能,无需更换硬件,适用于快速原型验证和多场景复用。并行处理能力基于其分布式架构,多个逻辑单元可独立工作,支持数万级并行数据通路,例如在图像处理中可同时执行边缘检测、色彩转换等任务,处理效率远超串行执行的处理器。集成硬核资源提升特定场景性能,如DSP切片(用于高速乘法累加运算)、高速收发器(支持10G/25Gbps数据传输)、PCIe接口等,在保持灵活性的同时满足高端应用需求。此外,FPGA还具有低延迟特性,硬件逻辑直接执行,无需指令译码环节,响应时间可达纳秒级,适合实时控制系统。

二、FPGA工作原理与开发流程

1. 架构原理:从通用硬件到专用电路

FPGA的工作机制类似于“硬件乐高”,通过配置文件定义内部资源的连接关系,将通用可编程架构转换为专用数字电路。上电后,FPGA从外部存储器(如Flash)加载配置文件,该文件包含逻辑单元的功能定义、互联路径的开关状态以及I/O接口的电平配置。配置完成后,逻辑单元按预设电路结构协同工作,例如在数字时钟设计中,CLB被配置为计数器模块,通过预设频率实现秒、分、小时的时序逻辑;IOB配置为输出接口,驱动数码管显示时间;内部互联则确保时钟信号和计数数据在模块间准确传输。这种“配置即电路”的特性,使FPGA能够像ASIC一样高效工作,同时保留现场修改的灵活性。

2. HDL编程机制:硬件描述与软件编程的差异

FPGA通过硬件描述语言(HDL)如Verilog或VHDL实现电路设计,其编程范式与传统软件存在本质区别。HDL描述的是电路的结构或行为,而非指令执行流程。例如,实现一个与门功能,Verilog代码直接描述输入与输出的硬件连接关系(“assign y = a & b;”),编译后生成的配置文件定义了逻辑单元中查找表的存储内容(如LUT存储与门的真值表);而单片机的C语言代码(“y = a & b;”)则是通过CPU指令计算结果,需经历取指、译码、执行等串行步骤。HDL编程需关注信号时序、逻辑延迟等硬件特性,例如在高频电路中需约束关键路径的延迟,避免信号竞争;而软件编程更关注算法流程和数据结构。

3. 开发流程与工具链

FPGA开发遵循标准化流程:需求分析阶段明确功能与性能指标,如数据处理带宽、延迟要求;设计输入阶段通过HDL代码或图形化工具描述电路,可复用IP核(如FFT、PCIe控制器)加速开发;功能仿真使用ModelSim等工具验证逻辑正确性,通过Testbench生成激励信号,观察输出是否符合预期;综合阶段由EDA工具(如Vivado、Quartus)将HDL代码转换为门级网表,优化逻辑资源分配;布局布线阶段确定逻辑单元和互联路径的物理位置,需满足时序约束(如最大工作频率);配置阶段生成Bitstream文件,通过JTAG或SPI接口下载到FPGA,完成硬件电路构建。主流工具链如Xilinx Vivado支持从设计到验证的全流程,集成HLS(高层次综合)工具可将C/C++代码转换为硬件逻辑,降低开发门槛。

三、FPGA典型应用领域

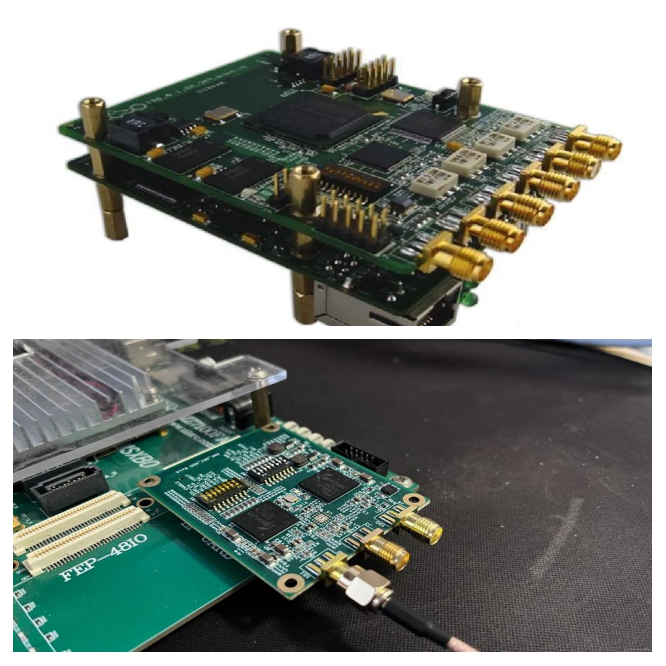

1. 数字信号处理与通信系统

FPGA在数字信号处理领域的优势在于并行运算能力和低延迟。在5G基站中,FPGA负责物理层信号处理,包括信道编码/解码、调制解调(如OFDM)和大规模MIMO(多输入多输出)数据处理——5G需支持的信道数量是4G的10倍以上,FPGA通过并行处理架构满足每秒数百兆比特的数据吞吐量。在雷达系统中,FPGA实现回波信号的实时滤波和目标检测,其高速乘法器(如Altera Stratix 10 FPGA的DSP模块运算速度达1.5GHz)可快速完成傅里叶变换,确保目标定位延迟小于1微秒。此外,FPGA还用于软件定义无线电(SDR),通过动态重构支持多频段、多协议通信,适配不同的无线标准(如Wi-Fi、蓝牙)。

2. 图像处理与人工智能加速

FPGA在图像处理中适用于高分辨率、实时性要求高的场景。自动驾驶系统中,FPGA对摄像头采集的1080P@60fps视频流进行实时分割,识别行人、车辆、交通标志等对象,处理延迟需控制在20毫秒以内以满足安全要求——某基于FPGA的图像分割方案通过并行执行卷积运算,较GPU能效比提升3倍。医疗设备如便携式超声仪,FPGA实现超声回波信号的波束合成和图像重建,支持动态聚焦和滤波参数调整,提升成像清晰度。在安防监控中,FPGA支持多通道视频编解码(如H.265)和智能分析(如异常行为检测),单芯片可处理16路1080P视频流,且功耗低于传统服务器方案。

3. 工业控制与嵌入式系统

工业自动化领域,FPGA的高可靠性和实时性使其成为关键控制单元。工业机器人控制器中,FPGA实现运动控制算法(如PID调节),控制周期可达100微秒,确保机械臂定位精度达0.01毫米;同时集成EtherCAT等工业总线接口,支持与传感器、执行器的高速通信。在智能电网中,FPGA用于电力信号采集与分析,实时监测电压、电流波形,快速识别故障并触发保护机制,响应时间小于1毫秒。消费电子领域,“FPGA+GPU”异构平台(如Z19-M开发板)支持多通道视频处理,应用于AR眼镜的实时环境建模,通过动态重构实现功能复用,降低硬件成本。

四、FPGA与单片机的核心差异分析

1. 架构与工作方式对比

FPGA采用无固定CPU的并行架构,由大量可编程逻辑单元、互联资源和I/O模块组成,工作时通过硬件配置实现专用电路功能,所有逻辑单元并行执行,无指令执行延迟。例如,一个FPGA可同时运行数据采集、信号处理、通信传输三个独立电路模块,模块间通过内部连线直接传输数据。单片机基于冯·诺依曼或哈佛架构,集成固定CPU核心、片内存储器和外设接口,工作时通过CPU逐条执行存储在Flash中的指令,实现控制逻辑。例如,8051单片机执行加法运算需经历取指(从Flash读取指令)、译码(解析指令含义)、执行(运算器计算)三个串行步骤,同一时刻只能处理一个任务(多任务需通过RTOS切换实现伪并行)。

2. 可编程性与开发模式差异

FPGA的可编程性体现在硬件逻辑层面,通过HDL描述电路结构或行为,编译后生成配置文件定义硬件连接,支持无限次擦写重构。开发需经历逻辑设计、时序分析、物理实现等硬件开发流程,入门门槛较高,但灵活性极强,可实现任意数字电路功能。单片机的可编程性局限于软件指令层面,通过C语言或汇编语言编写顺序执行的程序,编译为机器码存储在Flash中,CPU按地址顺序读取执行。开发流程接近传统软件开发,需关注算法逻辑和外设驱动,入门简单,但硬件功能固定,无法修改CPU架构或外设接口。

3. 性能与成本对比

性能方面,FPGA在并行处理和速度上优势显著,逻辑单元数量直接决定并行能力(如Xilinx Artix-7 XC7A35T含5200个逻辑单元,支持数万级并行数据通路),典型运算速度达ns级,DSP模块可实现1.5GHz乘法运算。单片机性能受CPU主频限制,8位机主频通常低于40MHz,32位机(如STM32)可达200MHz,单指令周期运算能力约10-200MIPS,串行处理效率远低于FPGA。成本方面,FPGA芯片价格较高(入门级约50元,高端型号超万元),开发工具多为厂商专用(如Vivado需付费授权),适合小批量、高性能场景。单片机成本低廉(8位机约1-10元,32位机约10-50元),开发工具开源普及(如Keil、IAR),适合大规模量产的低成本应用。

4. 应用场景选择对比表

| 对比维度 | FPGA | 单片机 |

| 核心优势 | 高速并行处理、硬件可重构、低延迟 | 低成本、低功耗、开发简单 |

| 典型性能指标 | 逻辑单元数:千-千万级;速度:ns级 | 主频:MHz级;运算能力:MIPS级 |

| 开发复杂度 | 高(需硬件知识) | 低(软件思维为主) |

| 成本范围 | 中高(芯片+工具) | 低(芯片+开源工具) |

| 代表应用 | 5G基站、自动驾驶、雷达 | 家电控制、传感器节点、智能仪表 |

| 适用场景特征 | 高实时性、高复杂度、多标准适配 | 低功耗、低速率、功能固定 |

五、应用场景选择标准与技术趋势

1. 场景需求驱动的选择依据

选择FPGA或单片机需基于应用场景的核心需求。当应用要求高速并行处理(如1Gbps以上数据率)、实时响应(延迟<100μs)或多标准适配(如通信协议动态切换)时,FPGA是最优选择,例如5G基站的物理层处理需同时支持多种频段和调制方式,FPGA的硬件可重构特性可降低设备成本。当应用为低复杂度控制(如灯光定时、传感器数据采集)、低功耗(如电池供电设备)或大规模量产(如家电控制器,年产量超100万件)时,单片机更具优势,例如智能水杯的温度检测与显示功能,通过8位单片机即可实现,成本仅需几元。此外,开发周期和团队技能也需考虑:FPGA开发周期较长(3-6个月),适合技术预研;单片机开发周期短(1-2个月),适合快速产品落地。

2. FPGA技术发展趋势

当前FPGA技术呈现三大发展方向。架构创新方面,高端产品集成异构计算资源,如高带宽内存(HBM,带宽达400GB/s)、AI加速引擎(如Xilinx Versal的AI Core)和光互联接口,满足云计算和AI推理的大数据处理需求。工艺制程持续进步,主流厂商已推出7nm工艺FPGA,5nm产品进入研发阶段,逻辑密度较16nm工艺提升2倍,功耗降低40%。应用领域不断扩展,在边缘计算中,FPGA凭借低功耗和实时性优势,成为AI推理的关键加速器件(如微软Azure Sphere使用FPGA实现设备安全监测);在汽车电子中,车规级FPGA(如Intel Agilex)支持ISO 26262功能安全标准,应用于自动驾驶的传感器融合和决策控制。此外,国产化FPGA快速崛起,在工业控制、通信设备等领域实现替代,推动产业链自主可控。

通过上述分析可见,FPGA与单片机并非替代关系,而是针对不同场景的互补技术。FPGA以其硬件可编程性和并行处理能力,在高端数字系统中发挥不可替代的作用;单片机则以低成本和易用性,在嵌入式控制领域占据主导地位。随着技术的发展,两者的边界逐渐模糊(如集成CPU的FPGA SoC和集成FPGA模块的单片机),但核心特性差异仍将长期存在,共同推动嵌入式技术的多元化发展。

二牛学FPGA