2025年,正值首款商用FPGA(现场可编程门阵列)诞生40周年。这项技术虽不如CPU、GPU广为人知,却以其独特的“硬件可编程”特性,彻底改变了半导体设计与应用的格局,成为支撑通信、AI、自动驾驶等前沿领域的关键技术。以下从起源、技术优势、应用场景(含未来十年新方向)及国产厂商突破难点展开解析。

一、起源与40年技术跃迁:从“小众验证工具”到“智能加速核心”

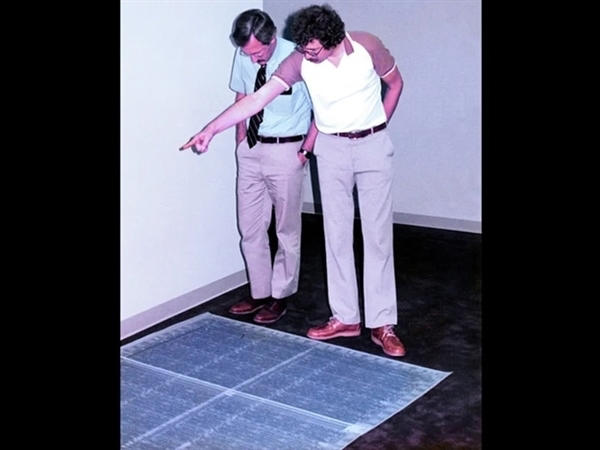

1985年,赛灵思(Xilinx)推出全球首款商用FPGA芯片XC2064(由联合创始人Ross Freeman发明),仅含64个逻辑块、8.5万个晶体管,却开创了“硬件如软件般灵活”的新范式——开发者可通过编程动态重构硬件功能,无需重新设计芯片。这一突破解决了ASIC(专用集成电路)开发周期长、成本高的痛点,最初主要用于芯片原型验证和小规模生产。

40年技术演进可分为三个阶段:

1985-2000年:基础架构确立期

早期FPGA以SRAM编程技术为主,集成嵌入式存储块和时钟管理模块,逐步应用于通信、军事等领域(如Xilinx XC4000系列)。

2000-2015年:系统级集成期

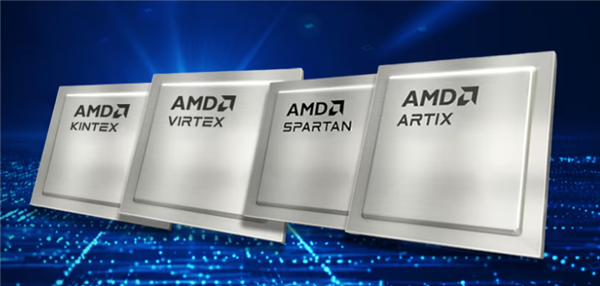

FPGA向SoC(片上系统)演进,集成硬核处理器(如ARM)、高速串行接口(PCIe、10G以太网)和DSP模块,成为视频处理、无线通信的核心平台(如Xilinx Virtex系列)。

2015年至今:智能加速时代

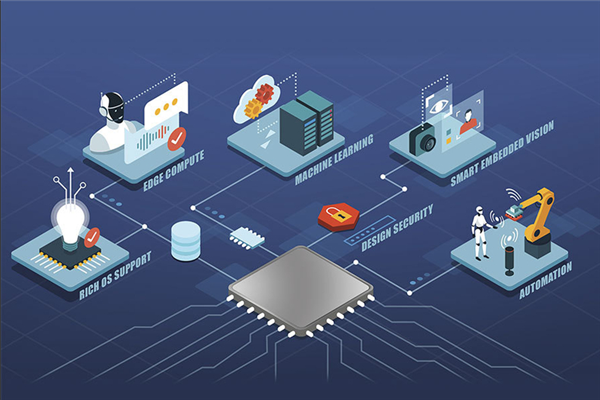

随着AI和云计算兴起,FPGA集成AI引擎(如AMD Versal系列的AI Core)、采用2.5D/3D先进封装,并支持高层次综合(HLS)开发,成为边缘计算、数据中心加速的优选方案。

目前,FPGA的晶体管数量已从8.5万跃升至1380亿,逻辑单元从64个增长至1850万个,覆盖从消费电子到航天的全场景。

二、技术核心优势:灵活、高效、低延迟的“硬件积木”

FPGA的核心竞争力在于其**“可编程”与“并行计算”的双重特性**,与CPU、GPU、ASIC形成差异化互补:

灵活性:可动态重编程硬件逻辑,适应算法迭代(如AI模型更新),开发周期仅需数周,远短于ASIC的数月甚至数年。

低延迟:硬件级并行计算,无指令译码和共享内存开销,延迟可低至微秒级(如高频交易、自动驾驶传感器数据处理)。

高能效:针对特定任务定制硬件架构,能效比(性能/功耗)远超CPU、GPU。例如,处理AI推理时,FPGA的功耗仅为GPU的1/4~1/10。

可扩展性:支持多芯粒整合(Chiplets)和异构计算,兼容CPU、GPU生态,成为“软件定义硬件”的核心载体。

对比其他芯片:

CPU:通用计算,擅长串行任务,但并行能力弱、延迟高。

GPU:强并行计算,适合AI训练,但固定架构难以适配快速迭代的算法。

ASIC:专用优化,能效最高,但开发成本高、灵活性差(一旦流片无法修改)。

FPGA则在“灵活性”与“能效”间取得平衡,尤其在实时性要求高、算法快速迭代的场景(如边缘AI、5G基站)中不可替代。

三、应用场景:从通信到AI,覆盖当前与未来的“数字世界”

凭借上述优势,FPGA已渗透至通信、数据中心、AI等核心领域,并在未来十年向更多新兴场景延伸:

当前主流应用场景

通信领域:5G基站的基带处理(如信道编解码、同步算法)、光通信的高速接口(100G/400G以太网),利用FPGA的高并行和低延迟特性实现线速处理。

数据中心:加速搜索排序、加密解密、数据库查询等任务。微软曾用FPGA加速Bing搜索,延迟从毫秒级降至微秒级;百度用FPGA优化AI推理,效率提升3倍。

AI与边缘计算:边缘端(如摄像头、工业传感器)的实时AI推理(如图像识别、语音处理)。AMD Versal系列FPGA集成AI引擎,支持端到端低延迟处理,被NASA火星探测器、斯巴鲁ADAS系统采用。

汽车电子:智能座舱的多屏互连(支持不同分辨率屏幕的统一控制)、ADAS的传感器数据融合(如激光雷达、摄像头的实时处理)。莱迪思(Lattice)的低功耗FPGA被用于车载显示的区域调光,提升对比度并降低能耗。

工业与航天:工业机器人的多轴控制、卫星的星载计算(如NASA用FPGA过滤火星图像数据),依赖其高可靠性和抗辐射能力。

未来十年新应用场景

边缘AI与实时推理:边缘计算对低延迟、本地化AI推理的需求激增,FPGA可动态重构硬件逻辑适配AI模型快速迭代(如小语言模型、多模态模型),在自动驾驶传感器数据融合、工业机器人实时决策、物联网设备端智能分析等场景中,实现微秒级延迟处理,能效比远超GPU。预计到2034年,边缘AI市场规模将突破1430亿美元。

智能驾驶新基建:L4级以上自动驾驶对传感器数据(激光雷达、摄像头)的实时处理需求极高,单辆L4车需搭载12-16片FPGA,用于动态算法切换(如毫秒级适应复杂路况),提升ADAS系统的响应速度和安全性。

6G通信与软件无线电:6G对高频段(毫米波)、Massive MIMO波束成形等技术的需求,要求硬件支持全频段覆盖和低时延处理。FPGA的软件无线电(SDR)特性可实现Sub-6GHz/毫米波全频段适配,波束成形时延缩短至3μs,成为6G基站基带处理的核心组件。

工业4.0神经中枢:工业自动化向智能化升级,FPGA在机器视觉(支持120fps高速图像处理)、预测性维护(准确率提升至99.2%)、多轴电机控制(单芯片控制百台设备)等场景中优势显著,成为“智能工厂”的核心计算单元。

四、“不为人知”的原因与国产厂商的技术突围难点

FPGA的“低调”源于其专业性和幕后属性:技术门槛高(需掌握硬件描述语言和底层电路设计)、应用场景隐蔽(嵌入通信设备、数据中心等“幕后”硬件)、市场集中度高(全球90%以上份额由AMD、Intel、Lattice垄断)。

尽管国产FPGA在中小容量市场(如28nm)已实现部分替代,但高端市场仍面临多重挑战:

工艺与规模差距:国际巨头已量产7nm/5nm工艺的超大规模FPGA(逻辑单元超1000万),而国产FPGA多数停留在28nm工艺,16nm技术尚未大规模突破,性能与容量存在代际差距。

专利壁垒与架构创新:Xilinx、Intel等拥有超6000项核心专利(覆盖逻辑单元架构、高速接口IP等),国产厂商需通过差异化设计(如异构计算、Chiplet封装)规避专利限制,但自主架构创新难度大。

EDA工具与生态短板:国际厂商的EDA工具(如Xilinx Vivado)支持高层次综合(HLS)和AI优化,而国产EDA工具在时序收敛、IP丰富度上仍需突破,生态链(开发板、参考设计)不完善。

高容量FPGA研发挑战:500K逻辑单元以上的高容量FPGA需集成硬核CPU、高速SerDes(100Gbps+)、AI引擎等模块,对硬件架构设计、多模块协同验证能力要求极高。

资金与人才瓶颈:FPGA研发周期长(5-7年)、流片成本高(单次超亿元),且需持续投入软件迭代和生态建设。国内企业融资规模有限,高端设计人才稀缺。

结语:AI时代的“第二春”与国产突围机遇

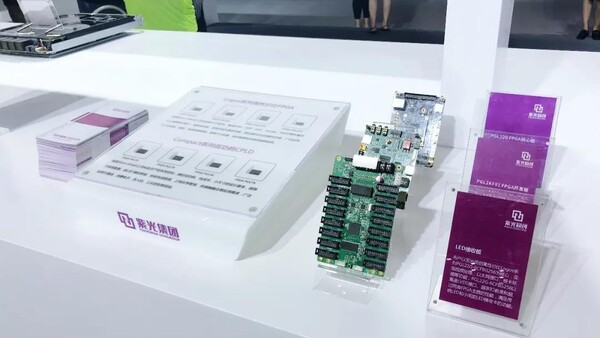

40年来,FPGA从“芯片验证工具”成长为“智能计算核心”,其“硬件可编程”的特性在AI、边缘计算、6G等新兴领域持续释放价值。随着AMD、Intel等巨头加速整合FPGA与GPU/CPU生态,以及国产厂商(如紫光同创、安路科技)在细分场景(如边缘AI、工业控制)的技术突破,FPGA或将在未来十年进一步渗透至更多“智能终端”,成为数字经济时代的“万能硬件引擎”。