写在前面

HDMI接口很早之前就想调试了,由于没有时间,就拖到了现在,而且毕业设计也是和视频处理系统有关,就趁这个机会把这个接口调试下。

开发环境

vivado 18.3

pynq - z2

HDMI简介

高清晰度多媒体接口(英文:High Definition Multimedia Interface,HDMI)是一种数字化视频/音频接口技术,是适合影像传输的专用型数字化接口,其可同时传送音频和影像信号,最高数据传输速度为2.25GB/s,同时无需在信号传送前进行数/模或者模/数转换。

HDMI接口设计说明

HDMI输出驱动接口在FPGA方面应用时,主要有两种方式:

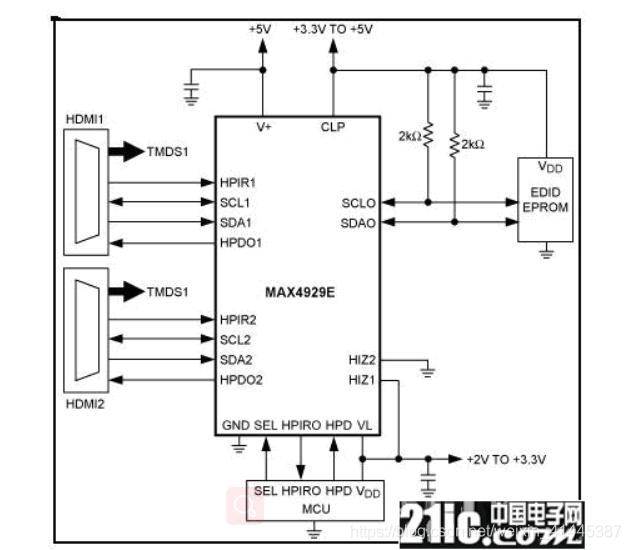

一种是采用HDMI( DVI)编码芯片。这种操作只需要对对应芯片进行操作配置即可实现功能。

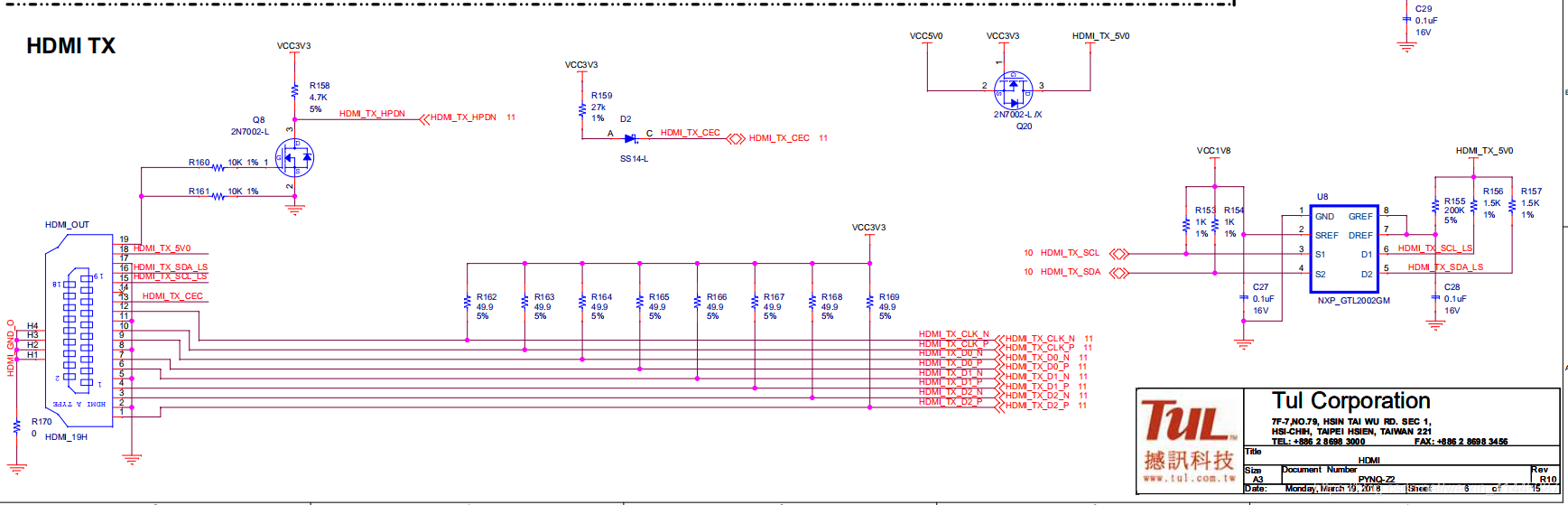

另外一种方式就是使用FPGA进行编写,由 IO 模拟方式实现。这里贴出我所使用的pynq-z2的对应模块的电路图并给出板子对应的信号引脚分配信息。

set_property -dict { PACKAGE_PIN L17 IOSTANDARD TMDS_33 } [get_ports { TMDS_Clk_n }]; #IO_L11N_T1_SRCC_35 Sch=hdmi_tx_clk_n

set_property -dict { PACKAGE_PIN L16 IOSTANDARD TMDS_33 } [get_ports { TMDS_Clk_p }]; #IO_L11P_T1_SRCC_35 Sch=hdmi_tx_clk_p

set_property -dict { PACKAGE_PIN K18 IOSTANDARD TMDS_33 } [get_ports { TMDS_Data_n[0] }]; #IO_L12N_T1_MRCC_35 Sch=hdmi_tx_d_n[0]

set_property -dict { PACKAGE_PIN K17 IOSTANDARD TMDS_33 } [get_ports { TMDS_Data_p[0] }]; #IO_L12P_T1_MRCC_35 Sch=hdmi_tx_d_p[0]

set_property -dict { PACKAGE_PIN J19 IOSTANDARD TMDS_33 } [get_ports { TMDS_Data_n[1] }]; #IO_L10N_T1_AD11N_35 Sch=hdmi_tx_d_n[1]

set_property -dict { PACKAGE_PIN K19 IOSTANDARD TMDS_33 } [get_ports { TMDS_Data_p[1] }]; #IO_L10P_T1_AD11P_35 Sch=hdmi_tx_d_p[1]

set_property -dict { PACKAGE_PIN H18 IOSTANDARD TMDS_33 } [get_ports { TMDS_Data_n[2] }]; #IO_L14N_T2_AD4N_SRCC_35 Sch=hdmi_tx_d_n[2]

set_property -dict { PACKAGE_PIN J18 IOSTANDARD TMDS_33 } [get_ports { TMDS_Data_p[2] }]; #IO_L14P_T2_AD4P_SRCC_35 Sch=hdmi_tx_d_p[2]

set_property -dict { PACKAGE_PIN R19 IOSTANDARD LVCMOS33 } [get_ports { HDMI_OEN[0] }]; #IO_0_34 Sch=hdmi_tx_hpdn

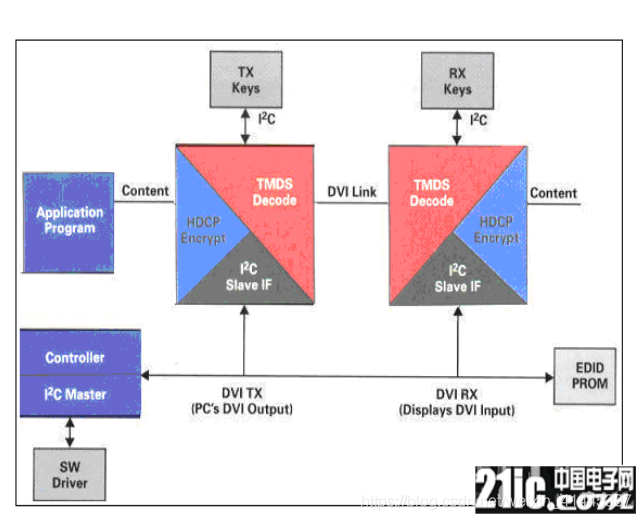

HDMI和DVI(Digital Visual Interface)数字视频接口这两种数字视频传输标准的要求几乎完全相同,并同时处理一组高频和低频信号。这两种标准均采用TMDS(最小跳变差分信号又称最小化传输差分信号)技术来传输数据的高频(视频)部分。

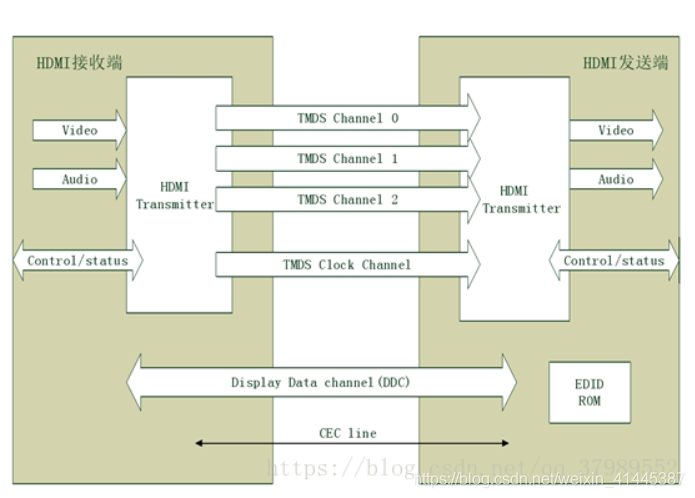

HDMI/DVI数字视频接口的设计思想采用了DVI用于至数字显示器的高速数字连接。DVI采用了TMDS技术来传输数据的高频(视频)信号(见图1红色块所示)。

要实现HDMI和DVI系统中的“即插即用”功能,源端(通常是一台电脑、DVD播放器或游戏机)和接收端(通常是监视器或接收机)必须连接起来。HDMI 和DVI借用VESA (视频电子标准协会)的开放标准,采用DDC(数字显示通道)、一个称为HPD的新信号(热插拔检测)

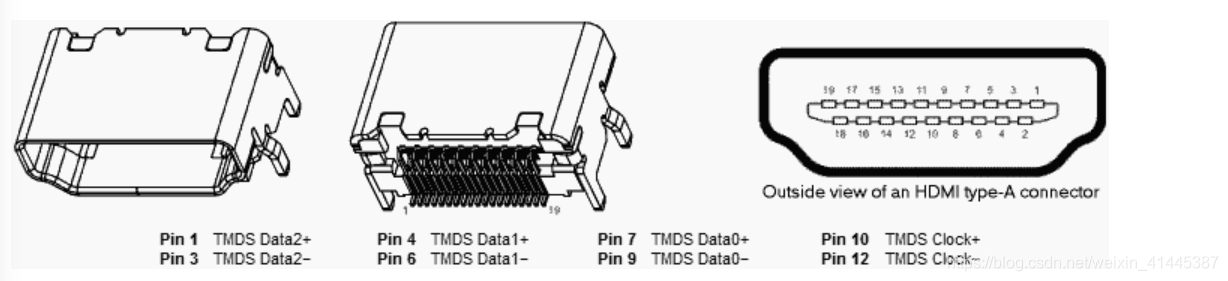

标准HDMI接口

TYPE A,包括19个PIN,主要是4对差分信号线

| TMDS clock+ | TMDS clock- |

| TMDS data0+ | TMDS data0- |

| TMDS data1+ | TMDS data1- |

| TMDS data2+ | TMDS data2- |

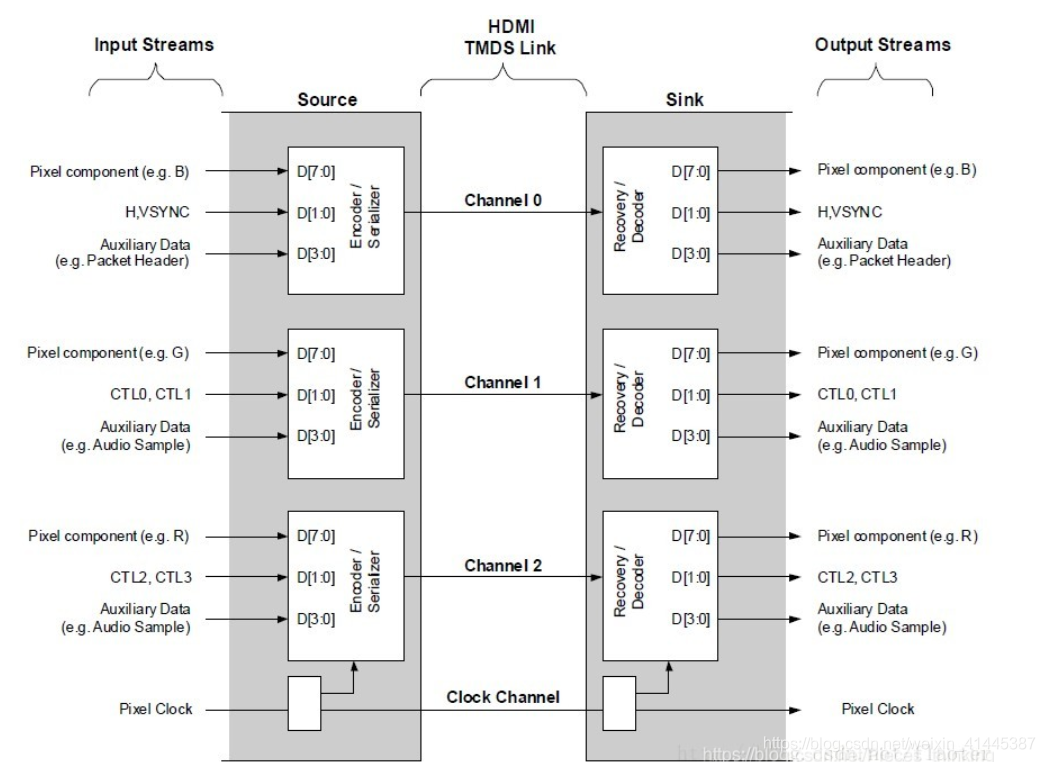

TMDS(最小跳变差分信号)

最小化传输差分信号(TMDS)作为电气电平的标准。被应用于发送数字视频接口(DVl)及高清晰度多媒体接口(HDMl)的数据。其设计考虑因素之包括:

对内偏斜(Intra-Pai rSkew)。在给定的一对差分信号上,真(true)信号及其互补信号之间的时间差应尽可能的小;

残余抖动(Residual Jitter)。测试点与信号源之间所测量到的抖动数量的差异。可接受的最大残余抖动等价于发射机与接收机之间最小的抖动预计量(budget);

静电放电(ESD)。外部连接器因曝露于外界,因而更易受到静电放电的影响。更高的静电放电率可提供更良好的保护。

TMDS 包括3个RGB数据和1个时钟,共计4个通道(称为1个TMDS连接或Single-link)的传输回路。TMDS是把8位的RGB视频数据变换成10 位转换最小化、DC平衡的数据,再完成数据的串行处理;接收端设备对串行数据解串行变成并行数据,再转换成8位视频信号。因此,传输数字RGB数据需要3 个转换最小化差分采样信号构成一个TMDS连接。

HDMI系统框图

HDMI传输由三组TMDS通道和一组TMDS clock通道组成,TMDS clock的运行频率是video信号的pixel频率,在每个cycle,每个TMDS data通道发送10bit数据。

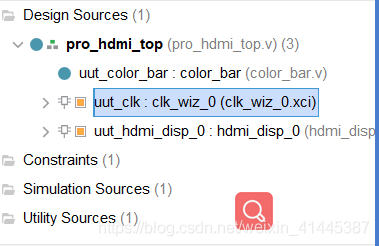

项目设计

整体的项目结构(因为也只是验证别人写好的程序为后续的毕设做准备,就没有直接移植的别人写好的程序):

hdmi的驱动这里使用的是迪芝伦的github上面开源的ip,链接如下:

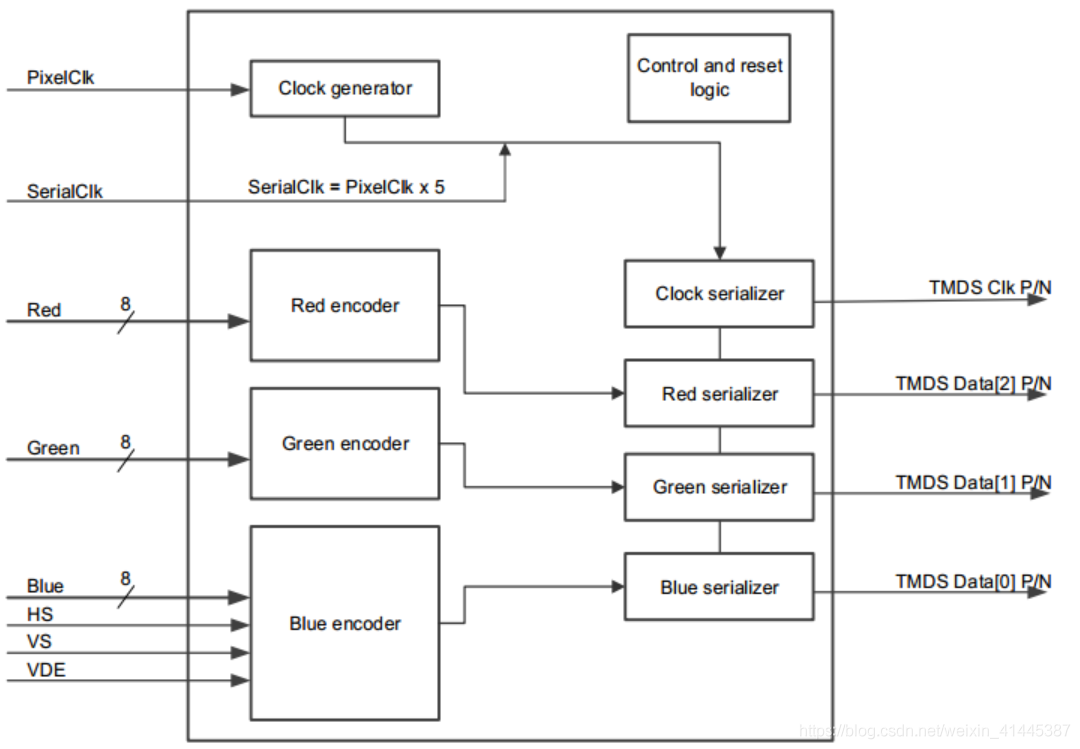

hdmi ip链接 ip系统框图:

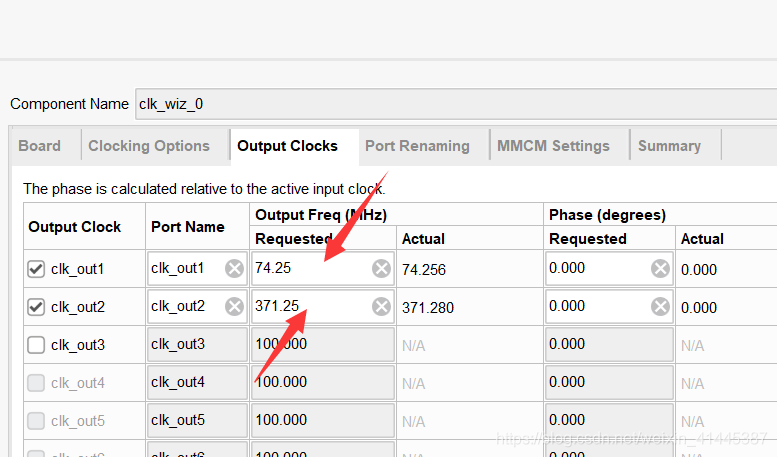

添加ip进入工程,后设置时钟ip的参数

彩条测试文件

input clk, //像素时钟输入,1280x720@60P的像素时钟为74.25

input rst, //复位,高有效

output hs, //行同步、高有效

output vs, //场同步、高有效

output de, //数据有效

output[7:0] rgb_r, //像素数据、红色分量

output[7:0] rgb_g, //像素数据、绿色分量

output[7:0] rgb_b //像素数据、蓝色分量

);

/*********视频时序参数定义******************************************/

parameter H_ACTIVE = 16'd1280; //行有效长度(像素时钟周期个数)

parameter H_FP = 16'd110; //行同步前肩长度

parameter H_SYNC = 16'd40; //行同步长度

parameter H_BP = 16'd220; //行同步后肩长度

parameter V_ACTIVE = 16'd720; //场有效长度(行的个数)

parameter V_FP = 16'd5; //场同步前肩长度

parameter V_SYNC = 16'd5; //场同步长度

parameter V_BP = 16'd20; //场同步后肩长度

//parameter H_FP = 16'd88;

//parameter H_SYNC = 16'd44;

//parameter H_BP = 16'd148;

//parameter V_ACTIVE = 16'd1080;

//parameter V_FP = 16'd4;

//parameter V_SYNC = 16'd5;

//parameter V_BP = 16'd36;

parameter H_TOTAL = H_ACTIVE + H_FP + H_SYNC + H_BP;//行总长度

parameter V_TOTAL = V_ACTIVE + V_FP + V_SYNC + V_BP;//场总长度

/*********彩条RGB color bar颜色参数定义*****************************/

parameter WHITE_R = 8'hff;

parameter WHITE_G = 8'hff;

parameter WHITE_B = 8'hff;

parameter YELLOW_R = 8'hff;

parameter YELLOW_G = 8'hff;

parameter YELLOW_B = 8'h00;

parameter CYAN_R = 8'h00;

parameter CYAN_G = 8'hff;

parameter CYAN_B = 8'hff;

parameter GREEN_R = 8'h00;

parameter GREEN_G = 8'hff;

parameter GREEN_B = 8'h00;

parameter MAGENTA_R = 8'hff;

parameter MAGENTA_G = 8'h00;

parameter MAGENTA_B = 8'hff;

parameter RED_R = 8'hff;

parameter RED_G = 8'h00;

parameter RED_B = 8'h00;

parameter BLUE_R = 8'h00;

parameter BLUE_G = 8'h00;

parameter BLUE_B = 8'hff;

parameter BLACK_R = 8'h00;

parameter BLACK_G = 8'h00;

parameter BLACK_B = 8'h00;

reg hs_reg;//定义一个寄存器,用于行同步

reg vs_reg;//定义一个寄存器,用户场同步

reg hs_reg_d0;//hs_reg一个时钟的延迟

//所有以_d0、d1、d2等为后缀的均为某个寄存器的延迟

reg vs_reg_d0;//vs_reg一个时钟的延迟

reg[11:0] h_cnt;//用于行的计数器

reg[11:0] v_cnt;//用于场(帧)的计数器

reg[11:0] active_x;//有效图像的的坐标x

reg[11:0] active_y;//有效图像的坐标y

reg[7:0] rgb_r_reg;//像素数据r分量

reg[7:0] rgb_g_reg;//像素数据g分量

reg[7:0] rgb_b_reg;//像素数据b分量

reg h_active;//行图像有效

reg v_active;//场图像有效

wire video_active;//一帧内图像的有效区域h_active & v_active

reg video_active_d0;

assign hs = hs_reg_d0;

assign vs = vs_reg_d0;

assign video_active = h_active & v_active;

assign de = video_active_d0;

assign rgb_r = rgb_r_reg;

assign rgb_g = rgb_g_reg;

assign rgb_b = rgb_b_reg;

always@(posedge clk or posedge rst)

begin

if(rst)

begin

hs_reg_d0 <= 1'b0;

vs_reg_d0 <= 1'b0;

video_active_d0 <= 1'b0;

end

else

begin

hs_reg_d0 <= hs_reg;

vs_reg_d0 <= vs_reg;

video_active_d0 <= video_active;

end

end

always@(posedge clk or posedge rst)

begin

if(rst)

h_cnt <= 12'd0;

else if(h_cnt == H_TOTAL - 1)//行计数器到最大值清零

h_cnt <= 12'd0;

else

h_cnt <= h_cnt + 12'd1;

end

always@(posedge clk or posedge rst)

begin

if(rst)

active_x <= 12'd0;

else if(h_cnt >= H_FP + H_SYNC + H_BP - 1)//计算图像的x坐标

active_x <= h_cnt - (H_FP[11:0] + H_SYNC[11:0] + H_BP[11:0] - 12'd1);

else

active_x <= active_x;

end

always@(posedge clk or posedge rst)

begin

if(rst)

v_cnt <= 12'd0;

else if(h_cnt == H_FP - 1)//在行数计算器为H_FP - 1的时候场计数器+1或清零

if(v_cnt == V_TOTAL - 1)//场计数器到最大值了,清零

v_cnt <= 12'd0;

else

v_cnt <= v_cnt + 12'd1;//没到最大值,+1

else

v_cnt <= v_cnt;

end

always@(posedge clk or posedge rst)

begin

if(rst)

hs_reg <= 1'b0;

else if(h_cnt == H_FP - 1)//行同步开始了...

hs_reg <= 1'b1;

else if(h_cnt == H_FP + H_SYNC - 1)//行同步这时候要结束了

hs_reg <= 1'b0;

else

hs_reg <= hs_reg;

end

always@(posedge clk or posedge rst)

begin

if(rst)

h_active <= 1'b0;

else if(h_cnt == H_FP + H_SYNC + H_BP - 1)

h_active <= 1'b1;

else if(h_cnt == H_TOTAL - 1)

h_active <= 1'b0;

else

h_active <= h_active;

end

always@(posedge clk or posedge rst)

begin

if(rst)

vs_reg <= 1'd0;

else if((v_cnt == V_FP - 1) && (h_cnt == H_FP - 1))

vs_reg <= 1'b1;

else if((v_cnt == V_FP + V_SYNC - 1) && (h_cnt == H_FP - 1))

vs_reg <= 1'b0;

else

vs_reg <= vs_reg;

end

always@(posedge clk or posedge rst)

begin

if(rst)

v_active <= 1'd0;

else if((v_cnt == V_FP + V_SYNC + V_BP - 1) && (h_cnt == H_FP - 1))

v_active <= 1'b1;

else if((v_cnt == V_TOTAL - 1) && (h_cnt == H_FP - 1))

v_active <= 1'b0;

else

v_active <= v_active;

end

always@(posedge clk or posedge rst)

begin

if(rst)

begin

rgb_r_reg <= 8'h00;

rgb_g_reg <= 8'h00;

rgb_b_reg <= 8'h00;

end

else if(video_active)

if(active_x == 12'd0)

begin

rgb_r_reg <= WHITE_R;

rgb_g_reg <= WHITE_G;

rgb_b_reg <= WHITE_B;

end

else if(active_x == (H_ACTIVE/8) * 1)

begin

rgb_r_reg <= YELLOW_R;

rgb_g_reg <= YELLOW_G;

rgb_b_reg <= YELLOW_B;

end

else if(active_x == (H_ACTIVE/8) * 2)

begin

rgb_r_reg <= CYAN_R;

rgb_g_reg <= CYAN_G;

rgb_b_reg <= CYAN_B;

end

else if(active_x == (H_ACTIVE/8) * 3)

begin

rgb_r_reg <= GREEN_R;

rgb_g_reg <= GREEN_G;

rgb_b_reg <= GREEN_B;

end

else if(active_x == (H_ACTIVE/8) * 4)

begin

rgb_r_reg <= MAGENTA_R;

rgb_g_reg <= MAGENTA_G;

rgb_b_reg <= MAGENTA_B;

end

else if(active_x == (H_ACTIVE/8) * 5)

begin

rgb_r_reg <= RED_R;

rgb_g_reg <= RED_G;

rgb_b_reg <= RED_B;

end

else if(active_x == (H_ACTIVE/8) * 6)

begin

rgb_r_reg <= BLUE_R;

rgb_g_reg <= BLUE_G;

rgb_b_reg <= BLUE_B;

end

else if(active_x == (H_ACTIVE/8) * 7)

begin

rgb_r_reg <= BLACK_R;

rgb_g_reg <= BLACK_G;

rgb_b_reg <= BLACK_B;

end

else

begin

rgb_r_reg <= rgb_r_reg;

rgb_g_reg <= rgb_g_reg;

rgb_b_reg <= rgb_b_reg;

end

else

begin

rgb_r_reg <= 8'h00;

rgb_g_reg <= 8'h00;

rgb_b_reg <= 8'h00;

顶层模块

module pro_hdmi_top(

input clk,

output [0:0] HDMI_OEN,

output TMDS_Clk_n,

output TMDS_Clk_p,

output [2:0] TMDS_Data_n,

output [2:0] TMDS_Data_p

);

wire Pixel_clk;

wire Serial_clk;

wire video_hs;

wire video_vs;

wire video_de;

wire [7:0] video_r;

wire [7:0] video_g;

wire [7:0] video_b;

assign HDMI_OEN = 1'b1;

//实例化色彩模?

color_bar uut_color_bar(

.clk (Pixel_clk),

.rst (1'b0),

.hs (video_hs),

.vs (video_vs),

.de (video_de),

.rgb_r (video_r),

.rgb_g (video_g),

.rgb_b (video_b)

);

//时钟信号

clk_wiz_0 uut_clk(

// Clock out ports

.clk_out1(Pixel_clk), // output clk_out1

.clk_out2(Serial_clk), // output clk_out2

// Status and control signals

.reset(1'b0), // input reset

.locked(), // output locked

// Clock in ports

.clk_in1(clk)

); // input clk_in1

//hdmi驱动

hdmi_disp_0 uut_hdmi_disp_0 (

.TMDS_Clk_p(TMDS_Clk_p), // output wire TMDS_Clk_p

.TMDS_Clk_n(TMDS_Clk_n), // output wire TMDS_Clk_n

.TMDS_Data_p(TMDS_Data_p), // output wire [2 : 0] TMDS_Data_p

.TMDS_Data_n(TMDS_Data_n), // output wire [2 : 0] TMDS_Data_n

.aRst(1'b0), // input wire aRst

.aRst_n(1'b1), // input wire aRst_n

.vid_pData({video_r,video_b,video_g}), // input wire [23 : 0] vid_pData

.vid_pVDE(video_de), // input wire vid_pVDE

.vid_pHSync(video_hs), // input wire vid_pHSync

.vid_pVSync(video_vs), // input wire vid_pVSync

.PixelClk(Pixel_clk), // input wire PixelClk

.SerialClk(Serial_clk) // input wire SerialClk

);

实验效果

reference

HDMI/DVI新技术与芯片及其应用HDMI的FPGA实现(一)基于FPGA的HDMI高清显示接口驱动基于FPGA的HDMI显示(二)基于FPGA的HDMI显示(一)