在嵌入式开发领域,单片机是很多工程师的入门起点,不少单片机开发者在积累一定经验后,会选择转向FPGA开发——毕竟FPGA在并行处理、高速接口、实时性等方面的优势,是单片机难以企及的,且掌握FPGA技术后,薪资提升空间显著。但现实往往是:很多单片机“大佬”自信满满上手FPGA,却很快陷入“时序炸了、资源爆了、逻辑错乱”的困境,甚至怀疑自己的技术能力。

核心原因并非FPGA难度过高,而是单片机与FPGA的底层设计思维存在本质差异。很多开发者习惯用单片机的“控制思维”硬套FPGA的“硬件思维”,忽略了两者的核心区别,最终在误区中反复内耗,浪费大量时间。今天,成电国芯就为大家深度拆解单片机转FPGA最容易踩的4个致命误区,结合技术原理和实际开发场景,帮大家理清思路、避开陷阱,快速实现从单片机到FPGA的平滑过渡。

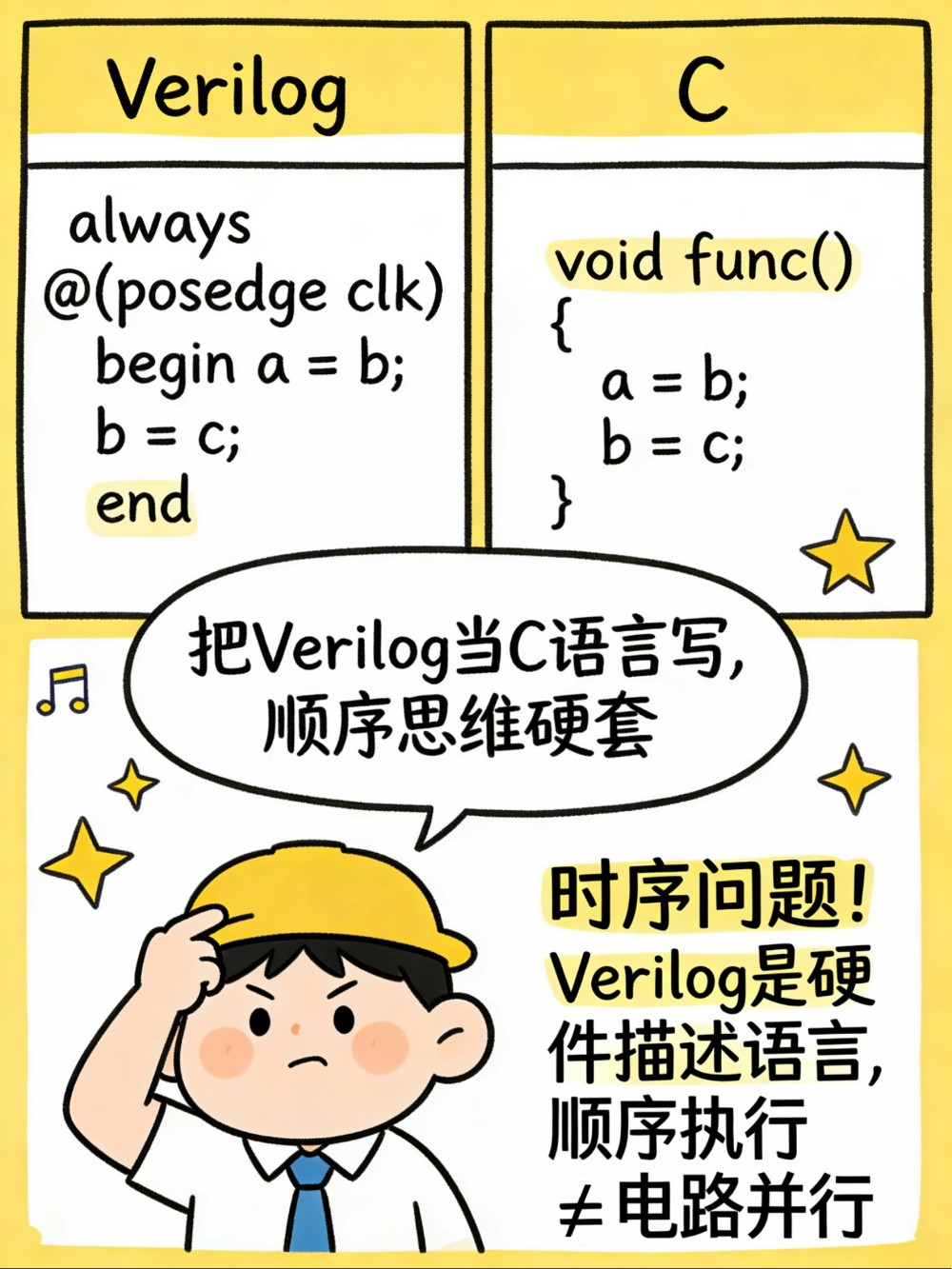

误区一:把Verilog当C语言写,顺序思维硬套

这是单片机转FPGA最常见、最致命的第一个误区,没有之一。很多开发者看到Verilog的语法(如if、for、while)和C语言相似,就想当然地认为“只要会写C语言,就能写Verilog”,甚至直接用C语言的顺序执行思维来编写FPGA代码,最终导致设计无法正常工作。

要明确一个核心认知:单片机是软件驱动的顺序执行架构,FPGA是硬件驱动的并行执行架构,两者的运行逻辑有着天壤之别。

单片机的核心是CPU,执行代码时遵循“逐条读取、顺序执行”的原则——你写的每一行C代码,都会被编译成机器指令,由CPU按顺序执行,哪怕是循环、条件判断,也是CPU依次处理每一个步骤。这种“一步一步来”的思维,已经深深烙印在很多单片机开发者的脑海中。

但FPGA完全不同:FPGA的本质是“可编程逻辑器件”,内部由大量的可配置逻辑块(CLB)、触发器、布线资源等硬件单元组成,Verilog代码并非“程序”,而是“硬件描述语言”——你写的每一行代码,本质上是在“画电路图”,描述的是硬件单元的连接关系和逻辑功能,而非执行步骤。

举个简单的例子:同样是“if-else”语句,在C语言中,CPU会先判断条件是否成立,再执行对应的分支,两个分支不会同时执行;但在Verilog中,if-else语句综合后,会生成一个多路选择器(MUX),两个分支对应的逻辑会同时存在于硬件中,根据输入条件选择对应的输出,本质是并行的硬件结构。

再比如for循环,C语言中的for循环是“循环执行某段代码”,执行次数由循环条件决定;而Verilog中的for循环(非generate语句),综合后会生成多个相同的硬件模块(如多个寄存器、加法器),实现并行处理,而非顺序循环执行。

用顺序思维写并行硬件,必然会导致三个严重问题:一是时序不收敛,代码逻辑与硬件结构不匹配,信号传输延迟超出时钟周期;二是逻辑冗余,生成大量不必要的硬件单元,浪费FPGA资源;三是无法达到目标频率,哪怕是简单的逻辑,也可能跑不起几十MHz的时钟,更别说高速场景。

✅ 正确做法:彻底抛弃C语言的顺序思维,建立“硬件并行思维”。编写Verilog代码前,先在脑海中勾勒出对应的硬件电路图,明确每个模块的功能和连接关系;避免用顺序执行的思路设计逻辑,多使用组合逻辑、时序逻辑的并行特性,让代码贴合FPGA的硬件架构。

误区二:无视时序约束,觉得“能跑就行”

单片机开发者转FPGA后,第二个容易踩的坑,就是“无视时序约束”——在单片机开发中,时序基本由晶振决定,开发者只需关注代码逻辑是否正确,无需额外处理时序问题,久而久之就形成了“能跑就行”的思维定式。但这种思维,在FPGA开发中会直接导致设计失败。

为什么FPGA必须重视时序约束?因为FPGA的工作频率远高于单片机——单片机的工作频率通常在几MHz到几十MHz,而FPGA的工作频率可轻松达到几十MHz甚至几百MHz,部分高性能FPGA甚至能突破1GHz。当频率提升,信号的传输延迟、建立时间、保持时间等时序问题会被无限放大,一旦时序不满足,设计就会出现各种异常。

时序约束的核心作用,是向FPGA开发工具(如Vivado、Quartus)传达设计者的时序意图,告诉工具“设计需要达到多少频率”“信号之间的时序关系是什么”,工具会根据约束进行综合、布局布线,确保所有信号的传输都满足时序要求,实现时序收敛。时序收敛是指经过逻辑综合和布局布线后,设计中的每一条时序路径都完美满足了约束要求,没有任何建立时间和保持时间的违例。

很多单片机转FPGA的开发者,初期会忽略时序约束,甚至不知道SDC(Synopsys Design Constraints)约束文件是什么,觉得“代码仿真通过、上板能点灯”就万事大吉。但实际上,这种“能跑”只是偶然——可能在低频率下暂时正常,但一旦提升频率,就会出现数据错乱、信号不稳定的问题;更严重的是,未加约束的设计,可能在布局布线时出现资源冲突,导致板子直接报废。

我们曾遇到过这样的案例:一位单片机开发者,用FPGA设计一个简单的UART通信模块,仿真通过后上板测试,低频率下能正常通信,但提升到50MHz后,数据传输频繁出错,调试了整整一周,最后发现问题仅仅是“没有添加时钟约束”——工具默认按最低频率布局布线,无法满足50MHz的时序要求,添加SDC约束后,问题瞬间解决。

SDC约束的编写有明确的逻辑和步骤,核心可分为四步:第一步建立时钟,确立系统的时间轴,通过create_clock等指令定义主时钟、衍生时钟及相关参数;第二步约束边界与I/O,划分系统级时序预算,用set_input_delay、set_output_delay等指令定义接口时间关系;第三步划分时钟域与关系,通过set_clock_groups等指令声明不同时钟域的关系,消除虚假时序违例;第四步设置时序例外与微调,用set_false_path、set_multicycle_path等指令处理特殊路径,优化关键时序。

✅ 正确做法:从设计初期就重视时序约束,养成“先约束、后设计”的习惯。明确设计的目标频率,编写完整的SDC约束文件,涵盖时钟约束、I/O约束、跨时钟域约束等;设计完成后,一定要查看时序报告,分析时序违例原因,针对性优化布局布线,确保时序收敛。

误区三:滥用组合逻辑,到处写latch还不知道

单片机开发中,开发者可以随手写条件判断、逻辑运算,无需担心额外问题;但在FPGA开发中,组合逻辑的使用需要格外谨慎,一旦使用不当,就会生成不必要的锁存器(latch),引发一系列致命问题,这也是很多新手“查bug查到崩溃”的核心原因。

首先要明确:锁存器(latch)是一种电平敏感的存储元件,它会根据输入电平的变化,实时改变输出状态,且在输入电平消失后,会保持当前输出状态。但FPGA开发中,我们更倾向于使用触发器(flip-flop)而非锁存器——触发器是边沿敏感的,只有在时钟有效边沿到来时,才会更新输出状态,时序更稳定,也更便于时序分析。

那么,锁存器是怎么被“无意生成”的?核心原因是组合逻辑编写不规范,尤其是单片机开发者习惯的“不完整条件判断”,在FPGA中会直接触发锁存器生成。根据Intel相关技术文档,当CASE或IF语句没有覆盖所有可能的输入条件时,综合工具会推断出锁存器,以保持输出信号的原有值。

最常见的三种情况:一是if语句没有写else分支,比如“if(en) q = data;”,当en为低电平时,q没有明确的赋值,综合工具会生成锁存器,让q保持当前值;二是case语句没有写default分支,没有覆盖所有可能的输入情况,同样会生成锁存器;三是组合逻辑出现反馈回路,即输出信号反馈到输入端,形成电平敏感的存储结构,诱发锁存器。

锁存器的危害非常大:一是会导致信号出现毛刺,影响逻辑正确性;二是容易引发亚稳态,尤其是在高速场景下,导致信号不稳定;三是破坏时序收敛,锁存器的电平敏感特性会让时序分析变得复杂,甚至无法收敛;四是增加功耗,锁存器会持续消耗电能,尤其是在高频场景下,功耗问题会更加突出。很多开发者遇到“板子一跑就玄学抽风,时而正常、时而出错”的情况,大概率就是锁存器在作祟。

举个错误示例:在组合逻辑always块中,未写else分支,会生成锁存器:

| verilog // 错误示例:会生成锁存器 always @(*) begin if (en) q = data; // 缺少else分支,当en为0时,q会保持原有值,综合为锁存器 end |

正确示例:补全else分支,或在always块开头为信号赋初值,避免锁存器生成:

| verilog // 正确示例1:补全else分支 always @(*) begin if (en) q = data; else q = 1'b0; end // 正确示例2:开头赋初值 always @(*) begin q = 1'b0; // 初值,确保所有路径都有明确赋值 if (en) q = data; end |

✅ 正确做法:规范组合逻辑编写,避免生成无意锁存器。写if语句时必须补全else分支,写case语句时必须添加default分支;尽量减少不必要的组合逻辑,复杂逻辑优先使用时序逻辑(带时钟的always块);设计完成后,查看综合报告,确认是否有锁存器生成,若有及时优化代码。

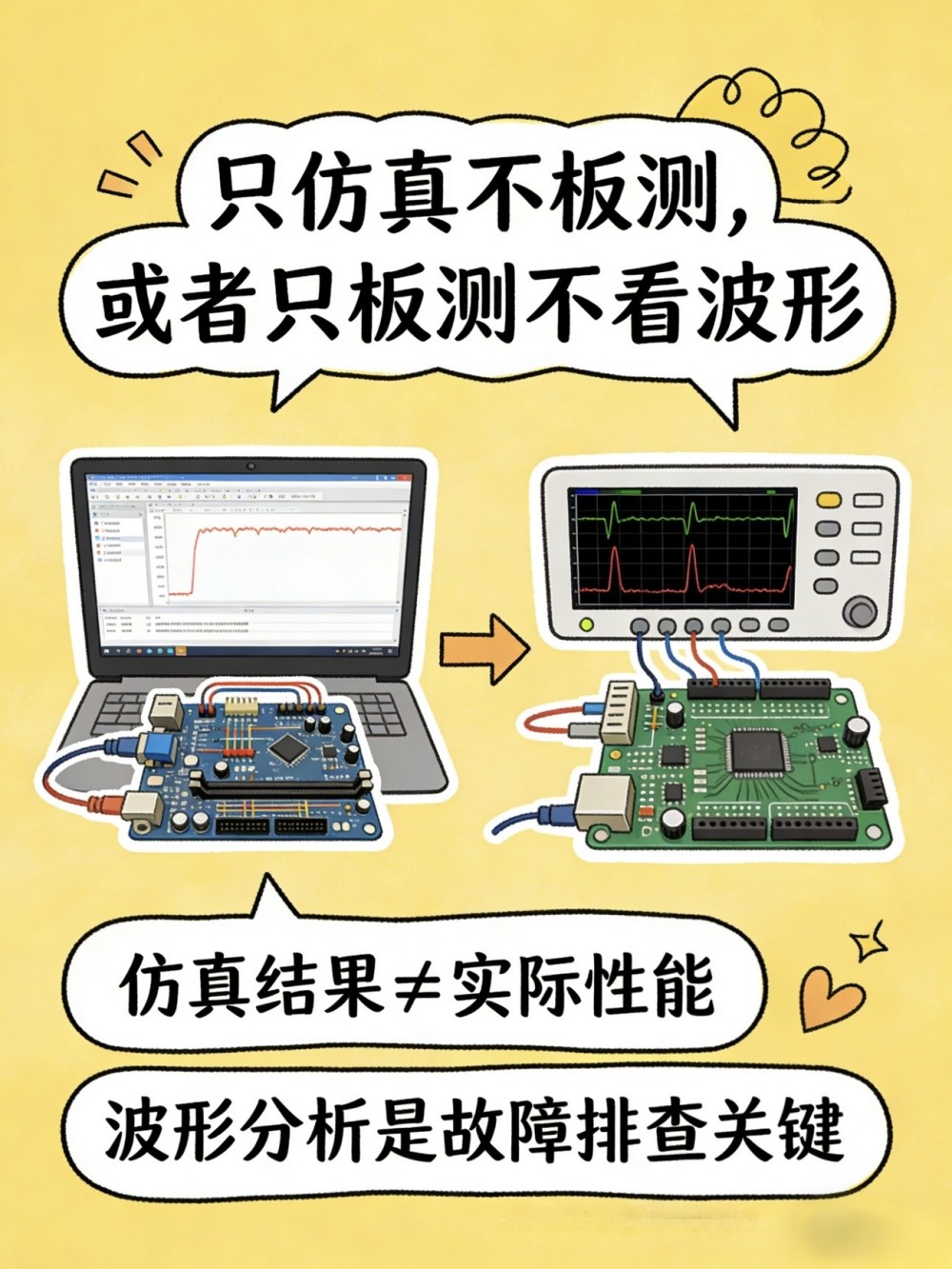

误区四:只仿真不板测,或者只板测不看波形

单片机开发中,很多开发者的习惯是“点灯亮了就完事”——只要代码仿真通过,上板后能实现预期功能(比如点亮LED、实现UART通信),就认为设计没问题。但这种“粗放式”的开发思路,在FPGA开发中完全行不通,很多开发者就是因为忽略了“仿真与板测的结合”,导致设计在量产时出现大量问题。

FPGA的开发流程远比单片机复杂,核心流程包括设计输入、仿真、综合、布局布线、配置文件生成、上板测试,其中“仿真”和“板测”是两个不可或缺的环节,且两者必须结合,缺一不可。很多开发者陷入两个极端:要么只做仿真,不进行板测,认为“仿真通过就一定能上板运行”;要么只做板测,不看波形、不分析时序,认为“上板能跑就没问题”。

首先要明确两个核心认知:仿真过了≠板上能跑;板上亮了≠时序稳定。

仿真(包括功能仿真和时序仿真)的作用是验证逻辑功能的正确性和时序的合理性,但仿真环境是理想的——忽略了FPGA内部的布线延迟、器件损耗、外部干扰等实际因素。比如,功能仿真只验证逻辑是否正确,不考虑时序延迟;时序仿真虽然会加入延迟模型,但无法完全模拟实际硬件的复杂环境,因此仿真通过的设计,上板后可能会因为实际延迟、干扰等问题,出现功能异常。

而只板测不看波形、不分析时序,更是FPGA开发的“大忌”。单片机点灯亮了,基本能说明逻辑没问题;但FPGA点灯亮了,只能说明“部分逻辑正常”,无法说明时序稳定——可能在低频率下正常,高频下就会出错;可能单次测试正常,批量生产后就出现问题;可能在常温下正常,在高低温环境下就出现逻辑错乱。尤其是在高速接口(如SPI、I2C、DDR)设计中,不看波形、不分析时序,很容易出现数据传输错误,甚至导致整个系统崩溃。

真正的FPGA开发,必须做到“仿真+时序+上板+抓波形”四位一体:功能仿真验证逻辑正确性,时序仿真验证时序合理性,上板测试验证实际运行效果,抓波形(用示波器、逻辑分析仪)分析信号状态,排查时序问题、干扰问题。比如,上板后发现数据错乱,通过抓波形可以快速定位是时序违例、信号毛刺,还是跨时钟域处理不当,从而针对性优化设计。

此外,FPGA开发中,时序报告的查看也至关重要——通过时序报告,能清晰看到时序违例的路径、延迟情况,帮助开发者优化布局布线、调整约束,确保设计的稳定性。很多开发者忽略时序报告,导致明明存在时序问题,却无从下手排查,浪费大量调试时间。

✅ 正确做法:养成“仿真先行、板测验证、波形分析”的习惯。设计初期先做功能仿真,确保逻辑正确;综合、布局布线后做时序仿真,验证时序收敛;上板测试时,用示波器、逻辑分析仪抓波形,分析信号状态;同时查看时序报告,及时排查时序问题,确保设计在实际场景中稳定运行。

结语:从“控制思维”到“硬件思维”,才是入门FPGA的关键

单片机转FPGA,看似是“换一种开发工具、换一种编程语言”,实则是“换一种设计思维”——单片机是“控制思维”,核心是“用软件控制硬件,顺序执行指令”;FPGA是“硬件思维”,核心是“用代码描述硬件,并行实现功能”。

很多单片机开发者转FPGA之所以屡屡碰壁,不是因为技术不够,而是因为没有放下旧的思维习惯,用单片机的逻辑去硬套FPGA的设计。以上4个误区,是90%的开发者都会踩的坑,也是阻碍大家快速入门FPGA的核心障碍。

成电国芯提醒各位开发者:转向FPGA开发,不要急于上手写代码,先静下心来理解FPGA的硬件架构、并行思维、时序约束等核心概念,避开上述误区;在实际开发中,多仿真、多板测、多分析波形,积累硬件设计经验,逐步建立“硬件思维”。

FPGA开发的门槛虽高,但一旦入门,就能解锁更高的技术上限和薪资空间——从单片机的“控制级”开发,升级到FPGA的“硬件级”开发,你会发现嵌入式开发的全新天地。

愿每一位单片机转FPGA的开发者,都能避开误区、少走弯路,快速掌握FPGA核心技术,在嵌入式赛道上实现突破,实现薪资与能力的双重提升!

EE大二学生