想在FPGA领域崭露头角?这些高含金量赛事你不能错过!从蓝桥杯到电赛、集创赛,本文梳理全流程攻略,助你高效备赛拿大奖~

一、赛事大盘点:两类玩法,不同备战策略

FPGA赛道的核心赛事分为两类,玩法差异显著:

▶ 可提前准备的赛事(电赛/竞赛/集创赛)

形式:组队参赛(2-3人),提前完成项目开发(代码+硬件),提交效果展示。

时间:电赛/集创赛在年初3-4月,竞赛在8-9月。

关键:图像类项目最易拿奖(场景丰富、效果直观),需结合系统集成(PS+PL协同)。

▶ 现场答题类赛事(蓝桥杯FPGA赛道)

形式:单人赛,5小时封闭答题(禁止上网),现场完成Verilog代码编写+硬件调试。

现状:第17届是第二届FPGA赛道,报名已开启(截止时间关注官网),重点考察基本功(数电模电、语法、开发流程)。

二、热门方向:图像类为何成拿奖“香饽饽”?

图像类项目是赛事“常胜将军”,原因在于:场景落地性强、技术栈成熟、易展示效果。

▶ 经典项目示例

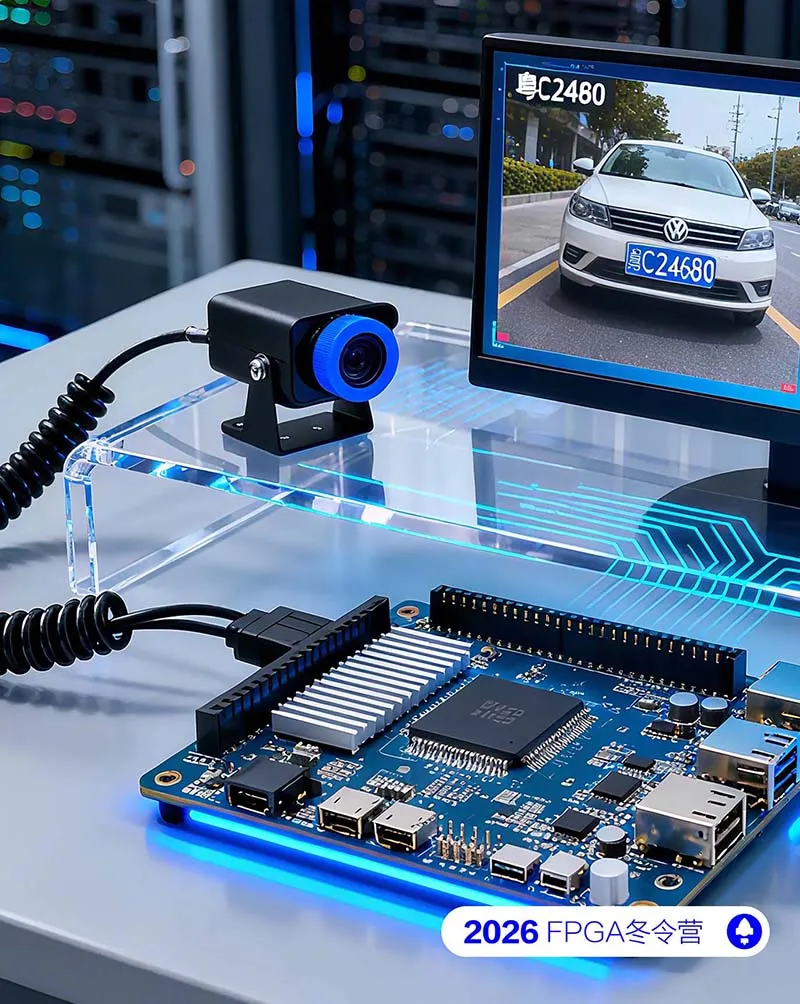

车牌识别:不止识别车牌,需结合场景(停车场空位统计+费用计算+APP联动)。

动态目标检测:用帧差法实时检测,通过以太网传输到上位机。

以太网视频传输:摄像头图像经千兆/万兆以太网发送,需帧封装(帧头标识帧起始)。

▶ 拿奖核心:系统集成

项目需做到PS侧(软件)+ PL侧(硬件)协同:

PS侧:部署Linux/Windows系统(类比车载电脑,负责决策)。

PL侧:优化FPGA代码(类比发动机,决定速度/功耗)。

两者结合,获奖概率翻倍!

三、技术核心:这些技能必须掌握

▶ 图像采集与处理

采集:摄像头寄存器配置(248个参数)、RGB565数据缓存(避免雪花屏)。

处理:二值边缘检测(提取轮廓)、字符分割(区分汉字/数字)、帧差法(动态检测)。

▶ 蓝桥杯重点考点

数电模电:基本逻辑门(异或)、D触发器(时序逻辑)、负三DB(半功率点,功率衰减50%)。

开发流程:综合(代码转门级网表)、布局布线(管脚分配+时序约束)。

调试:串口输出中间值、仿真(前仿真查逻辑,后仿真查时序)、ILA逻辑分析仪。

四、拿奖技巧:卷赢对手的3个秘诀

1. 分工明确,避免内耗

组队2-3人,各司其职:

FPGA开发:PL侧代码(采集/处理)。

硬件设计:PCB打板(替代杜邦线,提升稳定性)。

算法/上位机:算法转Verilog,开发APP/网页。

2. 项目融合,提升复杂度

将车牌识别、动态检测、以太网传输融合,形成“采集→处理→传输→展示”完整链路,国奖更有戏!

3. 关注赛事信息,及时跟进

官网+补充渠道:赛事细节(报名/题目)在官网和社群发布,需重点关注。

提前备赛:电赛/集创赛需提前6个月准备项目。

廖老师FPGA赛事课公开课完整内容整理

一、比赛类型及形式介绍

1.1 可提前准备的比赛(竞赛、集创赛等)

廖老师:首先,关于我们这次神经模型的公开课,我们一共有对应或者说对应FPGA赛道来说,有三个有三到四个相对来说比较重要的赛事。第一个竞赛电赛,然后就是竞赛,还有集创赛,这里是他们的全称,然后这里还有一个没有罗列到的,马上会重点去讲的。

廖老师:第17届蓝桥杯。第17届蓝桥杯。第17届蓝桥杯,一共今天我们要讲的主要就是这四个比赛。然后这三个为什么和蓝桥杯我做了一个区分来讲,就是因为这三个比赛都是干嘛,都是我们可以在私底下把代码写好,或者说写好提前写好那个项目,然后做把它最后的那个效果进行一个提交,它是这种的比赛形式,但是蓝桥杯,它是不一样的,蓝桥杯它是首先它是单人赛这些,其他这三个都是可以组队的蓝桥杯它的比赛形式是给你五个小时时间给你出一张卷子,然后让你去做,给你提供一些器件,然后让你在一个封闭的场地,然后去进行完成这些。

廖老师:电赛竞赛集创赛他们这三个是我们可以提前去做的,这是有一定区别的,所以说我们现在先讲这三个比赛。做的一般都是以图像为主,因为图像相对来说是比较好拿奖的。

廖老师:然后首先是我们这三个比赛的网址,这里都给大家了,然后这种官方的补充渠道是非常重要的,甚至某种意义上来说,比它官网上面公布的一些信息还要细致一点,不能说重要,更加的细致一点明白吧,大家一定要多多的关注这里,大家可以截图去看一下,这几个比赛。

廖老师:这就不带大家看了,等下次会带大家着重去看一下,马上就会有的蓝桥杯,因为蓝桥杯在这个月月底10月29号,12月29号11月22就好了,然后就会完成,就会截止报名。然后像这种打比赛的时间,竞赛的时间会晚一点,一般情况下是在八九月,然后其他几个都不是在年初三四月份的时候,他们两个年初三四月份的时候就会去完成比赛,然后在年底的时候基本上就已经结束了,能进国赛的同学上半年就能准备好。要注意一个点:我们现在越来越卷,真的是越来越卷,像以前最早的时候他们做一个什么千兆或万兆的以太网的视频传输都能去拿一个奖,但是现在完全不行了,只能刚好过一个省奖,拿国奖是很难的,现在是越来越卷了,我们就要去避免一些东西,比如说我们在起那个名字的时候,不要觉得那个起了个名字,就是项目,你那个项目起个名字随随便便就起了一下。

廖老师:你比如说我们最常见的比较常见的车牌识别。那这里我们的赛思课上面也有其中一个项目是车牌识别,你就不要直接去写个什么车牌识别,你不但要有车牌识别,你还要去识别一些其他的东西,比如说你那个车牌识别,你要去结合它的使用场景,比如说我们在小区的时候怎么去使用,然后去结合,比如说我进来之后,我可以统计我整个小区、整个停车场还有多少个空位,然后他们停的时间是多久,然后能不能给出我们相应的一些停车费用之类的,然后我们出闸口的时候,我们识别出来对应的车牌之后能不能自动去生成一个二维码,然后让司机去扫一个二维码,我们能不能去搭建一个对应的那种APP之类的。

廖老师:这和我们队友有关系?我们刚才说的那种项目算是一个拿奖方向,如果能做到那种程度,再加一点别的辅助性的外设,那么拿奖的概率其实很大,然后你再去做对应的模型,这个时候就涉及到了我们的队友。我们队友最好是怎样?我们要实现一个。

廖老师:一份比较好的作品,FPGA主要做的是什么?我们其实某种意义上来说是做的软件,但是这个软件和大家印象中那个软件是不太一样,这个软件是指的我们把程序下到板卡里面的那个软件,硬件就是一般是指的PCB,它要去打板,我们做的那些东西要集成到对应的驱动板上面去,而不能说直接就是我拿杜邦线去连,那样的效果会打一些折扣。这种东西就是我们软件要干的事,当然了,还有一种软件是指的比如说我们经常听说的写一个app或者说写一个网页那种软件,和我们这里的是不太一样的,然后还要有一个专门的同学去负责做算法,算法其实都是大差不差的东西,或者说算法它本身都是一个东西,只不过在不同的地方用,比如说我在FPGA中用、在32位单片机中用,它们的算法最核心的内容都是一样的,都是那些数据公式,难的是什么?难的是我们把需要使用的算法找出来,然后转化成对应的Verilog代码,比如我们用Verilog语言去写,怎么把公式转化成我们的代码,这个才是算法这方面的难点。我们找队友一定要避免一个点:不能找那种不干活的,不会可以一起慢慢学,但是一定不要找那种摆烂的,会影响拖累你们整个队伍的进度。这一点是非常重要的,因为你们通常情况下打比赛都是两到三人组,你其中有一个打退堂鼓了,就会导致大家都在这方面受影响,然后一定不要觉得人少,因为一般情况下组队都是好朋友,但不能说组队都是好朋友就随便,你必须得有一个明确的分工。

廖老师:不能我干你也干,到时候做出来的东西,大家时间都浪费到这一块儿,但是有一个人能把它做出来就行了,明白吗?就不要去重复的做一样东西,一定要提前做好分工,然后制定好自己需要去做的技术路线,这个可以找我们这边的老师或者说找学校带你们打比赛的老师,都是可以的,一定要做好分工。我们要提前用一个word文档之类的东西去做好任务的追踪知道吧!一定要做好这几个点,制定好我们周期性的计划,然后这个周期性计划如何制定,我们等一下讲到赛事包含哪些内容的时候,再具体细分的讲一下,然后就是我们一个获奖项目是怎样去做的,这个车牌识别很多人一听又是车牌识别,但实际上车牌识别它只是网上资源相对来说多一点,并不代表这个东西很简单,相反,它还是比较难的一个东西,因为你车牌识别的效果其实也是天差地别的,你能不能做到在同一张图片中识别多个车牌,这是第一个点,第二个点,你那个车牌能不能在动态过程中被识别到,它的响应速度又是怎么样的,这里面的东西其实还是比较多的。

廖老师:我们图像识别可以分成两个大的部分,一个是硬件。我们用图来讲,假如说这就是我们的top模块,我们首先是设计摄像头,假如说我们在摄像头采集到了数据之后,然后把这个数据处理一下,众所周知,我们摄像头过来的数据都是八位的并行口数据,但是我们一个RGB565的数据是16位对不对?RGB就是三元三基色,R是红色,G是绿色,B是蓝色,然后这三个分量分别占五个位宽、六个位宽、五个位宽,一共组成16位数据。

廖老师:我们到手之后要去做一个缓存,如果说你一个数据都不做缓存,它直接去进行显示,那么这个过程中就会出现各种各样的问题,比如说我们一个图像,就拿VGA来说,不知道大家有没有听说过VGA或者HDMI,我在这个时序点想要拿数据,但是你又没有对应的数据给我,那么这个过程中就会出现摄像头可能正常采集图像,但你呈现不出来,或者说呈现出来的屏幕是那种雪花,或者说是很多很乱的颜色线条。

廖老师:采集到之后我们去做一个缓存,最后再分两路:第一路去显示,第二路去做具体的图像处理,那么处理这里是一个很大的模块。图像处理里面,我们首先要去识别出来对应的车牌位置,然后车牌包含哪些字符?比如汉字、英文的ABCD、还有数字123456789,它们是怎么区分的,然后那个车牌上的点点是否要识别,识别出来又是以怎样的形式进行输出,比如我们的字符,汉字有很多,但车牌用不到那么多,有几个省份就有几个字符。

廖老师:那么汉字的字符我们识别出来之后又是通过什么去发送?发送到其他地方去,或者说我们直接就在显示屏上面涂一块区域出来,专门显示我们车牌识别出来的结果,还是说我们通过以太网或者三大技术协议的其中一个显示到LCD、OLED或者另外一块显示屏,或者通过以太网传输到上位机里面去进行显示,这个显示又是怎么去做的?

廖老师:Ok这是车牌识别在图像处理方面的一个难点,这里就不特别的展开说了,不然的话,可能一两个小时都讲不完。所以说我们一定要去搞清楚我们的技术难点是在哪里,就像我们前面讲到的分工,我们要怎么去分工,还是说一个人就把这些所有东西都做了,这就是很重要的一个点,一定要做好分工。然后我们做的项目,比如从HDMI驱动到图像算法,再到系统集成,大家可以看到我这上面写了一个SOC,不知道大家有没有听说过SOC?SOC(片上系统)包含PS(处理系统)和PL(可编程逻辑)两部分,PS是SOC的核心计算单元,对于我们来说,SOC指的是片上系统,片就是指我们的FPGA开发板,片上系统是什么?就是我们手机用的安卓,当然了,很少给开发板直接刷安卓操作系统进去,一般都是刷linux或者windows操作系统进去,操作系统的作用是什么?这里就很重要了,大家一定要搞明白。

廖老师:我们FPGA这边,FPGA和SOC相当于是什么?把这个东西比喻成一辆汽车的话,那么我们的SOC(PS)就是车载电脑,或者说现在经常听说的自动驾驶系统,它给整辆车发号施令;我们的FPGA(PL)就是这台车的发动机,我们跑这个项目,整个系统跑得快不快、响应速度怎么样、功耗怎么样,看我们的PL(FPGA)这边的代码。就相当于是这样的一个关系,这里某种意义上来说就是拿奖的顺序:如果各位学校对于这些比赛有校赛的话,那么你如果说是只做了一个摄像头采集到HDMI上面显示,那大概率就能过校赛;校赛完了之后你就会拿到省赛的推荐名额,省赛推荐名额拿到手之后你就去打省赛;省赛图像处理这方面你做的还算不错,那么你省赛大概率就能过,就会拿到国赛的资格,就看你有没有系统的集成,有没有去弄到PS侧?没有做到的话获奖的概率相对来说就会低一点,如果说有那就会高一点,并不是说必须得有,但是有这个东西,拿奖的概率就相对来说会大一点点。

廖老师:这个还要针对我们不同的比赛题目来说。

廖老师:然后我们的资源礼包,后面会有专门的老师给大家发,就是比如说有Verilog的基础语法、关于数电模电的一些知识点以及我们这里上一届FPGA蓝桥杯的真题以及解析,大家可以看到我这后面都是写了的,解析等下也会给大家讲,这个PDF大家可以拿过去,然后还有就是我们FPGA的一个基础语法,然后比如说蓝桥杯的,我们这一届是第17届,上一届是16届,蓝桥杯是在16届才开始有FPGA赛道的,它现在的整体资料还没有流传出来,然后蓝桥杯关于第17届怎么去报名的一些赛事大纲,这个资源礼包都会有,然后就是我们课程体系,我们赛事的课程体系是怎么样的?

廖老师:首先,我们包含了什么?总共是这样去分的:一个项目框架就是这三个项目,因为我们做的是,比如说第一个是车牌识别,然后第二个是动态目标的检测,第三个是以太网的视频传输,大家可以看到它很明显都是和图像有关的。然后一开始图像具体的采集,这就是我们整个项目的框架,包含了18个课时,大家都可以去学一下。

廖老师:具体的项目内容一共有36个,我的建议是,你如果说能把这三个项目搞到一起,能融合得很明白弄到一起的话,那么基本上就是国奖有戏!就是比较有希望了,不能说太满嘛,然后项目框架主要就是我们这里车牌识别前面的VGA到HDMI,然后再到摄像头的采集,比如说我们摄像头的寄存器怎么去配置,有248个,很多的,然后采集之后,我们用DDR去存储,还是说直接用以太网进行发送?以太网发送的过程中,PC要接收到数据,怎么去区分你这一帧是刚开始还是对于上一帧的补充,还是说你这里发的到底是什么?也就是我们要去做一个帧封装,要去做帧头的封装,然后再发给我们的PC(电脑以太网的上位机)。

廖老师:然后就是一些关于图像的具体处理,比如说二值边缘检测、车牌区域的定位以及字符分割,还有就是我们那边动态检测的帧,我们用的是帧差法,然后这些具体是怎么做的,这就是我们课程的内容,然后平台的话,这儿不得不提这个平台,这平台很过分的,为啥?我们看这个,现在大家数一下,这里有几个文件夹?一个两个三个四个五个六个文件夹,它就有五到六个平台,每一个平台它使用的环境虽然说语言都是一样的,但是它具体使用起来就是不一样,比如说什么?比如说IP核上面很不一样的。大家看我们这下面最下面,比如说紫光!紫光我们要去用PLL,紫光这东西还是算比较齐的,但是它没有SDR嘛?它就有DDR,DDR是SDRAM的一个升级版本,但是安路它就很恶心,它就没有DDR的IP核给你用,你就只能用SDR,就很难受。所以说我们就把每一个平台具体要使用到的这些都会去做一个讲解,就保证大家拿到手之后都能够去具体的使用。我们这三个项目在这五个平台都会去讲一遍,当然了,不是说代码都会去讲一遍,就是代码我们肯定是只去讲一遍,然后具体怎么去使用,在每一个平台上面都会去讲一遍的,然后这个完整的源码,这个课也会给大家提供,就是单一版卡耗材这些,然后的话我们就来讲继续来讲一下技术相关的东西。

1.2 现场答题类比赛(蓝桥杯)

廖老师:然后蓝桥杯,这个是我们的真题,我这样一边放答案一边放题吧!我们的题。第一个题:以下哪些不属于我们的基本逻辑门电路?And是什么意思?and是不是与的意思,就代表与门;or是什么意思,或门就是两个不同的取一的,它的真值就是有一为一;那叉OX是什么?XOR是什么意思?首先我们不看X,OR就是或,然后X的意思就是两个不一样的东西就为真(异或);not就是否,代表非门。这四个都是基本逻辑门,叉OX不是。那第二个题:我们D触发器描述正确的是?首先可以存储一个比特的数据,这个是D触发器的特点,这个就是数电模电的基础知识,为什么它可以存储一个比特数据?一个比特是什么意思?就是一位,一个零或者一,因为它这个数据进来之后,它会延迟输出一个时钟周期才进行输出,所以说它可以去存储一个比特数据;然后第二点,选项B:D触发器在有效边缘更新,这个肯定是对的,这本身就是D触发器的一个特点;好D触发器是时序电路的基本逻辑单元,众所周知,逻辑是长什么样子?就长这个样子,只要是在时钟的边缘触发都叫做时序逻辑,或者说和时钟挂钩的代码的逻辑都叫做时序逻辑。这个肯定就是对的,无可厚非,因为我们D触发器的特点,或者说它定义的标准就是要在上升沿或者说是下降沿边缘触发,然后并且和时钟挂钩。某种意义上对于我们写代码的来说,D触发器是在时钟的上升沿或下降沿触发,这个肯定是对的;选项D:输入端可以直接改变输出端的结果,我们是不是说了它每次要在时钟的有效边缘才能去更新输出的结果,并且会延后一个时钟周期,所以说D选项就不对。那么这句话是指的谁?是指的我们的锁存器是什么东西?latch latch,锁存器相当于我们的电平触发的组合逻辑,易产生毛刺,它什么样子?我们把这个时钟边缘触发的条件去掉,它就变成了锁存器,那么我们把这个去掉,它就直接就是那种不规则性的锁存器,它就会产生毛刺信号。而且锁存器的定义是什么?它是在电平触发的时候,并且不和时钟挂钩。当我们输入端改变时,也会去触发刚才这个代码里面的语句,所以说它就可以做到输入端改变,输出端也会发生改变,大家有没有理解到?

廖老师:然后第三题:像FPGA中PL的一个典型功能代表什么?第一个倍频分频,PL是什么东西?这个东西,我们都把这些题对应到代码上面来给大家做一个讲解。PLL就这个东西,它就是一个IP核,这个IP核是用来做什么的?当然了,这里我们选的是MMCM和PLL,PLL中文是锁相环,MMCM就是时钟管理器,它们俩其实都是一个东西,或者说MMCM是PLL的一个升级版本,MMCM它所占用的资源更多,但是它的功能也更加强大,它专门用来做分频倍频这些操作,也可以去改变它的极性和相位,在哪改?就在这,我们给大家翻译一下:这里是什么?占空比改成50%就可以改变它了,然后我们把占空比改了是某种意义上来说就是在改变相位,当然也有更直接改变相位的操作,就是直接去改变相位角度,改变多少度就可以了。那么相位是什么?肯定有同学有这个疑问,假如说我们就拿时钟来举例,一开始我们的时钟是长这个样子,然后我挪到这来开始产生,这个就叫做让它的相位开始发生了改变,就是往后挪了半个时钟周期,对不对?就往后挪半个时钟周期,那么时钟周期我们的相位改变是多少?180度,如果说我们挪了一整个时钟周期是多少?360度。

廖老师:这个幅值是什么意思?幅值我们准确的说就是这个时钟信号输出的一个电压幅值,它输出有一个电压幅值。还是刚才这张图,那么这个幅值的改变是什么?假如说这就涉及到另外一个东西,和我们刚才讲的都不太一样,它是和电气标准相挂钩的,假如说我以这根线中间这根线为例,那么我们过来的这个东西其实都是电压值,我大于这个电压值的地方,就把它认为是逻辑一,小于这个值的地方,就把它认为是逻辑零,那么这个逻辑一和逻辑零是什么意思?或者说和我们幅值相挂钩,就相当于是幅值浮动幅度拉的更大,我才能去认为它是逻辑零或者逻辑一,那我们把这里这个线虚线拉过来说。

吴同学:也行。

廖老师:怎么了?这位同学你有什么问题吗?

吴同学:挺好的。

廖老师:这哪位同学在说话?有什么问题吗同学?有问题的同学直接就问就好了,那我们继续。你这是卡到这个幅值的时候,就相当于是我们这里所需要更低的电压才能把它认为是逻辑零或者说是逻辑一,更高或者更低的电压才能去认为它是逻辑零或者逻辑一,这就是我们的电气标准,大家不要说没见过这个电气标准是在哪见到的?同样我们回到我们的代码里面去,这里是不是就是我们绑管脚的这个地方,LVTTL STD这里是什么?这里就是我们的电气标准,也就是说可以改变我们幅值的地方。那么LVCMOS/LVTTL 3.3和这一种3.3,那么它肯定是不一样的,明白吗?它肯定是不一样的,怎么去认为它是逻辑零还是逻辑一,那么这里肯定就可以去改变它的幅值。

廖老师:D选项是由谁去改变?是不是就由我们的电气标准去进行一个改变?下一题第四题:DB负三DB有没有同学知道是什么?负三DB这个DB是一个什么?同样是我们数电模电的知识点,DB它就是一个相对的对数单位,表示的就是两个数值之间的比值。它的工程公式要分成在电压条件下还是对于功率的条件下:对于功率的条件下,我们就相对来说是比较简单,就是输入和输出的比值,然后去对10取对数就可以;对于电压来说,这就是要去看它的衰减程度。拉的越高,或者说正数这边拉的越高就代表它的增大的幅度越大,拉的越低,就代表到负数这边拉的越多就代表是它衰减的越多,就相当于是这样的一个区别。那么这个负三,它是一个比较关键的点,它的定义或者说它算出来之后会给大家一个结论是什么?它是一个性能的临界点,如果说你的功率在这个时候,那么你的功率带来的增益是这么大的时候,这个滤波电路就直接被叫做半功率点,也就是说它的功率会降低一半,所以说A选项是对的,那么BC大家听到这个一半,很多同学这个题都错了,直接就是选AB选项,走事就完事儿走人。那么这B选项是对谁来说?大家看清楚题目一定要看清楚题目,B选项描述的是电压幅度而非功率幅度。直接就给出来大家有一个公式,我们就直接给它倒过来算一遍:这里我们要算的是它的衰减幅度为多少,把这个东西拿到这边来,然后把这个东西拿过去做一个乘法,就相当于是什么?就相当于这东西除以20,我们的负三除以20得出来的值,通过计算公式可以得出来,10的负0.15次方这么去计算出来,大约计算出来的比值就是70%,这个点大家也一定要记住,当然同样类型的题,它明年可能不会再考了,但是这个类型的题大家一定要去会做,我们这里就不展开讲了,因为我们现在只有还有20来分钟,后面还有几个题没讲完,然后还有更多的东西,比如说带大家去网页上面实操,看这个东西我们有哪些地方可以去寻找一些资源?

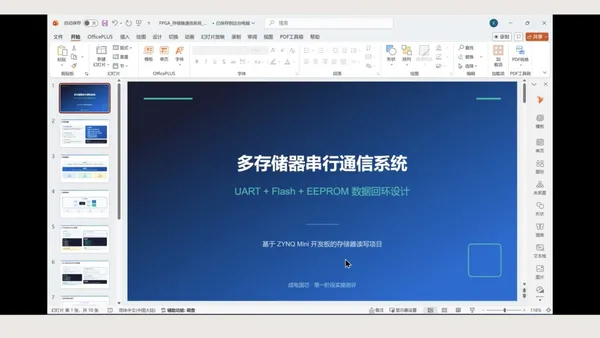

廖老师:好第五题:以下哪些串行通讯方式必须包含独立的时钟总线?包含独立的时钟线,也就说两边的时钟线不是同一根对不对?要去找异步通信,异步通信是谁?SPI有几根线?我们的四线SPI通讯一根是时钟线,然后另外两根是MOSI和MISO(主机发送从机接收、主机接收从机发送),还有一根片选信号线,然后我们的串口就只有两根线,就是我们的TX以及我们的RX。然后还有我们的I2C,I2C是不是就是两根线,一个SDA一个是SCL,SDA就是我们的数据线,它是什么?它是要的SDA图大家还有没有印象长什么样子的?

廖老师:假如说这是我们FPGA的主机,这是我们FPGA的从机,或者说就是我们的那些外设,然后他自己拉一根时钟线出来,这里也同样拉一根时钟线、拉一根数据线过来,然后这里有两个上拉电阻,都是3.3的上拉电阻,为什么是3.3?电子类为主,都是3.3。把这些都挂载到上面去?尽量挂载到上面去。就是我们I2C的那个图不知道大家还有没有印象,我们拉上拉电阻的原因是什么?这根线是什么?这根数据线是in out,代表什么意思?它是一个三态门,这根线对我们FPGA的端口来说,它既可以输入也可以输出,当我们不需要它的时候,就要相当于释放它,因为我们的I2C可以多主多重,释放它的时候,它就相当于又变成了3.3的高阻态,变成3.3的高电平,然后这个高电平我们就可以安排其他的主机这个时候去进行操控,然后就不会说一根线两个主机都在对它进行控制,就不会出现这种情况。

廖老师:这个题的话,我们的C选项是不是也可以选上?然后不是什么,它是不需要独立的时钟线,它是一个异步通信,不用管它。然后这是我们的第六节:对于串口中通信中以下哪些描述是正确的?第一个波特率误差导致通讯失败是很正常的,波特率是什么?就是指我们一秒钟可以传输多少个比特,就是我们最基本的存储单元,比如说9600、115200,我们一直念在口上的9600、115200,不知道大家到底是个什么,就是我一秒钟可以传输115200这么多个比特,一秒钟可以传输9600这么多个比特,就相当于是这样。那么B选项可以支持多主多重,这个就是错的,为什么?众所周知,我们的串口线只有两个,只有TX和RX,我们是通过数据帧的结构打包过去,然后它接收到手之后进行一个逆解析,就是我们的RX的那个操作就是一个逆解析,它是一个点对点的操作,就是一对一,所以说它实现不了多对多,但是我们把RS485的那种,RS485是什么?RS485简单可以理解成一种电气标准,或者说是一种物理意义上的端口,就相当于我直接给它改一个端口,虽然通讯协议发送的数据帧结构还是用我们的串口通讯这种数据帧结构进行发送,就是下面这个D选项说的是对的,起始位、数据位、校验位、停止位,我同样以这种形式发送出去,它就叫做串口,但是它的线就不再是只有一个TX一个RX了,它就变成更多的线了,RS485它是一个差分线,差分对的形式。

廖老师:以下可以属于是让Verilog进行综合的代码?综合是什么意思?综合是不是就是把我们写的代码转化成这样的原理图,这就是综合所干的事情。Ok知道综合他做的最根本的点是什么?接下来讲就会好讲得多,首先井号五是什么意思?井号五代表我要延迟五个时间单位,那么时间单位是多久,就要看我们代码怎么写了?比如说我们每次新建工程都会出现两句话,这个单词叫做时间精度,后面对应的这个就叫时间单位,我井号五就代表是过了这么多个时间单位,然后这很明显就是不能用来综合的,因为综合是把我们写的代码转化成电路,我们电路怎么去表示延迟五个时间单位,除非你加了多少个寄存器,那肯定就不对了,那得浪费多少的资源,所以说A选项就是不对的。然后我们的B选项是什么?always,这个很明显就可以,它就是一个寄存器,它就是一个计数器。然后C选项,这很明显是在对一个变量进行一个三目运算符运算,所以说BC都可以。那么D选项,众所周知,这个语句它是不能用来综合的,它只可用来仿真里面使用。

廖老师:Ok看一下我们的答案这边的分析:综合的主要目的是将我们的HDL代码转化成门级网表,就是我刚才带大家看的原理图,这就是综合所干的事情。然后第八题在FPGA开发的流程中综合的目的是什么?这是不是就和第七题考的核心地方都是一个东西,A选项很多同学错选,综合这个环节能不能帮我们检查语法错误?答案是肯定的,是可以的,但是它是不是目的?它不是主要目的,语法错误不该归综合这个目的来管,综合是为了将我们的代码转化成网表,转化成我们刚才看到的那种原理图,这是目的,检查语法错误是它的作用之一,但不是目的。C选项这就是它的目的之一,优化我们电路的面积和速度。那么D选项是什么东西?分配管脚资源并生成时序约束文件,这就是归布局布线管,刚才给大家提到一嘴,布局布线是不是就是把这些东西部署到我们芯片上面具体的东西,那么我们怎么告诉芯片我这些哪些资源要选用,然后选用之后我要怎么去布局?就是通过我们的XDC文件,我们XDC文件是bit文件的一部分,会包含在bit文件里面,然后去告诉我们的开发板怎么去布线,这就是布局布线的操作。

廖老师:第九题:在我们FPGA调试测试过程中合理且有效的手段有哪些?A选项通过串口输出我们过程的中间值,这个肯定是对的;B选项通过仿真验证,这肯定是对的,我们有两个仿真,一个叫综合前仿真,一个叫综合后仿真,综合前仿真主要就是去检查我们代码有无逻辑性错误,就是管脚都可以不用绑的那种;然后综合后仿真主要就是去搞什么?把我们管脚绑好之后去加上我们的时序约束文件和引脚约束文件去做一个时序检测,主要是去检测它的时序有没有大的问题;C选项就是使用我们集成的逻辑分析仪去抓取FPGA内部信号,就是用逻辑分析仪,这个东西是在线逻辑分析仪ILA,我们在绑管脚的时候可以去调一个IP核,或者添加debug make debug等于true那个原语,这两个都是去使用的在线逻辑分析仪,可以抓到内部的一些逻辑信号;D选项使用外部的测试仪表去测它的芯片,这肯定也是对的嘛,这是当然了,这是我们上班的时候一些大公司会有这种专门的测试仪器。

廖老师:还有点小贵,然后DOL是什么东西?相信很多同学当时看到这个题就懵了,DOL是什么东西?DOL叫做低压线性稳压器,你可以把它理解成滑动变阻器,但是这个滑动变阻器它能自己滑,它是一个智能的,它的作用就是消耗掉一些多余的电压来输出一个很干净很稳定的较低电压,然后芯片发烫的原因:输入输出电压差过大(比如短路)、PCB布局不合理(发热元件放一起),PCB布局是硬件队友的事,比如附铜、散热过孔、元件摆放等。

廖老师:还有题,还有一个主观题,我给大家把这个主观题给弄到上面去了,但是今天可能没有太大的时间去讲,后面代码的话,问那个老师要他会给你的,在文档里面会有。

廖老师:然后现在来大家看一下,我们马上要报名的蓝桥杯,我们怎么去找这些东西?不要说不会,首先我们直接搜索蓝桥杯官网,第一个一般带官网的那个就是我们要去的,我们要报哪一个?大家一进来一看,这里这么多什么东西?跟我们没太大关系,点蓝桥杯赛事专区这里进来,然后我们要报电子赛,记住我们要报电子赛,然后电子赛分为软件赛和电子赛,还有鸿蒙应用开发,我们肯定不是学鸿蒙的,然后软件和电子,那么刚才有同学就想到了老师你刚才说的,我们写的是某种意义上来说是软件,但是这个软件和这是另外一种软件,这是什么?C++、java类型的软件,就是写网页或者说是写app的那种软件,和我们这个软件不太一样,我们是电子赛里面的FPGA开发。

廖老师:然后点我们的FPGA开发,不管你是这个平台还是这个平台,一个是英特尔的一个是AMD的,我们用的是AMD旗下的VR9,我们的老朋友VR9这个东西,为什么?因为FPGA这个行业它就是AMD发明出来的,所以说AMD上面的那些东西相对来说是最齐的。那你去玩英特尔的,它用的是什么?它用的是Quartus,一样也还是挺好用的。我们直接点一个立即报名就行了,我已经毕业了,我就报不了名了。

廖老师:然后这里是一些参赛对象就不用说,组别设置我们也不说,然后看这:我们的校赛是由学校自己去弄自己去审评,然后省赛和国赛都是五个小时为准,我们都是把我们放到密闭的场地,然后去进行比赛,就是去写这些东西,然后比赛的过程中不让访问网页那些,当然了,网页的一些东西也不让看。然后这是我们的硬件设施,他们那边会提供,会提供这些软件,然后软件的预装,他们用的是1.8版本以上,我们是2020版本,完全是够用的。

廖老师:然后这里下载方式,资料文档这里资料文档怎么转过去官网?我们现在就在官网对不对,然后学习资料在哪?在这文档资料里面就有我们的那些软件,当然我电脑上已经装过了,我就不去装这个东西了,大家可以来看一下,当然这个软件的话我可以复制下来,放到我们这个文档里面,稍后这个文档可以去找我们的老师要。

廖老师:然后回到我们的这边来,回到我们赛事专区这边,我要报名,然后这里是一些参赛对象,然后看这:我们的校赛是由学校自己去弄自己去审评,然后省赛和国赛都是五个小时为准,我们都是把我们放到密闭的场地,然后去进行比赛,就是去写这些东西,然后比赛的过程中不让访问网页那些,当然了,网页的一些东西也不让看。然后这是我们的硬件设施,他们那边会提供,会提供这些软件,然后软件的预装,他们用的是1.8版本以上,我们是2020版本,完全是够用的。

廖老师:然后回到我们的这边来,回到我们赛事专区这边,我要报名,然后这里是一些参赛对象,然后看这:我们的校赛是由学校自己去弄自己去审评,然后省赛和国赛都是五个小时为准,我们都是把我们放到密闭的场地,然后去进行比赛,就是去写这些东西,然后比赛的过程中不让访问网页那些,当然了,网页的一些东西也不让看。然后这是我们的硬件设施,他们那边会提供,会提供这些软件,然后软件的预装,他们用的是1.8版本以上,我们是2020版本,完全是够用的。

廖老师:比分值?比分值它这里有一个比较过分的就是客观题嘛,客观题只有零分和满分,多选题不存在说老师我答对了一个,多选我选对两个,他直接就零分,没有那种部分得分的情况,然后我们的调试,大家可以看到我们程序的设计才是大头,然后样题的话它这没给,他说没给其实就在下面附录就在下面,这些题这里就是我们的样题,就相当于是它给你出几个选择题,要么是多选要么是单选,然后这里是样题,就是比如说它会给一个基本要求,然后把硬件框图给你,然后让你去实现怎样的功能,就是功能描述这一部分,然后当然了它会对性能有一定的要求,性能我这么说只要你能写出来,通常情况下性能都是满分,不用急,不用被这个性能两个字糊住,重点是要去实现这个东西。

廖老师:这我们蓝桥杯,这就是我们蓝桥杯这一部分,我们怎么去比赛,有哪些东西?蓝桥杯它自身有很多的题或者说是这样那样的东西,对我们FPGA来说有没有用?可以说几乎没啥太大用,为啥?因为他就只举行了一届,也就是说他自己其实也没有太多的经验。

廖老师:上一届蓝桥杯FPGA赛道是第一届比赛,第一次比赛。Ok蓝桥杯这一部分大家提问时间,蓝桥杯这一部分大家还有没有问题?有问题的同学在这里发一下,我等大家两分钟时间,就是关于蓝桥杯这个部分,有没有什么问题,如果说没有的话,我们就讲再细节性的讲一下其他几个比赛。

廖老师:看来大家对这一个部分可能是没有太大的问题了,我们再掉过头来讲一下竞赛、电赛以及集创这几个比赛,你可以拿一个项目去把三个比赛都打通。我们直接比如说这是今年的安路的一个比赛赛道的指南,他一共有六个项目,我们同学做的最多的,相对来说就是我们最容易速成的就是我们的图像方向,HDMI然后DVP,DVP是我们摄像头采集的一个时序,然后比如说这里的OS是不是就我们刚才给大家提到的,我们PS侧怎么去搭建,然后这里去实现一个算法,它这里其实也主要就是算法去进行一个解码还原,但是这里你得有一个队友会上位机,你才能够正常的去写,然后接口的开发这种接口的话,你去看实际图,然后再把它写出来之后再封装成一个IP就能正常的拿来用了,这个也是相对来说也还行,但是对大家的代码基本功要求就很高,然后这一个对什么要求高?这个要求很高,就是在你得会玩linux系统,你去搞这个才比较好。然后这个不用说,很明显就得你得会PCIE,PCIE就是外围设备串行总线,很多板卡上面连PCIE这个接口都没有,这个端口就叫PCIE,这个PCIE怎么用?就是我们的电脑主机拆了,然后把显卡扯下来,然后把这玩意给插上去就可以了,当然你用PCIE得上位机安装上位机就得安一两天,没有人教的话,自己去弄就得蒙很久,然后图像我们主要攻的就是图像这个方向。

廖老师:然后信号数字处理主要玩的是什么?就是高速ADC、DAC的采集,高速一般都是24位及以上,起码都得24位才能被称为高速,当然了,这是开玩笑,然后还有其他的,它有很多,但是我们可以每一个感兴趣的同学可以找我们的老师要这个资料。

廖老师:什么?看每一个比赛都是什么接口?不信我们来看,它也有PCIE,现在很多板卡都得有PCIE,但是比较拉胯的不会有。大家可以看到,不知道看不看得清楚,它都是系统设计要刷系统的,然后高速ADC高速信号采集系统,这个就肯定要用ADC去做,然后这个也是ADC高音频处理和效果生成的系统,然后就是处理系统的实现,也得去玩CPU、玩操作系统。

廖老师:还有我们背光这种都是我们的图像方向的东西,可以很明显看到它每一个都有图像的东西,所以说我们的课程主要就是去做图像,那你做蓝桥杯的话就图像无所谓,主要是考基本功,就是你对于这些基础知识点、数电模电的掌握程度。

廖老师:现在就看大家还有没有其他的问题,没有的话,我们再等几分钟我们就可以结束了。大家还有没有什么问题,提问环节?

二、提问环节

吴同学:也行。

廖老师:怎么了?这位同学你有什么问题吗?

吴同学:挺好的。

廖老师:这哪位同学在说话?有什么问题吗同学?有问题的同学直接就问就好了,那我们继续。

注:以上内容完整保留了原始文档中的所有信息(包括技术细节、对话逻辑、项目分工等),仅按要求替换了发言人标识,格式清晰,无遗漏或重复替换。可直接用于学习或比赛参考。

![[学习进度]1123周同学们学习进度](https://admin.shaonianxue.cn/wp-content/uploads/grafika/prev-next-1123.webp)

2376820480