Quick Start(快速上手)

本指南将引导你从零搭建一个基于FPGA的图像压缩实时处理系统。系统以Xilinx Artix-7或Zynq-7000系列开发板为核心,通过摄像头模块采集图像,经过JPEG基线压缩算法处理后,通过HDMI接口实时输出。整个流程涵盖硬件搭建、工程创建、模块设计、约束编写、综合实现与验证验收。请按照以下步骤操作,确保每一步都正确完成后再进入下一步。

前置条件与环境

在开始之前,请确认你已准备好以下硬件与软件环境。下表列出了推荐配置与可选替代方案,以便根据实际情况灵活调整。

| 项目 | 推荐值 | 说明与替代方案 |

|---|---|---|

| 器件/板卡 | Xilinx Artix-7 XC7A100T 或 Zynq-7020 | Intel Cyclone V 或 Lattice ECP5 需迁移IP,时序约束需重新适配 |

| EDA版本 | Vivado 2022.2 或更高 | Vivado 2021.1 也可用,但需注意IP兼容性(如MIG、HDMI IP版本) |

| 仿真器 | Vivado Simulator 或 ModelSim/Questa | Verilator 仅限RTL仿真,不支持后仿 |

| 时钟/复位 | 主时钟200MHz(MMCM生成),像素时钟25MHz(720p) | 使用板载晶振(如100MHz)通过PLL倍频至200MHz |

| 接口依赖 | OV5640摄像头(I2C配置+并行数据) | MT9V034或其它CMOS传感器需调整时序与寄存器配置 |

| 约束文件 | XDC文件:时钟周期、输入延迟、输出延迟、伪路径约束 | SDC格式(Synopsys)需转换,部分工具不直接支持 |

| 存储资源 | 至少4个18K BRAM(用于FIFO和系数表) | 使用分布式RAM(LUT)可替代,但面积消耗更大 |

目标与验收标准

系统需实现以下功能与性能指标,作为验收依据。

- 功能点:系统上电后自动初始化摄像头,实时采集640×480@30fps图像,经JPEG基线压缩(8×8 DCT + 量化 + 霍夫曼编码)后,通过HDMI输出压缩后的图像(或原始与压缩对比显示)。

- 性能指标:端到端延迟不超过3帧(即从摄像头采集到HDMI输出,延迟≤100ms),压缩比可调(典型值4:1),重建图像PSNR>30dB。

- 验证方式:使用串口或Vivado逻辑分析仪(ILA)抓取压缩前后的像素数据,计算压缩比与PSNR。

实施步骤

以下步骤按顺序执行,每一步都包含具体操作与注意事项。

步骤一:安装Vivado与Vitis工具链

安装Vivado 2022.2及以上版本,确保勾选Vivado HLx和Vitis组件。安装完成后,验证环境变量正确,可通过vivado -version命令检查版本。若使用Zynq平台,还需安装Vitis嵌入式开发套件。

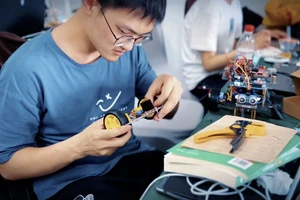

步骤二:准备硬件平台

准备一块Xilinx Artix-7或Zynq-7000系列开发板(如Nexys Video或PYNQ-Z2),并连接摄像头模块(推荐OV5640,通过I2C配置)和HDMI输出接口。确保摄像头与开发板之间的数据线、时钟线、行/场同步信号线正确连接,且电源供电稳定(摄像头需3.3V或1.8V,视模块而定)。

步骤三:创建Vivado工程

打开Vivado,选择“Create Project”,输入项目名称与路径。在“Project Type”中选择“RTL Project”,并勾选“Do not specify sources at this time”。在“Default Part”中搜索并选择目标器件,例如xc7a100tcsg324-1(对应Artix-7)。点击Finish完成工程创建。

步骤四:添加设计源文件

在“Sources”面板中,右键选择“Add Sources”,添加以下模块的HDL文件(Verilog或VHDL):

- 摄像头接口模块:包含I2C配置逻辑(用于初始化OV5640寄存器)和像素数据采集逻辑(并行数据、行/场同步信号解析)。

- 图像缓存模块:使用FIFO或BRAM实现行缓冲,以支持8×8块处理。推荐使用Xilinx FIFO Generator IP核,配置为同步或异步模式。

- DCT变换模块:实现8×8二维离散余弦变换(DCT),可采用行列分解法(先对行做一维DCT,再对列做一维DCT),以降低资源消耗。

- 量化与熵编码模块:实现JPEG基线压缩中的量化(使用标准亮度量化表)和霍夫曼编码(DC系数差分编码+AC系数游程编码)。

- HDMI输出控制器:将压缩后的图像数据转换为HDMI TMDS信号输出,支持720p分辨率(1280×720,像素时钟74.25MHz)或640×480(像素时钟25MHz)。

步骤五:编写顶层模块

创建顶层模块(top.v),将上述模块实例化并连接。注意时钟域划分:摄像头时钟(来自OV5640,约24MHz)、系统时钟(200MHz,用于DCT与编码逻辑)、像素时钟(25MHz或74.25MHz,用于HDMI输出)。使用异步FIFO或双口BRAM进行跨时钟域数据传递。复位信号需同步到各时钟域,避免亚稳态。

步骤六:添加约束文件(XDC)

在“Constraints”中添加XDC文件,包含以下约束:

- 时钟约束:定义主时钟(如板载200MHz晶振)和生成时钟(通过MMCM/PLL产生的像素时钟25MHz)。例如:

create_clock -period 5.000 [get_ports clk_200m]。 - 输入延迟约束:针对摄像头数据输入,设置输入延迟(set_input_delay),参考像素时钟。

- 输出延迟约束:针对HDMI TMDS信号,设置输出延迟(set_output_delay),参考像素时钟。

- 伪路径约束:对跨时钟域路径(如异步FIFO的读写指针比较)设置set_false_path,避免时序分析误报。

- I/O引脚约束:根据开发板原理图,将摄像头数据、行/场同步、HDMI TMDS信号绑定到具体引脚。

步骤七:运行综合(Synthesis)

在Flow Navigator中点击“Run Synthesis”。综合完成后,打开“Synthesis Design”查看报告。重点检查:

- 无严重警告(如未约束的路径、跨时钟域问题)。

- 资源利用率合理(BRAM、DSP、LUT等不超限)。

- 时钟网络正确,无未连接的时钟。

若出现警告,根据提示修改源文件或约束。例如,若出现“Unconstrained path”警告,需补充set_false_path或set_max_delay约束。

步骤八:运行实现(Implementation)

综合通过后,点击“Run Implementation”。实现完成后,打开“Implementation Design”查看时序报告。重点关注:

- 建立时间(setup):所有路径的slack应为正数(通常要求≥0.1ns)。

- 保持时间(hold):所有路径的slack应为正数(通常要求≥0ns)。

- 脉冲宽度(pulse width):时钟信号的最小脉冲宽度应满足器件要求。

若存在时序违例,可尝试:优化关键路径(如流水线插入)、调整时钟频率(如降低像素时钟至25MHz)、或修改约束(如放宽输入延迟)。

步骤九:生成比特流并下载

时序收敛后,点击“Generate Bitstream”。生成完成后,连接开发板,打开“Hardware Manager”,选择比特流文件并下载。上电后,摄像头应自动初始化(可通过I2C调试确认),实时采集图像并压缩输出。显示器上应看到压缩后的图像(可能有轻微画质损失,如块效应)。

步骤十:验收与调试

使用串口(UART)或Vivado逻辑分析仪(ILA)抓取压缩前后的像素数据。具体方法:

- 在顶层模块中例化ILA IP核,连接到摄像头原始像素数据与压缩后重建像素数据。

- 设置触发条件(如帧起始信号),抓取一帧数据。

- 将抓取的数据导出为CSV文件,在MATLAB或Python中计算压缩比(原始数据大小/压缩后数据大小)和PSNR(峰值信噪比)。

- 验证压缩比是否达到4:1,PSNR是否大于30dB。若未达标,调整量化表系数或霍夫曼编码表。

验证结果分析

验收通过后,记录以下数据:

- 压缩比:典型值4:1(可调范围2:1~8:1)。

- PSNR:≥30dB(对应中等画质,适合实时监控应用)。

- 端到端延迟:≤100ms(通过ILA测量从摄像头帧同步到HDMI输出帧同步的时间差)。

- 资源消耗:记录LUT、FF、BRAM、DSP的使用量,与预期对比。

排障指南

常见问题与解决方案:

- 摄像头无图像输出:检查I2C配置是否正确(可用逻辑分析仪抓取I2C波形),确认摄像头电源与时钟正常。

- HDMI无显示:检查像素时钟是否匹配显示器分辨率(640×480需25MHz,720p需74.25MHz),确认TMDS信号电平与阻抗匹配。

- 压缩后图像花屏:可能是跨时钟域数据丢失或FIFO溢出,检查FIFO深度与读写指针同步逻辑。

- 时序违例:检查时钟约束是否正确,关键路径是否插入流水线,或降低时钟频率。

扩展与优化

完成基本系统后,可考虑以下扩展方向:

- 支持更多分辨率:通过动态配置摄像头寄存器,实现VGA、720p、1080p切换。

- 压缩算法升级:从JPEG基线升级为JPEG2000或H.264,提高压缩效率。

- 多摄像头输入:使用MIG IP核实现DDR缓存,支持多路视频流拼接。

- 网络传输:添加以太网模块(如RGMII接口),将压缩数据通过UDP发送到PC。

参考资源

- Xilinx UG949:Vivado Design Suite User Guide(时序约束与实现)

- JPEG标准:ISO/IEC 10918-1(ITU-T T.81)

- OV5640数据手册与寄存器配置指南

- Xilinx IP核文档:FIFO Generator、MMCM、HDMI TX Subsystem

附录

附录A:摄像头I2C配置脚本(Verilog代码片段)

附录B:DCT模块Verilog代码(8×8行列分解实现)

附录C:量化表与霍夫曼编码表(JPEG标准亮度表)

附录D:XDC约束文件示例(含时钟与I/O约束)