对于具备数学与物理背景的学习者而言,理解FPGA设计的核心——时序与并行计算——并非从零开始。您的学科训练已赋予您强大的抽象思维、模型构建与系统分析能力。本指南旨在引导您将这些思维优势,转化为理解硬件描述语言(HDL)与数字系统设计的具体路径。我们将通过一个可执行的“两级流水线累加器”项目,让您直观感受时序与并行在硬件中的本质体现。

快速开始:构建流水线累加器

请按顺序执行以下步骤,快速建立工程并观察结果,获得第一手硬件操作体验。

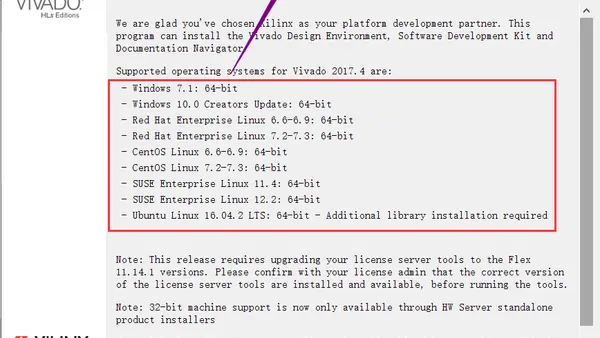

- 步骤1:环境准备。安装Vivado 2022.1(或更高版本)并获取有效的工具链许可证。

- 步骤2:创建工程。启动Vivado,创建新工程,选择目标器件型号为“xc7z020clg400-1”(或您开发板对应的型号)。

- 步骤3:添加设计文件。新建一个Verilog源文件,命名为

pipelined_accumulator.v。 - 步骤4:编写核心RTL。将下文“实施步骤”中“阶段二:关键模块 - 两级流水线累加器”的完整代码复制到该文件中。

- 步骤5:添加测试平台。新建一个Verilog测试文件(Testbench),命名为

tb_accumulator.v,复制“验证与结果分析”小节中的测试代码。 - 步骤6:运行行为仿真。在Vivado中,将

tb_accumulator设置为顶层仿真模块,点击“Run Simulation → Run Behavioral Simulation”。 - 步骤7:观察波形。在仿真波形窗口中,添加所有信号。您应能看到输入数据

din在每个时钟上升沿变化,而输出dout和dout_valid会延迟两个时钟周期后出现,且dout是连续三个din值的和。这正是“流水线延迟”与“并行计算”的直观体现。 - 步骤8:综合与实现。关闭仿真,将

pipelined_accumulator设置为顶层设计模块,依次运行“Synthesis”和“Implementation”。 - 步骤9:查看时序报告。实现完成后,打开“Timing Report”,查看“Worst Negative Slack (WNS)”。一个正值(如 > 0.2 ns)表示时序收敛,您的设计能在指定时钟频率下稳定工作。

- 步骤10:查看资源报告。打开“Utilization Report”,查看“Slice LUTs”和“FFs”的消耗量。理解面积(资源)与速度(时序)的权衡自此开始。

前置条件与环境配置

| 项目 | 推荐值/说明 | 替代方案与注意点 |

|---|---|---|

| FPGA器件/开发板 | Xilinx Zynq-7000系列 (如 xc7z020) | 任何具备足够逻辑资源的Xilinx 7系列、UltraScale系列,或Intel (Altera) Cyclone V/10系列。核心原理相通。 |

| EDA工具 | Xilinx Vivado 2022.1 | Vivado 2018.3及以上版本均可。Intel器件请使用对应的Quartus Prime。 |

| 仿真工具 | Vivado内置仿真器 (XSim) | Modelsim/QuestaSim,或开源工具如Verilator(需额外配置)。 |

| 设计语言 | Verilog HDL (IEEE 1364-2005) | SystemVerilog (IEEE 1800-2017) 是更强大的超集,推荐后续学习。 |

| 时钟与复位 | 单时钟域,同步高电平复位 | 本示例假设时钟频率100MHz(周期10ns)。复位信号需在约束文件中正确定义。 |

| 关键约束文件 (.xdc) | 需创建,至少包含时钟和复位引脚定义 | 约束是硬件设计的“物理定律”,必须准确。示例:create_clock -period 10 [get_ports clk] |

| 数学思维准备 | 理解离散系统、状态转移、流水线概念 | 将连续微积分思维转化为离散时钟沿思维。物理中的“传播延迟”可类比于“逻辑延迟”。 |

| 物理思维准备 | 能量最小化(资源优化)、信号完整性(时序)概念 | 将电路视为由门和连线组成的物理实体,信号传播需要时间,路径有长有短。 |

目标与验收标准

完成本指南后,您将实现并理解一个具体的硬件模块,并达到以下验收标准:

- 功能正确:设计一个两级流水线累加器,对连续输入的3个数据进行求和。输入

din每时钟周期变化一次,输出dout在输入第3个数据后的第2个时钟周期输出有效结果,并伴随一个周期的高电平有效信号dout_valid。 - 时序收敛:在100MHz时钟约束下,综合实现后的时序报告显示WNS > 0 ns(理想情况 > 0.2 ns),无建立时间(Setup)或保持时间(Hold)违规。

- 资源可量化:查看布局布线后的资源报告,记录消耗的查找表(LUT)和触发器(FF)数量,并与非流水线版本(见扩展思考)进行对比。

- 波形可验证:通过仿真波形,能清晰指出流水线的“填充”、“稳定流动”和“排空”阶段,并能准确计算输出延迟(Latency)和吞吐率(Throughput,本例为每周期1个新结果)。

实施步骤

阶段一:工程结构与模块定义

首先建立硬件描述的基本框架。一个Verilog模块类似于一个物理黑盒,定义了输入输出端口(引脚)和内部行为。

// pipelined_accumulator.v

module pipelined_accumulator #(

parameter DATA_WIDTH = 16 // 参数化数据位宽,体现数学中的“一般性”

) (

input wire clk, // 全局时钟信号 - 系统的“时间基准”

input wire rst_n, // 低电平有效复位信号 - 系统的“初始状态”

input wire [DATA_WIDTH-1:0] din, // 输入数据总线

output reg [DATA_WIDTH-1:0] dout, // 输出数据总线

output reg dout_valid // 输出有效标志

);

// 内部逻辑将在这里编写

endmodule常见问题与排查1:端口方向(input/output)声明错误。如果将一个本应是输入的端口声明为output,在顶层连接时可能报“多重驱动”或“端口不匹配”错误。请始终从模块内部视角思考信号流向。

常见问题与排查2:复位极性混淆。使用低电平复位(rst_n)时,条件判断应写为 if (!rst_n)。请确保测试平台中复位信号的初始值和触发极性与此严格一致。

阶段二:关键模块 - 两级流水线累加器

这是设计的核心,可以用数学中的“递推关系”和物理中的“流水线”模型来理解。我们需要计算 S = dint + dint-1 + dint-2。在硬件中,我们通过寄存器(触发器)来记忆“过去”的值,并通过多级流水线并行计算部分和。

// 在模块内部添加以下寄存器声明与逻辑

reg [DATA_WIDTH-1:0] din_r1, din_r2; // 两级数据寄存器,存储前两个时钟周期的输入值

reg [DATA_WIDTH-1:0] sum_stage1; // 第一级流水线寄存器:存储 din_r1 + din_r2 的中间结果

reg [DATA_WIDTH-1:0] sum_stage2; // 第二级流水线寄存器:存储最终累加和 sum_stage1 + din

reg [1:0] valid_cnt; // 一个简单的状态计数器,用于生成精确的 dout_valid

// 核心时序逻辑块

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

// 复位:将所有寄存器和输出置为初始状态(零)

din_r1 <= {DATA_WIDTH{1'b0}};

din_r2 <= {DATA_WIDTH{1'b0}};

sum_stage1 <= {DATA_WIDTH{1'b0}};

sum_stage2 <= {DATA_WIDTH{1'b0}};

dout <= {DATA_WIDTH{1'b0}};

dout_valid <= 1'b0;

valid_cnt <= 2'b00;

end else begin

// 流水线第一级:数据移位与部分和计算

din_r1 <= din; // 锁存当前输入,作为下一周期的“过去值1”

din_r2 <= din_r1; // 将“过去值1”移位为“过去值2”

sum_stage1 <= din_r1 + din_r2; // 并行计算前两个历史数据的和

// 流水线第二级:完成最终累加并输出

sum_stage2 <= sum_stage1 + din; // 将当前输入与第一级部分和相加

dout <= sum_stage2; // 输出最终结果

// 有效信号生成逻辑:在流水线充满后(第3个数据输入开始),每个周期输出有效

if (valid_cnt == 2'b10) begin

dout_valid <= 1'b1;

end else begin

valid_cnt <= valid_cnt + 1;

dout_valid <= 1'b0;

end

end

end机制分析:此设计将三数累加这个组合逻辑拆分为两级。第一级在一个时钟周期内并行计算 din_r1 + din_r2,第二级在下一个周期计算该结果与当前 din 的和。这降低了单级组合逻辑的延迟(有利于提高时钟频率),并实现了每时钟周期吞入一个新数据、吐出一个新结果的流水线吞吐率。延迟(Latency)为2个时钟周期。

验证与结果分析

为验证设计功能,需要编写测试平台(Testbench)施加激励并观察响应。

// tb_accumulator.v

`timescale 1ns / 1ps

module tb_accumulator();

parameter DATA_WIDTH = 16;

parameter CLK_PERIOD = 10; // 100MHz时钟,周期10ns

reg clk;

reg rst_n;

reg [DATA_WIDTH-1:0] din;

wire [DATA_WIDTH-1:0] dout;

wire dout_valid;

// 实例化被测设计 (DUT)

pipelined_accumulator #(

.DATA_WIDTH(DATA_WIDTH)

) uut (

.clk(clk),

.rst_n(rst_n),

.din(din),

.dout(dout),

.dout_valid(dout_valid)

);

// 时钟生成

initial clk = 0;

always #(CLK_PERIOD/2) clk = ~clk;

// 测试激励

initial begin

// 初始化与复位

rst_n = 0;

din = 0;

#(CLK_PERIOD*2); // 保持复位两个周期

rst_n = 1;

#(CLK_PERIOD);

// 施加连续输入数据流,例如:1, 2, 3, 4, 5...

din = 16'd1;

#CLK_PERIOD;

din = 16'd2;

#CLK_PERIOD;

din = 16'd3;

#CLK_PERIOD;

din = 16'd4;

#CLK_PERIOD;

din = 16'd5;

#(CLK_PERIOD*5); // 多观察几个周期

$finish;

end

// 波形输出(可选,用于某些仿真器)

initial begin

$dumpfile("tb_accumulator.vcd");

$dumpvars(0, tb_accumulator);

end

endmodule运行仿真后,在波形窗口中应观察到:

- 复位释放后,

din依次为 1, 2, 3, 4, 5。 - 输出

dout_valid在前两个时钟周期为低,从第三个时钟周期开始变为高电平并持续。 - 输出

dout在din=3输入后的第2个周期(即看到din=4的同一周期)首次有效,其值应为 1+2+3 = 6。随后依次输出 2+3+4=9, 3+4+5=12。

这清晰地展示了流水线的延迟特性与稳定的吞吐能力。

常见问题与故障排除

- 仿真无波形或信号为“X”(未知态):检查测试平台中时钟和复位信号是否正常生成;确认被测模块所有寄存器在复位时都被赋予了明确的初始值。

- 时序报告WNS为负值:表示设计无法在100MHz下工作。可能原因是组合逻辑路径过长。对于本设计,可尝试:1) 检查加法器是否被推断为多级逻辑;2) 使用寄存器打拍进一步分割关键路径;3) 降低约束时钟频率。

- 资源消耗异常高:如果LUT使用量远大于预期,可能是综合工具未识别出共享的加法器逻辑。检查代码风格,确保算术运算在明确的时序块中,避免在多个always块或组合逻辑中对同一变量进行赋值。

扩展思考与实践

- 对比实验:实现一个非流水线的组合逻辑累加器(在一个always @(*) 块中计算 dout = din + din_r1 + din_r2),并比较两者在时序(最高工作频率)和资源(LUT/FF用量)上的差异。体会“面积换速度”的经典权衡。

- 参数化探索:修改

DATA_WIDTH参数(如改为 8 或 32),重新综合,观察资源报告的变化。理解数据位宽对硬件资源的直接影响。 - 流水线深度调整:尝试设计一个三级流水线累加器(计算连续4个数的和)。分析其延迟、吞吐率以及硬件结构的变化。

- 数学思维延伸:将此累加器视为一个离散时间系统,尝试写出其输入输出的差分方程,并与代码中的寄存器传输级(RTL)描述进行对应。

参考与进一步阅读

- IEEE Standard for Verilog Hardware Description Language (IEEE Std 1364-2005).

- Xilinx. Vivado Design Suite User Guide: Synthesis (UG901).

- 数字设计中的基本概念:时钟、复位、建立/保持时间、流水线、吞吐率与延迟。

附录:关键术语对照

- RTL (Register Transfer Level):寄存器传输级,一种描述同步数字电路硬件行为的设计层次。

- WNS (Worst Negative Slack):最差负裕量。时序分析的关键指标,正值表示满足时序要求。

- LUT (Look-Up Table):查找表,FPGA中实现组合逻辑的基本单元。

- FF (Flip-Flop):触发器,用于存储1位二进制数据的时序逻辑单元,是构成寄存器的基本元件。