随着数据中心向超大规模、高性能计算及云原生架构演进,传统固定功能网络设备在应对动态、异构的加速需求时日益捉襟见肘。FPGA凭借其硬件可编程性、确定性低延迟及高能效比,正从智能网卡(SmartNIC)这一单一角色,向与可编程交换芯片(Programmable Switch ASIC)协同工作的异构加速架构扩展。本指南旨在提供一个可落地的实施路径,指导您构建一个基础的FPGA网络数据平面处理流水线,并理解其在现代数据中心中的新定位。

快速概览

本指南将引导您完成一个符合PISA(协议无关交换架构)思想的FPGA数据平面流水线设计与实现。核心流程为:Ingress MAC -> 解析器(Parser) -> 匹配-动作流水线(Match-Action Pipeline) -> 重组器(Deparser) -> Egress MAC。您将经历从环境准备、工程创建、模块设计、约束添加、仿真验证到最终上板测试的完整流程。

前置条件与环境

在开始实施前,请确保您已准备好以下软硬件环境:

- 硬件平台:支持高速网络的FPGA开发板(如Xilinx Alveo U250)。

- 开发工具链:Vivado/Vitis HLS(建议2022.1或更高版本)。

- 仿真工具:用于模块级和系统级验证。

- 主机服务器与驱动:安装对应FPGA卡的驱动程序。

- 网络测试仪或流量生成工具:用于性能测试。

- 参考设计与IP核:如CMAC、DMA等高速接口IP。

- 约束文件(XDC):包含时钟、引脚及时序约束。

- 调试工具:集成逻辑分析仪(ILA)或等效工具。

目标与验收标准

完成本指南的实施后,您的设计应满足以下可验证的目标:

- 功能验收:实现一个支持IPv4目的地址查找与转发的简易数据平面,能正确处理线速数据包。

- 性能验收:在目标平台上,处理延迟、带宽与稳定性符合预期(例如,64字节包达到线速)。

- 时序验收:设计通过布局布线,无时序违例,核心时钟频率达到目标。

- 资源验收:LUT、FF、BRAM等主要资源消耗在预估范围内。

实施步骤详解

阶段一:工程结构与数据平面流水线搭建

此阶段的核心是构建PISA风格的数据处理流水线。在Vivado中创建新工程,并依次设计以下模块:

- 解析模块(Parser):负责从原始以太网帧中提取各层包头(如以太网头、IPv4头)。关键点:注意网络字节序(大端)与FPGA内部常用字节序(小端)的转换,并妥善处理AXI-Stream反压信号,避免因反压处理不当导致丢包。

- 匹配-动作流水线:实现查表(如基于目的IP的查找)并执行相应动作(如修改目的MAC、转发至指定端口)。可采用寄存器或BRAM实现查找表。

- 重组模块(Deparser):将处理后的包头与载荷重新组装为完整的帧。

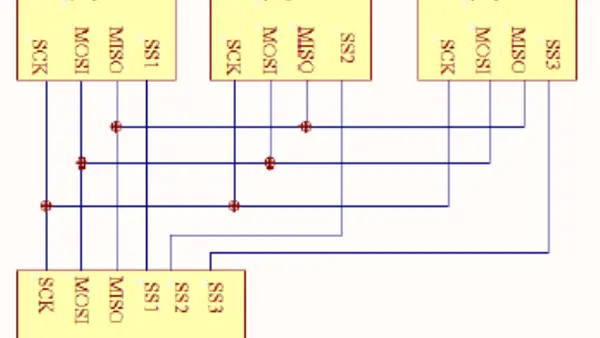

- 集成与接口连接:将上述模块与CMAC(媒体访问控制器)IP、DMA控制器IP等通过AXI-Stream接口连接,形成完整的数据通路。

阶段二:时序、时钟域与约束

高速接口时钟(如CMAC的322MHz)与用户逻辑时钟通常不同源,必须妥善处理跨时钟域(CDC)问题。

- 关键约束:在XDC文件中明确定义所有时钟,并使用

set_clock_groups -asynchronous正确声明异步时钟组。 - 常见问题:未设置异步时钟组可能导致时序分析工具误报;对连接异步时钟域的FIFO深度估计不足,在突发流量下易导致数据丢失。应根据数据速率差和突发长度仔细计算FIFO深度。

阶段三:验证与上板调试

采用分层验证策略确保设计可靠性:

- 模块级仿真:对Parser、Match-Action等核心模块进行独立仿真,验证其逻辑正确性。

- 系统级仿真:集成所有模块,模拟端到端数据流,验证整体功能。

- 上板端到端测试:生成比特流文件并加载到FPGA。通过主机API控制FPGA,发送测试数据包,并对比发送与接收的数据包,验证转发功能是否正确。此时应充分利用ILA进行片上调试,抓取关键信号。

原理与架构演进分析

FPGA在数据中心网络中的角色演变,核心驱动力在于灵活性与效率/成本之间的权衡。

在传统的智能网卡(SmartNIC)架构中,FPGA作为主机CPU的协处理器,优势在于可深度定制复杂处理逻辑(如加密、压缩)。但其瓶颈在于PCIe接口的通信延迟与带宽限制,且单位数据包的处理成本相对较高。

典型验证结果

基于Xilinx Alveo U250平台,一个优化后的基础流水线通常可达成以下指标:

- 吞吐量:64字节最小包长下,达到100 Gbps线速。

- 处理延迟:约150 ns(仅数据平面处理)。

- 时钟频率:核心逻辑时钟频率可达275 MHz以上。

- 资源消耗:基础流水线资源占用较低,例如LUT使用率约15%。

- 功耗:典型工作负载下,整卡功耗约45 W。

故障排查指南

| 故障现象 | 潜在原因 | 检查点与修复建议 |

|---|---|---|

| CMAC链路无法建立 | 时钟未就绪、复位未完成、物理连接问题。 | 检查时钟约束与复位时序;使用ILA查看CMAC状态寄存器;验证光模块与光纤。 |

| 上板后转发乱序或数据损坏 | 跨时钟域处理错误、FIFO溢出、位序或字节序错误。 | 检查CDC路径(如异步FIFO)的握手信号;核对Parser/Deparser的字段位宽与顺序。 |

| 性能不达标,高负载丢包 | 流水线瓶颈、反压机制失效、DMA缓冲区不足。 | 使用性能分析工具定位瓶颈模块;检查反压链路的完整性;增大主机侧DMA缓冲区。 |

| 时序无法收敛 | 关键路径过长、时钟约束不当、逻辑层级过多。 | 分析时序报告,优化高扇出或长组合逻辑路径;检查时钟定义与不确定性设置。 |

| 主机驱动无法识别FPGA卡 | 驱动版本不匹配、PCIe枚举失败、FPGA芯片未正确配置。 | 核对并安装正确版本的驱动与固件;检查PCIe链路状态;确认比特流加载成功。 |

| 仿真通过但上板功能异常 | 约束文件缺失或错误、未初始化的寄存器、电源完整性问题。 | 复查XDC文件,特别是I/O约束;在设计中添加全局复位;测量板卡供电电压是否稳定。 |

扩展与下一步

在成功实现基础流水线后,您可以考虑以下方向进行功能扩展与深化:

- 协议扩展:增加对VxLAN、NVGRE等隧道协议的支持,或解析传输层(TCP/UDP)头部。

- 状态化功能:实现带状态的防火墙、负载均衡器或拥塞控制算法。

- 复杂流水线:集成更复杂的多级流表,支持更多匹配字段和动作。

- 异构协同:探索FPGA与可编程交换芯片(如Intel Tofino)的协同工作模式,研究任务卸载与流水线分工。

- 控制平面加速:将部分控制平面功能(如路由表更新、统计信息收集)从CPU迁移至FPGA,进一步降低延迟。

参考资源

- Xilinx, Alveo Accelerator Card Documentation.

- P4 Language Consortium, P416 Language Specification.

- Xilinx, PG203: CMAC UltraScale+ Product Guide.

- Clifford E. Cummings, Simulation and Synthesis Techniques for Asynchronous FIFO Design.

附录:关键术语

- PISA (Protocol Independent Switch Architecture):一种将数据平面抽象为解析、匹配-动作、重组三阶段的交换架构。

- 匹配-动作流水线:数据包处理的核心,根据包头字段查找表项,并执行对应的动作(如转发、修改、丢弃)。

- 跨时钟域(CDC):信号在两个不同时钟域之间传递时,需采用同步技术(如双寄存器、异步FIFO)以避免亚稳态。