设计要求

一听饮料需要2.5美元,规定只能投入一美元,0.5美元的硬币。

设计架构

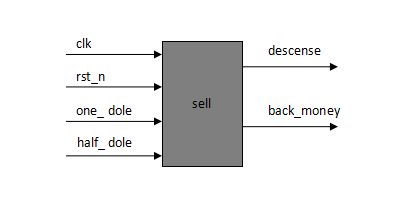

设计框架图:

设计代码

设计模块sell代码:

module sell(clk,rst_n,one_dole,half_dole,descense,back_money);

input clk;

input rst_n;

input one_dole; //输入1美元

input half_dole; //输入0.5美元

output reg descense; //是否买到的标志位

output reg [2:0] back_money; //找回的钱

parameter s0 = 2'b00,s1 = 2'b01,s2 = 2'b10;

reg [1:0] state;

reg [4:0] money;

reg [1:0] state_x;

always @ (posedge clk or negedge rst_n)

if(!rst_n)

begin

state_x <= s0;

end

else

begin

state_x <= state;

end

always @ (posedge clk or negedge rst_n)

if(!rst_n)

begin

money <= 5'b0;

state <= s0;

end

else

begin

case (state)

s0:begin

//判断投入的钱是多少

if(one_dole)

begin

money <= money + 10;

state <= s1;

end

else if(half_dole)

begin

money <= money + 5;

state <= s1;

end

else

begin

state <= s0;

money <= money;

end

end

//判断和商品的价格是否一样

s1:begin

if(money < 25)

begin

state <= s0;

end

else

begin

state <= s0;

money <= 5'b0;

end

end

endcase

end

reg [1:0] state_s;

always @ (posedge clk or negedge rst_n )

if(!rst_n)

begin

descense <= 1'b0;

back_money <= 3'b0;

state_s <= s0;

end

else

begin

case (state_s)

s0: begin

if(money < 25) //判断输入的钱数

begin

back_money <= 3'b0;

descense <= 1'b0;

end

else

//找回的钱和买到的标志位

begin

back_money <= money - 25;

descense <= 1'b1;

state_s <= s1;

end

end

s1: begin

descense <= 1'b0;

state_s <= s0;

end

endcase

end

endmodule测试仿真

测试模块sell_tb代码:

`timescale 1ns/1ps //时间精度

module sell_tb();

//定义我们的端口

reg clk;

reg rst_n;

reg one_dole;

reg half_dole;

wire descense;

wire [2:0] back_money;

initial begin

clk = 1'b1;

rst_n = 1'b0;

one_dole = 1'b0;

half_dole = 1'b0;

#200.1 rst_n = 1'b1;

//模拟输入的钱数

#200 one_dole = 1'b1;

#20 one_dole = 1'b0;

#200 one_dole = 1'b1;

#20 one_dole = 1'b0;

#200 one_dole = 1'b1;

#20 one_dole = 1'b0;

#1000.1

#200 half_dole = 1'b1;

#20 half_dole = 1'b0;

#200 one_dole = 1'b1;

#20 one_dole = 1'b0;

#200 one_dole = 1'b1;

#20 one_dole = 1'b0;

# 1000 $stop; //停止仿真

end

always #10 clk = ~ clk;

sell sell_dut( //例化端口

.clk(clk),

.rst_n(rst_n),

.one_dole(one_dole),

.half_dole(half_dole),

.descense(descense),

.back_money(back_money)

);

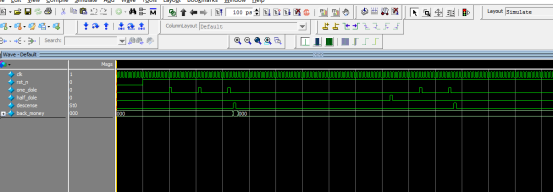

endmodule仿真图:

我们从仿真中可以看到当我们的钱数投够的时候,就给一个买到的标志位,如果投的超过商品的价格,那么我们就给一个买的标志位,然后找回我们投的多的钱。

用户_15381