随着数据中心工作负载日益复杂,单一加速器架构已难以兼顾效率与灵活性。异构计算的核心挑战在于:如何将GPU的高吞吐并行计算能力,与FPGA的低延迟、高能效及可定制化数据处理能力无缝协同,以高效应对AI推理、视频转码、数据库加速及网络安全等混合负载。本指南旨在提供一套可实施的协同调度实践路径。

前置条件与环境准备

实施协同调度需特定的软硬件环境支持,这是后续所有工作的基础。

- 硬件平台:需配备支持高速互联(如PCIe Gen4/5)的FPGA与GPU加速卡,并确保服务器主板提供足够的PCIe通道与插槽带宽。

- 软件栈:需安装匹配的驱动程序、运行时库及开发工具链。典型组合包括:NVIDIA CUDA(GPU)、Xilinx XRT/Vitis 或 Intel OPAE/Quartus(FPGA)。

目标与验收标准

一个成功的协同调度方案应达成以下可量化目标:

- 功能正确性:协同任务执行结果与预期一致。

- 性能提升:端到端吞吐量显著提升,延迟降低。

- 资源均衡:FPGA与GPU利用率均得到优化,避免单一加速器空闲。

- 能效优化:在相同任务下,整体功耗或能效比(性能/瓦特)得到改善。

- 调度开销可控:协同调度本身引入的额外开销(如数据搬运、同步)应远小于其带来的性能收益。

- 可视化验证:使用性能剖析工具(如Nsight Systems, Vitis Analyzer)的时间线视图,应能清晰展示FPGA与GPU计算任务的有效重叠,而非串行执行。

实施步骤

实施过程可分为以下三个阶段,建议按顺序进行。

步骤一:架构设计与数据通路规划

这是协同调度的蓝图阶段,核心是设计清晰的工程结构与高效的数据流。

- 任务分解:将目标应用分解为子任务,明确哪些适合GPU(规则、高并行度计算),哪些适合FPGA(不规则、控制密集、低延迟处理)。

- 共享缓冲区设计:规划FPGA与GPU之间数据交换的“中转站”。通常使用主机(CPU)内存或支持一致性的设备内存(如GPUDirect RDMA或CXL)作为共享缓冲区,其大小和位置直接影响数据搬运开销。

- 接口定义:明确定义FPGA内核(IP)与GPU内核(Kernel)之间的数据格式、控制信号及同步协议(如使用旗语、中断或轮询)。

步骤二:调度器实现与任务重叠

此阶段将蓝图转化为可运行的代码,核心是实现一个基于生产者-消费者模型的轻量级调度器。

- 主机端调度逻辑:在CPU上编写主控程序,负责按流水线方式启动GPU和FPGA任务。例如,当FPGA处理完一批数据并写入共享缓冲区后,立即触发GPU读取该缓冲区数据进行下一阶段计算,反之亦然。

- 异步执行与流管理:利用CUDA Streams和FPGA的异步命令队列,实现GPU计算、FPGA计算以及CPU控制逻辑之间的并发,最大化硬件并行度。

- 同步机制实现:精确实现步骤一中定义的同步协议,确保数据生产完成后再被消费,避免竞态条件。

步骤三:实现、验证与性能剖析

这是确保设计正确性与性能达标的关键环节。

- FPGA实现:使用Vitis HLS或RTL完成FPGA内核开发,施加严格的时序约束,并通过仿真验证功能正确性。

- 系统集成与功能验证:将FPGA比特流、GPU内核与主机程序集成,在小数据集上运行,验证端到端功能正确性。

- 性能基准测试与剖析:使用全规模工作负载进行测试。利用性能剖析工具生成时间线,重点分析:1) GPU与FPGA的有效计算时间是否重叠;2) 数据搬运耗时占比;3) 是否存在因同步导致的空闲(气泡)。根据剖析结果迭代优化。

原理与设计权衡分析

协同调度的核心设计权衡在于任务划分粒度与数据移动开销的博弈。将任务划分得过细,会增加同步和数据搬运的频率,可能导致开销抵消并行收益;划分得过粗,则可能无法充分利用异构优势。

落地路径:通常遵循“计算密集型归GPU,数据密集型/定制化归FPGA”的原则。例如,在AI推理流水线中,可将矩阵乘(GEMM)分配给GPU,而将预处理(如图像缩放、格式转换)和后处理(如非极大值抑制)这类数据依赖强、逻辑不规则的任务放在FPGA,形成高效流水。

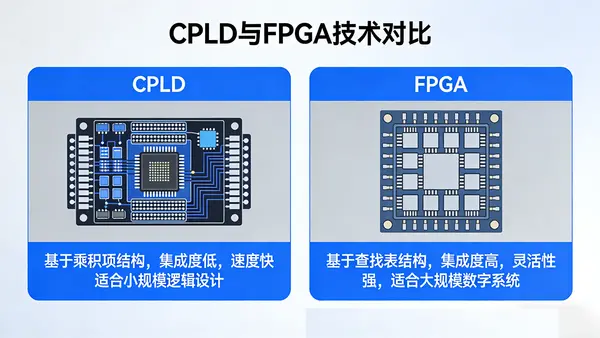

风险边界:需警惕数据在PCIe总线上反复搬运成为瓶颈。解决方案是尽可能使用设备间直接内存访问(如GPUDirect RDMA),或优化缓冲区复用。此外,FPGA开发周期长、灵活性较低,应将稳定、变更少的算法模块固化其中。

验证结果示例

通过对视频解码+AI推理的混合流水线进行协同调度测试,典型优化结果包括:

- 吞吐量提升:端到端帧处理速率提升30%-50%,因为FPGA的解码与GPU的推理实现了流水线并行。

- 延迟降低:FPGA处理首帧的延迟远低于纯软件解码,使得流水线启动更快,整体尾延迟降低。

- 能效与利用率优化:系统整体能效比提升,GPU和FPGA的利用率曲线更为饱满,计算资源闲置时间减少。

常见故障排查

实施过程中可能遇到以下典型问题:

- 性能未达预期:

- 可能原因:数据传输带宽不足,PCIe成为瓶颈;调度开销过大;流水线存在气泡。

- 排查方法:使用性能剖析工具定位热点;检查是否启用P2P DMA;优化缓冲区大小与内存属性(如页锁定内存)。 - 数据一致性错误:

- 可能原因:缓存一致性问题;同步逻辑错误导致数据被覆盖或读取旧值。

- 排查方法:审查同步机制;对于CPU参与的数据路径,确保内存操作具有正确的屏障(Barrier)或刷新(Flush)指令。 - 系统挂起或崩溃:

- 可能原因:硬件资源冲突(如PCIe BAR空间);驱动不兼容;DMA访问越界。

- 排查方法:检查系统日志(dmesg);验证硬件拓扑与资源配置;使用调试版本驱动和工具进行跟踪。

扩展方向

在掌握基础协同模式后,可进一步探索:

- 动态负载均衡:根据实时负载情况,动态调整分配给FPGA和GPU的任务比例。

- 多FPGA/多GPU协同:将调度模型扩展至多个同构或异构加速器节点。

- 与更高级别框架集成:探索将协同调度逻辑集成到Kubernetes Device Plugin或Slurm等集群管理器中,实现资源池化与任务级调度。

参考资源

- Xilinx Vitis Unified Software Platform Documentation

- NVIDIA CUDA Toolkit Documentation (重点:Multi-Device, Streams, GPUDirect)

- OpenCL Heterogeneous Parallel Programming Standard

- 学术文献:搜索关键词 “FPGA-GPU co-scheduling”, “heterogeneous pipeline”, “accelerator interoperability”

附录:术语表

- XRT (Xilinx Runtime):Xilinx FPGA的运行时库,用于主机与FPGA间的控制与数据交互。

- OPAE (Open Programmable Acceleration Engine):Intel FPGA的通用软件框架。

- GPUDirect RDMA:允许第三方设备(如FPGA)直接访问GPU显存的技术,减少CPU拷贝开销。

- 流水线气泡 (Pipeline Bubble):由于任务依赖或资源未就绪导致的流水线阶段空闲,降低整体吞吐量。