引言:为什么NoC是FPGA毕业设计的“宝藏选题”?

你有没有发现,现在的FPGA芯片越来越“胖”了?里面塞满了各种处理器核、加速器和控制器。这时候,老旧的“总线”通信方式就像一条拥挤的单车道,很容易成为性能瓶颈。

于是,片上网络(NoC)闪亮登场了!它把计算机网络的智慧搬到了芯片里,用“路由器”和“链路”组成一张高效的数据传输网,带宽高、延迟低,还能轻松扩展。

选择“从零搭建一个FPGA上的NoC”作为你的毕业设计,简直不要太酷!它不仅能让你彻底搞懂现代复杂芯片是怎么“聊天”的,还能全方位锻炼你的系统设计、代码编写、仿真调试和硬件实现能力。这个课题既前沿又硬核,绝对是电子、计算机、集成电路专业同学展示实力的绝佳舞台。

第一部分:目标锁定,找到你的核心战场

别想着一口吃成胖子。一个好的毕业设计,关键在于聚焦核心,在有限时间里做出一个能跑、能测、有深度的系统。下面三个方向,选一个你最感兴趣的切入吧:

- 方向一:搭建轻量级Mesh网络。 这是最经典的选择。你的目标是设计一个2x2或3x3的二维网格,里面包含路由器和网络接口。核心是搞定那个确定性的XY路由算法,并实现路由器内部的缓冲、计算、仲裁和交换功能。

- 方向二:设计AXI-Stream协议适配层。 想让你的NoC更实用、更能融入现有的FPGA生态吗?试试这个!你需要深入理解AXI-Stream协议,然后设计一个网络接口,负责把数据打包成NoC的格式发出去,再把收到的包解包还原回来,中间还要处理好流量控制。

- 方向三:性能评估与优化挑战。 在实现了一个基础版NoC之后,你可以把它当成一个实验平台。研究一下在不同数据流量(比如均匀随机、局部密集)下它的表现如何,然后尝试一些优化技巧,比如用“虚通道”来防止死锁,或者加入简单的优先级仲裁机制。

给你的核心目标建议: 无论如何,最终目标都是让你的NoC在FPGA开发板上“活”起来。比如,用几个软核处理器(像MicroBlaze或RISC-V)或者自己写的数据模块作为终端,让它们通过你的NoC传数据,并用板子上的LED、串口或者VGA把通信结果(像延迟、吞吐量)展示出来。看得见的效果,才是答辩时最有力的证明!

第二部分:动手实现,一步步拆解关键技术

怎么把一个复杂的NoC系统做出来?别慌,咱们自底向上,一步步来:

- 1. 定规矩:通信协议与数据包格式

这是整个系统的“宪法”。你得先把数据包长什么样定义清楚:包头(去哪、从哪来、什么类型)、有效载荷(数据本身)、包尾(比如校验码)。数据位宽通常和FPGA的存储器位宽对齐(比如32位或64位),这样效率更高。 - 2. 造核心:路由器(Router)设计

这是NoC的“交通枢纽”。一个典型的路由器包括:- 输入单元: 带缓冲队列(FIFO),临时存放到达的数据包。

- 路由计算单元: 查看包头的目标地址,用预设算法(比如XY路由)决定该从哪个口出去。

- 仲裁单元: 如果好几个入口都想从同一个出口出去,就得由它来裁决(比如轮流来或者谁优先级高谁先走)。

- 交叉开关: 根据仲裁结果,把数据从入口切换到对应的出口。

建议先用Verilog/VHDL写一个参数化的路由器模块(可以灵活配置数据位宽和缓冲深度)。

- 3. 建桥梁:网络接口(NI)设计

它是终端IP核和NoC网络之间的“翻译官”。负责把用户的数据(比如一个内存写请求)打包成NoC能识别的数据包扔进网络,同时从网络收包,解包后再交给用户逻辑。它还得处理好流量控制,可别把路由器的缓冲区给塞爆了。 - 4. 组网络:拓扑集成与终端设计

把多个路由器和网络接口按照Mesh网格连接起来。终端节点可以很简单:- 一个数据生成器:定期产生发往特定地址的数据包。

- 一个数据检查器:接收数据包,检查内容和顺序对不对,然后通过LED或串口报告状态。

想玩得更高级?可以集成一个软核处理器,跑个小程序,让它通过NoC去访问共享内存或者跟其他处理器“隔空对话”。

- 5. 验成果:仿真验证与FPGA实现

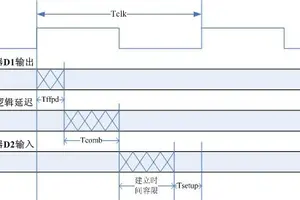

在把所有模块连起来之前,一定要对路由器、NI这些核心进行“地毯式”仿真测试,各种极端情况都试试。然后用Vivado或Quartus进行综合、布局布线,最后烧录到开发板上实测。遇到复杂的时序问题怎么办?别怕,片上逻辑分析仪(像Vivado的ILA)就是你最好的“侦探工具”,可以帮你抓取内部信号一探究竟。

第三部分:毕业答辩,如何惊艳全场?

答辩是展示你所有辛苦工作的关键时刻。围绕这几个要点来组织你的演讲,保证清晰又出彩:

- 1. 讲清背景与意义: 开门见山,说说传统总线为什么不够用了,NoC的优势在哪。结合AI加速、多核处理器这些热门应用,让大家明白你这个课题为什么重要、为什么酷。

- 2. 展示架构设计: 这是你的亮点!清晰地亮出你的系统整体框图、数据包格式定义、路由器内部结构图。别忘了解释你为什么选择特定的网络拓扑、路由算法和流控机制。

- 3. 深挖模块细节: 重点讲解路由器里路由计算、仲裁这些关键功能的状态机是怎么设计的,以及你是怎么用代码实现的。把关键模块的仿真波形图秀出来,用事实证明它们工作正常。

- 4. 呈现测试结果: 展示整个NoC系统的顶层连接图。然后,亮出最重要的两部分成果:

- 5. 总结难点与展望: 坦诚地聊聊项目中踩过的“坑”(比如遇到死锁、时序不满足),以及你是怎么爬出来的。最后,可以展望一下未来还能怎么改进,比如支持更智能的自适应路由、加入服务质量(QoS)机制、集成更复杂的AXI4接口等,这能体现你的思考深度。

成果展示小贴士: 准备一份逻辑清晰的设计报告,一个能直接打开跑的工程文件(Vivado/Quartus项目),再加一段1-2分钟的短视频,动态演示数据包在你的NoC里穿梭的过程(可以用仿真工具生成动画,或者用LED的扫描效果来模拟)。

结语

从零开始在FPGA上搭建一个NoC,这段旅程充满挑战,但回报绝对超值。它不仅能让你把数字逻辑、计算机体系结构、网络通信这些课程的知识串起来、用起来,更能让你获得一次贴近工业前沿的复杂系统开发实战经验。

成电国芯FPGA培训的课程体系,尤其是在高级数字系统设计、FPGA原型验证等方面,能为你的这场“硬核”之旅打下坚实的基础。祝你设计顺利,答辩时一鸣惊人!