半加器

module half_qwer(a,b,cout,sum);//半加器设计input a,b;output cout,sum;assign sum = a^b;assign cout = aendmodule

全加器

`timescale 1ns / 1psmodule qwe(a,b,cin,cout,sum);//一位input a,b,cin;output sum,cout;assign sum = a^b^cin;assign cout = (a&b)|(a&cin)|(bendmodule//四位全加器module asdfg(sum,cout,a,b,cin);input[3:0] a,b;input cin;output[3:0] sum;output cout;assign {cout,sum} = a+b+cin;endmodule================四位全加器仿真=================== initial begin // Initialize Inputs a = 0;b = 0;cin = 0;#100; // Add stimulus here repeat(10000) #100 {a,b,cin} = {a,b,cin}+1; end//八位全加器module qwer(a,b,cin,sum,cout);parameter SIZE = 8;input[SIZE-1:0]a,b;input cin;output[SIZE-1:0] sum;output cout;wire[SIZE:0] c;assign c[0] = cin;generate //for循环级联8位 genvar i; for(i=0;i<SIZE;i=i+1) begin : add qwe fi(a[i],b[i],c[i],sum[i],c[i+1]);//模块调用 endendgenerateassign cout = c[SIZE];endmodule

2-4译码器

module fgvh(A,Q);input[1:0] A;//两位输入output reg[3:0] Q;//四位输出always @(A)begin case(A) 2'b00 : Q[3:0] =4'b1110; 2'b01 : Q[3:0] =4'b1101; 2'b10 : Q[3:0] =4'b1011; 2'b11 : Q[3:0] =4'b0111; endcaseendendmodule=========================建议使用下面的方法=============================module qwe(A,Q);//2-4译码器 for循环input[1:0] A;output reg[3:0] Q;integer i;always @(A)begin Q = 4'b1111; for(i=0;i<=3;i=i+1) if(A==i) Q[i] = 0; else Q[i] = 1; endendmodule============================================================//仿真激励代码initial begin // Initialize Inputs A = 0; #100; forever begin A=A+1;#100;end end

3-8译码器

module sanba(A,Q);//3-8译码器 法一(不推荐)input[2:0] A;output reg[7:0] Q;always @(A)begin case(A) 3'b000:Q=8'b1111_1110; 3'b001:Q=8'b1111_1101; 3'b010:Q=8'b1111_1011; 3'b011:Q=8'b1111_0111; 3'b100:Q=8'b1110_1111; 3'b101:Q=8'b1101_1111; 3'b110:Q=8'b1011_1111; 3'b111:Q=8'b0111_1111; endcaseendendmodule======================推荐使用下面方法==========================module qwerttgy(A,Q);//3-8译码器 for循环 方法二(推荐)input[2:0] A;output reg[7:0] Q;integer i;always @(A)begin Q=8'b1111_1111; for(i=0;i<=7;i=i+1) if(A==i) Q[i] = 0; else Q[i] = 1; endendmodule

编码器

module bvhk(A,Q);input[3:0] A;output reg[1:0] Q;always@(A) begin case(A) 4'b0001:begin Q=2'b00;end 4'b0010:begin Q=2'b01;end 4'b0100:begin Q=2'b10;end 4'b1000:begin Q=2'b11;end default:begin Q = 2'bx;end endcase endendmodule=============仿真============== A = 1; #100; forever begin A=A*2;#100;end

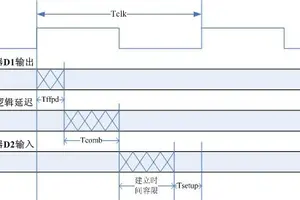

分频器

module aerwyghz(fout,clk,res);//分频器input clk,res;output reg fout;reg[29:0] counter;always@(posedge clk)begin if(res)begin counter<=0;fout<=0; end else begin if(counter==24)//50分频,10分频counter==9 begin counter<=0;fout<=~fout; end else begin counter <=counter+1; end endendendmodule==================分频器仿真======================= clk = 0;res = 1; clk=1;#100; res=0; forever #10 clk = !clk;

PWM

module ryuj(clk,res,pwm,fout);input clk,res;input[3:0]pwm;output reg fout;reg[30:0] j;always@(posedge clk or negedge res)begin if(res==0) begin j<=0;fout<=0;end else begin if(j==9) begin j<=0;end else j<=j+1; if(j<pwm)fout<=1; else fout<=0; endendendmodule========================仿真======================== initial begin // Initialize Inputs clk = 0;pwm = 0;res = 1;res = 0;#100; res = 1; pwm = 8; repeat(100) begin #100; clk = ~clk;end end

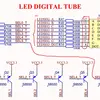

七段数码管译码器*

`timescale 1ns / 1psmodule rtyu(bcd_out,bit_S,indec,res);input [3:0]indec;input res;output reg[3:0] bit_s;output reg[6:0]bcd_out;always@(res,indec)begin if(!res)begin bcd_out=7'bx;bit_s=4'b1111;end else begin bit_s=4'b1110; case(indec)//共阳数码管 dp、g、f、e、d、c、b、a 0:bcd_out=7'hc0;//1100_0000 1:bcd_out=7'hf9;//1111_1001 2:bcd_out=7'ha4;//1010_0100 3:bcd_out=7'hb0;//1011_0000 4:bcd_out=7'h99;//1001_1001 5:bcd_out=7'h92;//1001_0010 6:bcd_out=7'h82;//1000_0010 7:bcd_out=7'hf8;//1111_1000 8:bcd_out=7'h80;//1000_0000 9:bcd_out=7'h90;//1001_0000 endcase endendendmodule============仿真代码================ indec = 0; res = 1;#50; repeat(10)begin#100 indec=indec+1;end res=0;indec=0; repeat(10)begin#100 indec=indec+1;end

流水灯

module jhfgx(clk,led,res);output reg[7:0]led;input clk,res;reg[29:0] counter;always@(posedge clk)begin if(res)begin counter<=0;led<=8'b0000_0001;endelse beginif(led==0) led<=8'b0000_0001; if(counter>=25_000_00) begin counter<=0; led<=led<<1; end else counter<=counter+1;endendendmodule=====================仿真代码===================== initial begin // Initialize Inputs clk = 0;res = 1;clk=1;#100; res = 0; forever begin #25 clk=~clk;end end