结合华为5G通信、海思芯片及自研EDA工具链技术方向整理,覆盖基础到高阶考点

一、基础理论与语言类(10题)

1. 华为项目中为何常用Verilog而非VHDL?

答案:

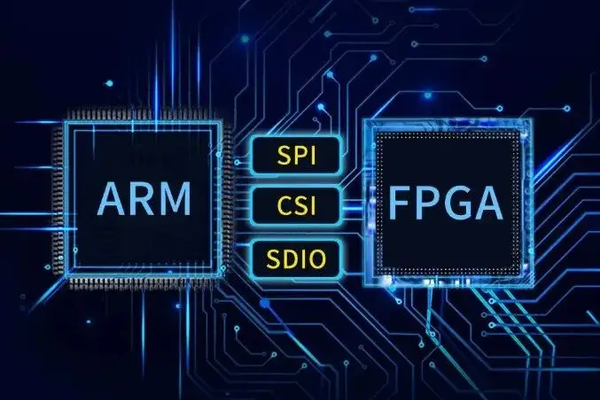

- 生态适配:华为自研工具链(如Ascend FPGA开发套件)对Verilog支持更完善,与ARM核协同设计效率高。

- 团队协作:国内华为系企业普遍使用Verilog,代码复用率高。

- 动态建模:Verilog的

generate块和系统函数更适合复杂通信协议栈开发(如5G Polar码实现)。

2. 解释Setup Time和Hold Time违例的修复方法(需结合华为高速接口场景)

答案:

- 缩短路径延迟:插入流水寄存器、逻辑复制(华为常用Xilinx UltraScale+的

CARRY8优化进位链)。 - 约束优化:设置

set_max_delay -from [get_clocks clk1] -to [get_clocks clk2]跨时钟域路径。 - 华为案例:光模块设计中,通过

set_false_path忽略非关键路径时序。

3. 华为对异步FIFO设计有哪些企业级规范?

答案:

- 格雷码深度:必须为2^N,避免指针跨多bit跳变。

- 安全冗余:读写指针增加奇偶校验位(华为GJB标准要求)。

- 覆盖率要求:仿真需覆盖FIFO满/空边界及亚稳态恢复场景。

4. 华为项目中为何强制使用SystemVerilog断言(SVA)?

答案:

- 协议验证:确保AXI4-Stream、DDR PHY接口信号符合华为自研IP核要求。

- 形式化验证:华为使用JasperGold对关键模块(如电源管理)做SVA穷举验证。

- 错误定位:

assert property可实时捕获时序违规,减少调试时间。

二、项目实战类(10题)

5. 描述你在华为风格项目中遇到的时序收敛难题及解决思路

参考答案:

问题:某5G基带FPGA在高温下时序违例(Setup Time -0.3ns)。

解决:

- 关键路径分析:用Vivado的

report_timing_summary定位到DSP48E2链。 - 流水优化:将组合逻辑拆分为3级流水,插入

(* keep = "true" *)保留寄存器。 - 约束调整:

set_clock_uncertainty增加高温余量,最终通过华为EMIR(电热耦合)签核。

6. 如何为华为光通信模块设计低功耗FPGA?

答案:

- 时钟门控:对非活跃区域的时钟网络使用

BUFGCE。 - 动态电压调节:通过Xilinx UltraScale的

PSU模块动态切换VCCINT电压(华为专利方案)。 - 功耗仿真:华为要求用Power Artist生成SAIF文件反标功耗数据。

7. 华为海思芯片中,如何验证DDR4 PHY与FPGA的兼容性?

答案:

- 眼图测试:使用示波器捕获DDR4 DQ信号,确保满足华为眼罩模板。

- IBIS-AMI模型:导入华为自研DDR4模型进行信道仿真。

- 压力测试:运行华为自研

HSDT(高速数据训练)算法验证稳定性。

三、华为技术生态类(10题)

8. 华为Ascend FPGA开发流程与Xilinx有何差异?

答案:

- 工具链:使用华为自研

HiSilicon Studio替代Vivado,支持昇腾AI核协同开发。 - IP核:强制使用华为安全加密IP(如AES-256核),禁止第三方未认证IP。

- 部署流程:代码需通过华为云

ModelArts平台进行安全校验和烧录。

9. 华为对FPGA代码安全性的企业级要求有哪些?

答案:

- 代码混淆:使用华为

SecEncrypt工具对RTL代码做非线性变换。 - 权限隔离:通过TCL脚本控制

read_only属性,禁止修改关键模块。 - 防篡改:比特流文件必须启用

AES-GCM加密,密钥由华为云端管理。

10. 解释华为“硬件归一化”理念在FPGA设计中的应用

答案:

- 模块复用:要求不同项目共用华为自研的PCIe Gen4/5核、以太网MAC核。

- 接口统一:所有AXI接口必须符合华为《IP核接口规范V3.2》。

- 验证标准化:使用华为

VPlan模板编写验证计划,覆盖率要求≥98%。

四、华为面试技巧与学习建议

华为FPGA面试特点:

- 协议栈深度:必问5G/LTE物理层实现(如Turbo编解码、信道估计)。

- 系统思维:关注FPGA与ASIC/CPU的协同设计(如华为鲲鹏+昇腾方案)。

- 合规意识:强调代码安全、国密算法(如SM4)和GJB标准。

学习资源推荐:

- 书籍:《华为FPGA设计规范》、《AXI协议权威指南》

- 工具:华为HiSilicon Studio试用版、ModelArts FPGA开发镜像

- 项目:复现华为公开技术文档中的参考设计(如光模块时钟恢复电路)

适用人群:

- 目标华为/OD岗的FPGA工程师

- 需掌握华为自研工具链(HiSilicon Studio)的开发者

- 计划切入5G通信、光模块、AI加速等华为核心业务的求职者

FPGA

FPGA小白

FPGA

未来

FPGA

bd

snx_taox

张阿木

用户_15394

884485GO