基于ZYNQ ECO开发板的蜂鸣器实验

简介

蜂鸣器广泛应用于计算机、打印机、复印机、报警器、电子玩具、汽车电子设备、电话机、定时器等电子产品中作发声器件;压电式蜂鸣器用于音乐贺卡、电子门铃和电子玩具等小型电子用品上作发声器件;本实验利用无源蜂鸣器实现《两只老虎》歌曲实验。所需工具

1、ZYNQ—ECO开发板; 2、无源蜂鸣器; 3、vivado开发工具;无源蜂鸣器发声原理

无源蜂鸣器也被称为电磁式蜂鸣器,主要是由永磁体、线圈、振荡片组成。无源蜂鸣器的发声过程为:外部按照一定的频率提供驱动一个振荡信号(一定占空比的方波),该信号是作用于线圈,产生的磁声与永磁体共同作用,使一片金属片(振荡片)发生震动,从而发出声音。实操

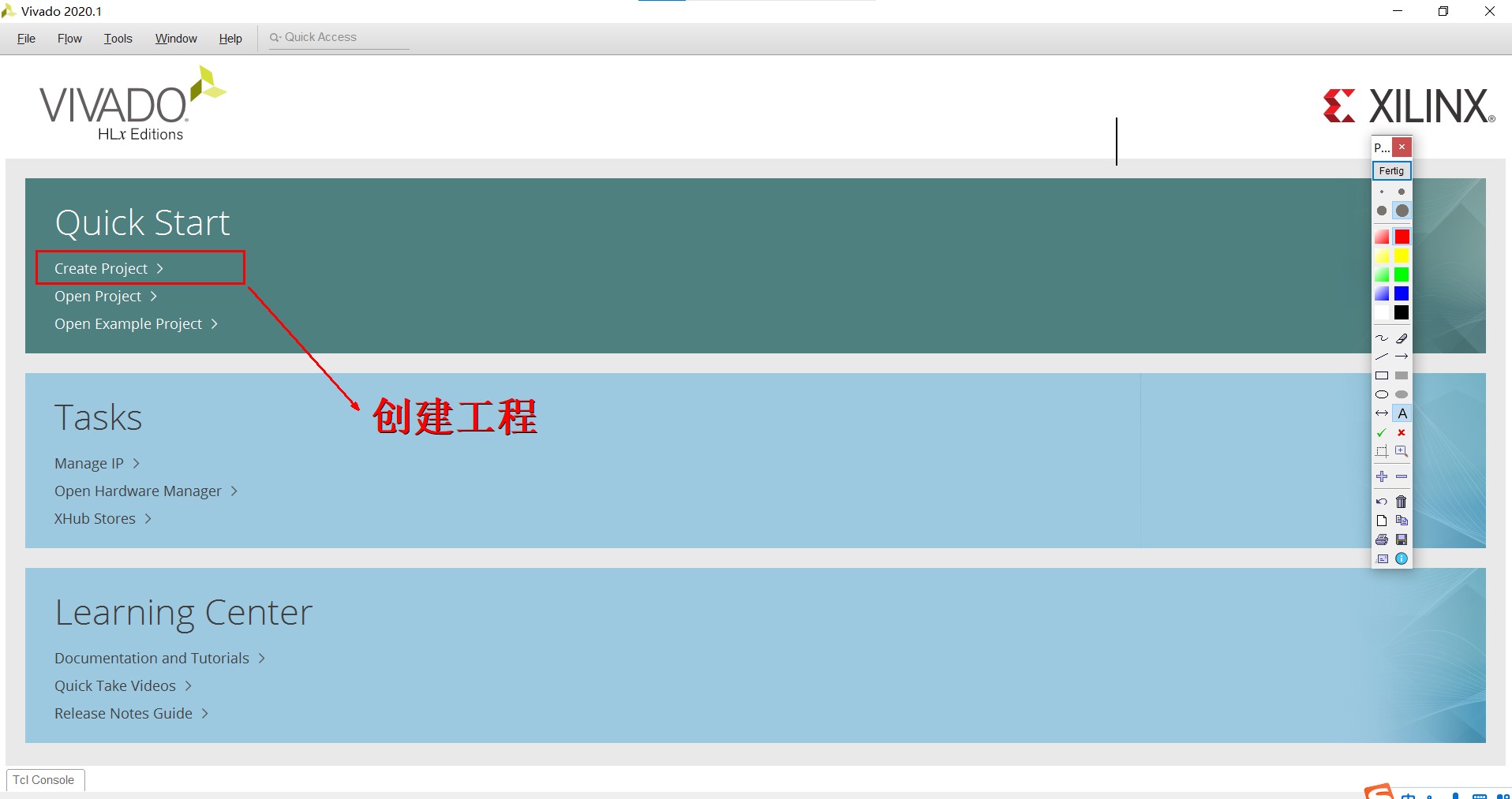

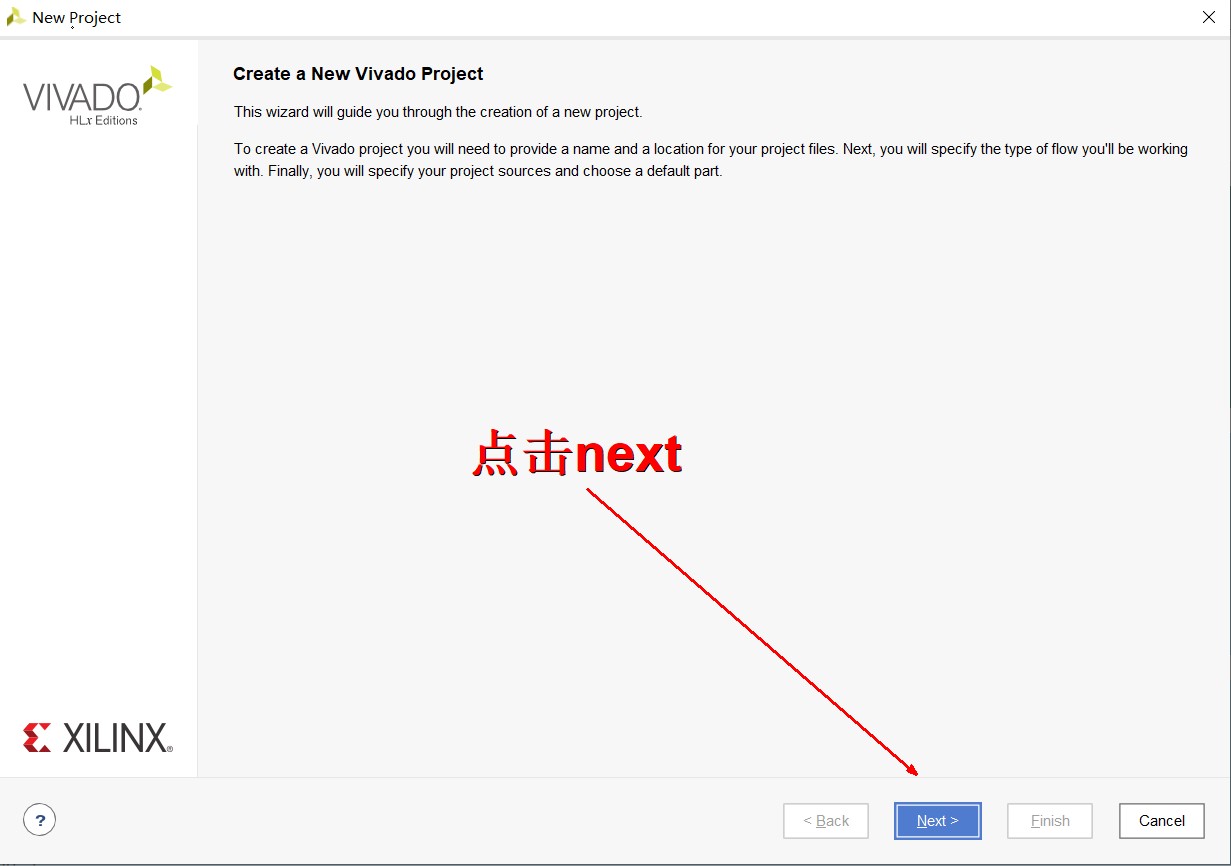

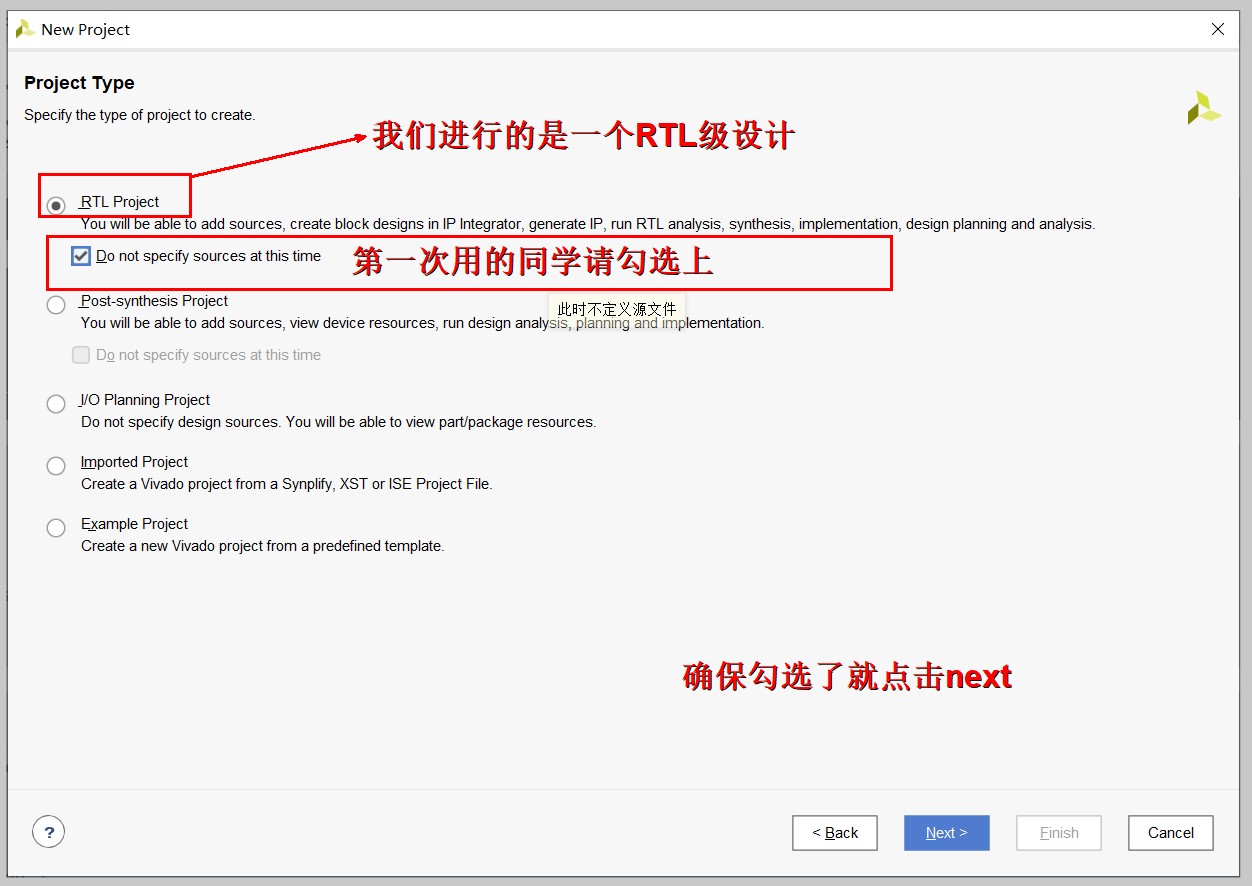

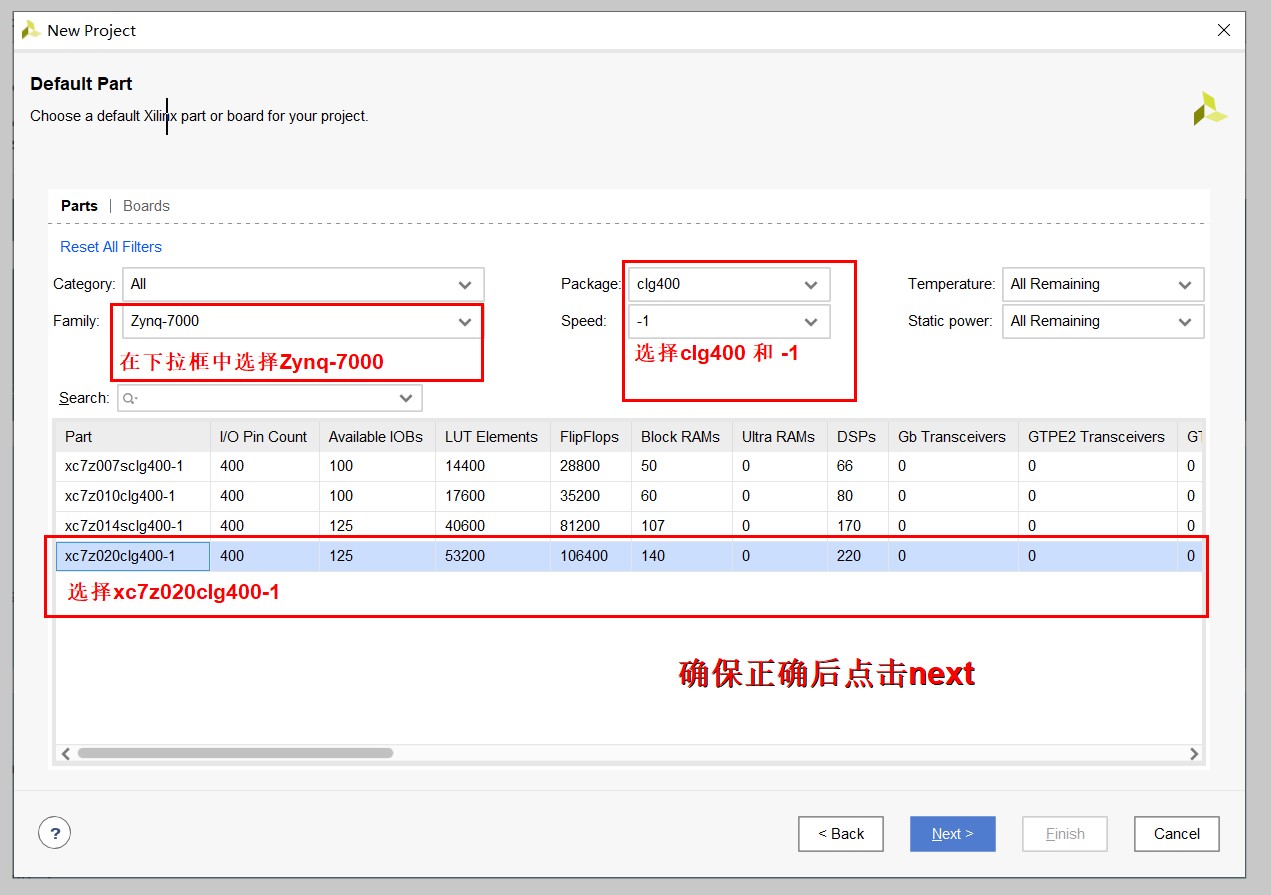

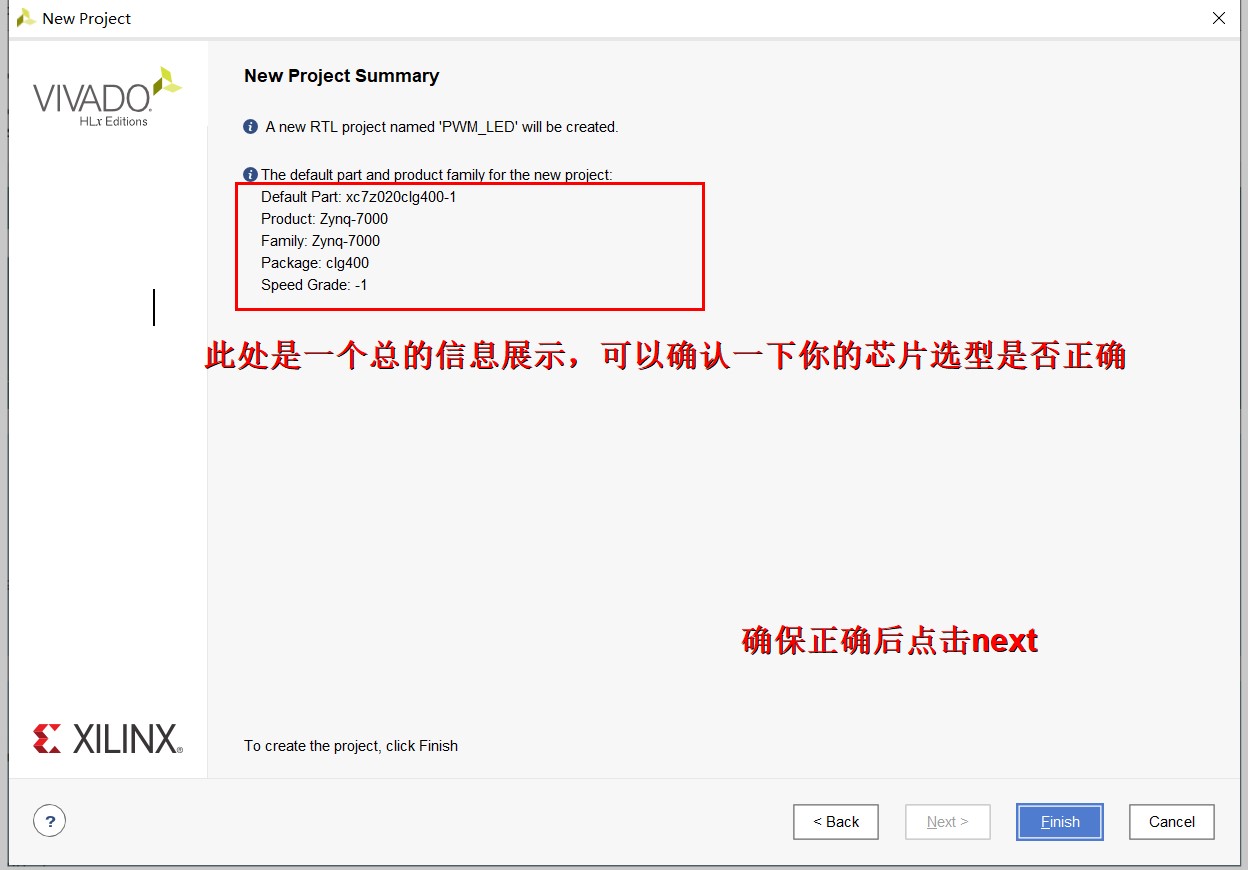

1、创建工程以及芯片选型

[caption id="attachment_413" align="alignnone" width="1024"]

[caption id="attachment_413" align="alignnone" width="1024"] 点击ok[/caption]

[caption id="attachment_414" align="alignnone" width="1024"]

点击ok[/caption]

[caption id="attachment_414" align="alignnone" width="1024"] 点击完成[/caption]

[caption id="attachment_415" align="alignnone" width="746"]

点击完成[/caption]

[caption id="attachment_415" align="alignnone" width="746"] 点击OK[/caption]

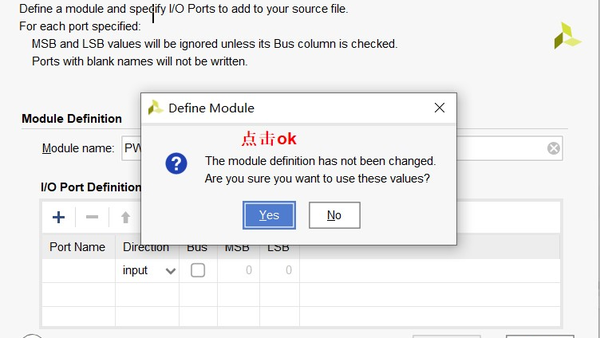

[caption id="attachment_416" align="alignnone" width="750"]

点击OK[/caption]

[caption id="attachment_416" align="alignnone" width="750"] 点击yes[/caption]

[caption id="attachment_417" align="alignnone" width="627"]

点击yes[/caption]

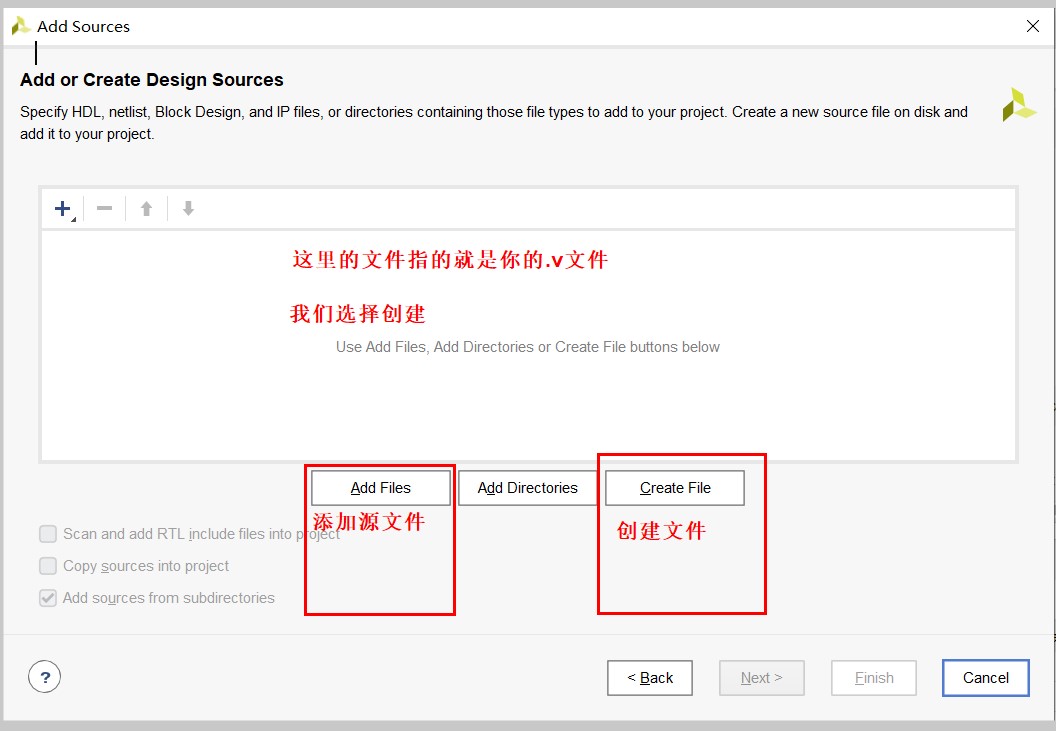

[caption id="attachment_417" align="alignnone" width="627"] beep.v为创建的设计源文件[/caption]

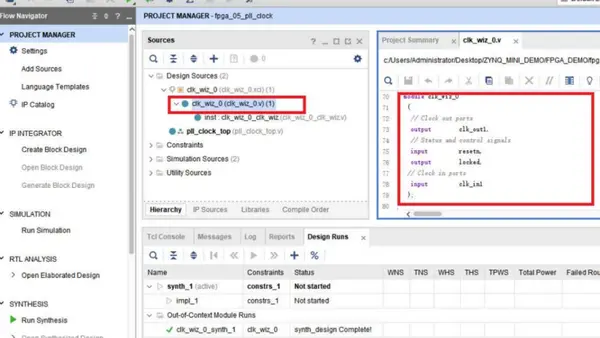

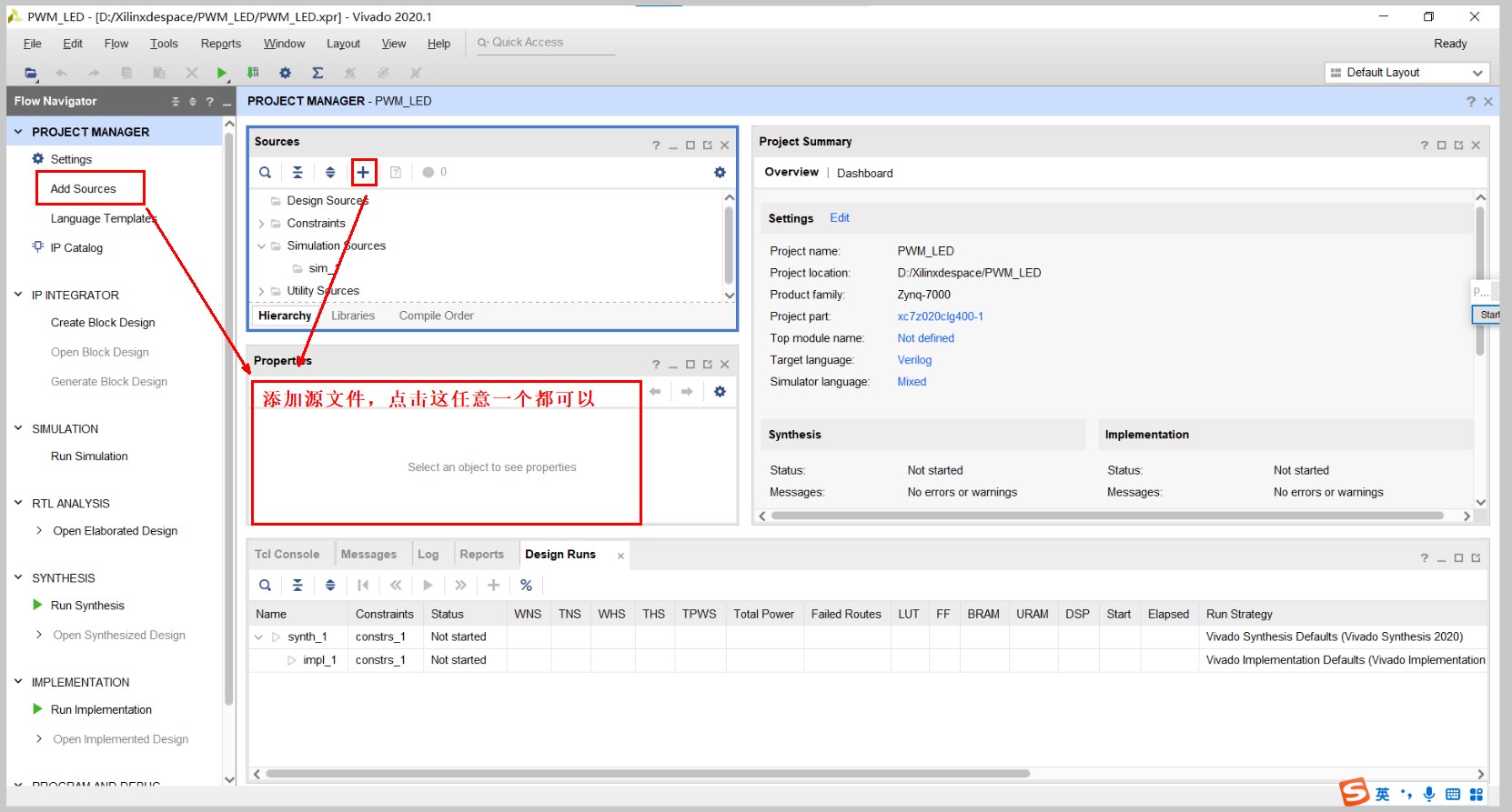

[caption id="attachment_418" align="alignnone" width="1603"]

beep.v为创建的设计源文件[/caption]

[caption id="attachment_418" align="alignnone" width="1603"] 写入代码[/caption]

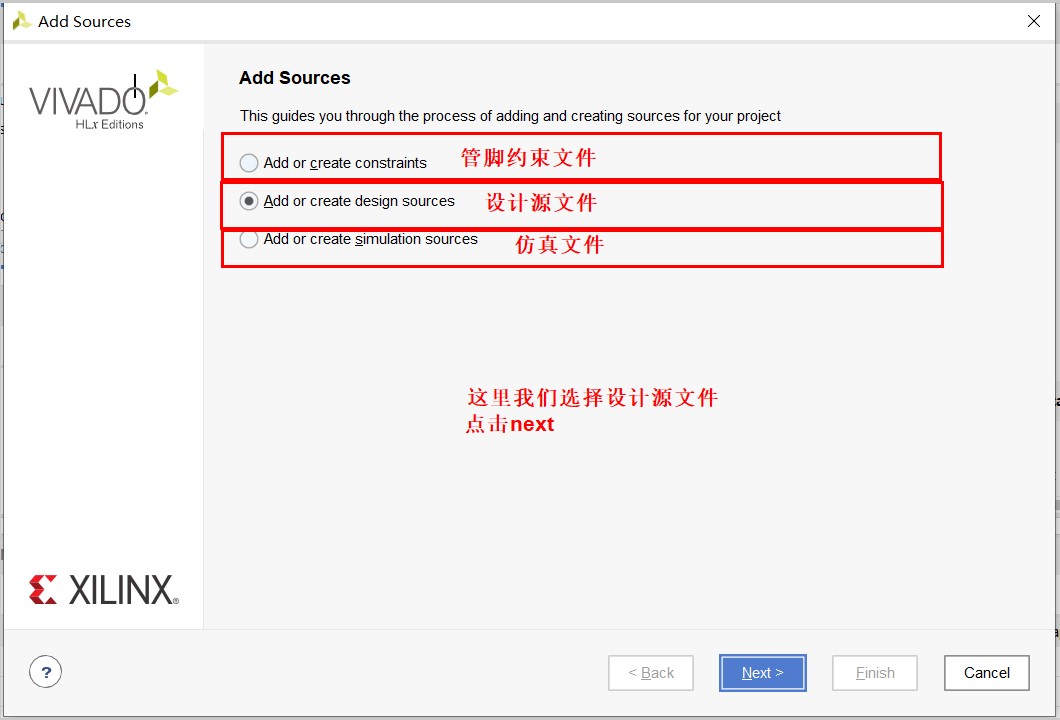

[caption id="attachment_236" align="alignnone" width="1048"]

写入代码[/caption]

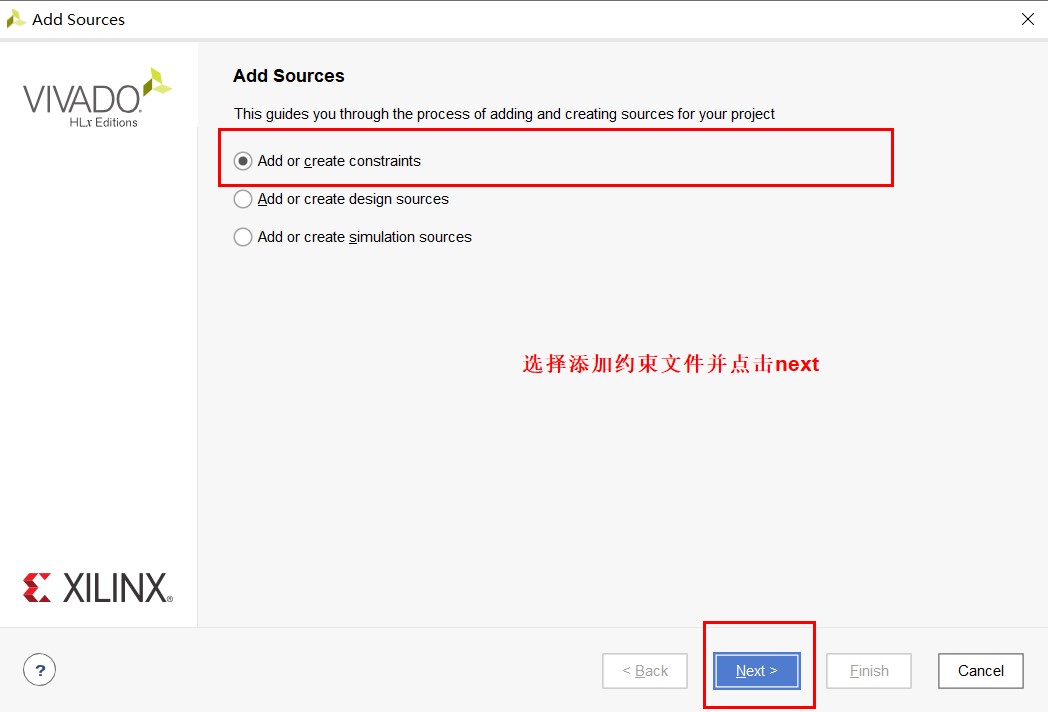

[caption id="attachment_236" align="alignnone" width="1048"] 创建约束文件[/caption]

[caption id="attachment_419" align="alignleft" width="637"]

创建约束文件[/caption]

[caption id="attachment_419" align="alignleft" width="637"] pin.xdc为约束文件[/caption]

[caption id="attachment_421" align="alignleft" width="944"]

pin.xdc为约束文件[/caption]

[caption id="attachment_421" align="alignleft" width="944"] 添加约束[/caption]

[caption id="attachment_422" align="alignleft" width="299"]

添加约束[/caption]

[caption id="attachment_422" align="alignleft" width="299"] 点击Generate Bitstream(生成编译文件)[/caption]

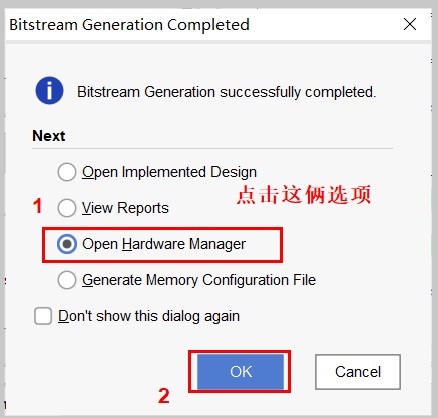

[caption id="attachment_324" align="alignnone" width="438"]

点击Generate Bitstream(生成编译文件)[/caption]

[caption id="attachment_324" align="alignnone" width="438"] 等待生成编译文件成功会出现一个任务栏[/caption]

[caption id="attachment_424" align="alignnone" width="3000"]

等待生成编译文件成功会出现一个任务栏[/caption]

[caption id="attachment_424" align="alignnone" width="3000"] 连接DEBUG接口,连接蜂鸣器[/caption]

连接DEBUG接口,连接蜂鸣器[/caption]

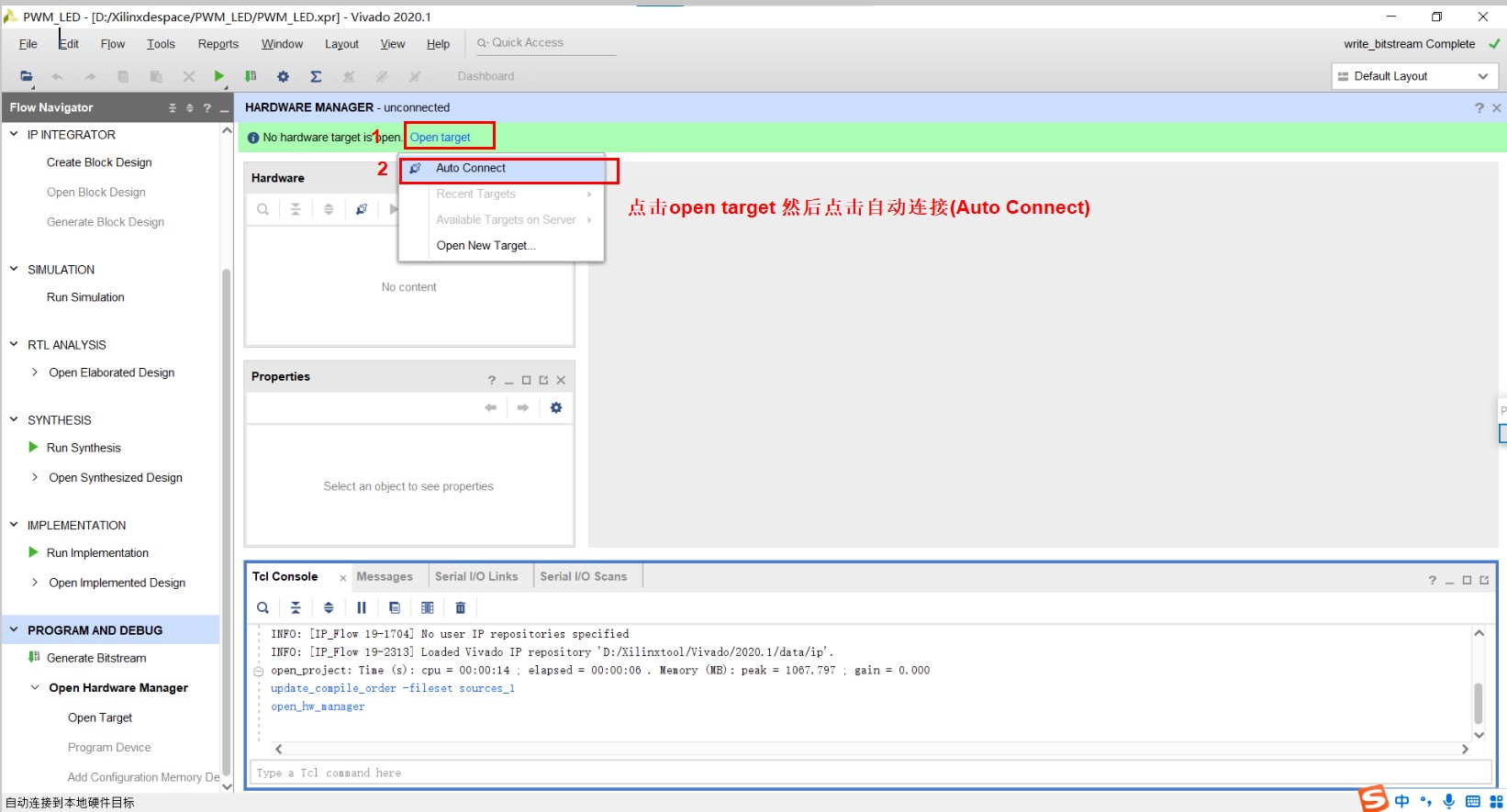

连接开发板

[caption id="attachment_423" align="alignnone" width="1913"]

连接开发板

[caption id="attachment_423" align="alignnone" width="1913"] 将编译文件下载到开发板,点击Program[/caption]

将编译文件下载到开发板,点击Program[/caption]

视频演示

[video width="1920" height="1080" mp4="https://admin.shaonianxue.cn/wp-content/uploads/2021/12/1640234875-307186186ede4e2.mp4"][/video]约束

[rihide]set_property PACKAGE_PIN K17 [get_ports clk] set_property PACKAGE_PIN U15 [get_ports beep] set_property PACKAGE_PIN M20 [get_ports rst_n] set_property IOSTANDARD LVCMOS33 [get_ports beep] set_property IOSTANDARD LVCMOS33 [get_ports clk] set_property IOSTANDARD LVCMOS33 [get_ports rst_n] [/rihide]源代码

[rihide]`timescale 1ns / 1ps module beep( input clk, input rst_n, output beep ); parameter delay=50_000_000/2; parameter delay_1=50_000_000/523/2; parameter delay_2=50_000_000/587/2; parameter delay_3=50_000_000/659/2; parameter delay_4=50_000_000/698/2; parameter delay_5=50_000_000/784/2; parameter delay_6=50_000_000/880/2; parameter delay_7=50_000_000/988/2; reg [31:0] cnt; always@(posedge clk or negedge rst_n) if(!rst_n) cnt<=32'd0; else if(cnt==delay) cnt<=32'd0; else cnt<=cnt+1; reg [31:0] state; always@(posedge clk or negedge rst_n) if(!rst_n) state<=32'd0; else if(cnt==delay) state<=state+1; else state<=state; reg [31:0] cnt_1; reg beep_1; always@(posedge clk or negedge rst_n) if(!rst_n) begin cnt_1<=32'd0; beep_1<=1'b1; end else if(cnt_1==delay_1) begin cnt_1<=32'd0; beep_1<=~beep_1; end else cnt_1<=cnt_1+1; reg [31:0] cnt_2; reg beep_2; always@(posedge clk or negedge rst_n) if(!rst_n) begin cnt_2<=32'd0; beep_2<=1'b1; end else if(cnt_2==delay_2) begin cnt_2<=32'd0; beep_2<=~beep_2; end else cnt_2<=cnt_2+1; reg [31:0] cnt_3; reg beep_3; always@(posedge clk or negedge rst_n) if(!rst_n) begin cnt_3<=32'd0; beep_3<=1'b1; end else if(cnt_3==delay_3) begin cnt_3<=32'd0; beep_3<=~beep_3; end else cnt_3<=cnt_3+1; reg [31:0] cnt_4; reg beep_4; always@(posedge clk or negedge rst_n) if(!rst_n) begin cnt_4<=32'd0; beep_4<=1'b1; end else if(cnt_4==delay_4) begin cnt_4<=32'd0; beep_4<=~beep_4; end else cnt_4<=cnt_4+1; reg [31:0] cnt_5; reg beep_5; always@(posedge clk or negedge rst_n) if(!rst_n) begin cnt_5<=32'd0; beep_5<=1'b1; end else if(cnt_5==delay_5) begin cnt_5<=32'd0; beep_5<=~beep_5; end else cnt_5<=cnt_5+1; reg [31:0]cnt_6; reg beep_6; always@(posedge clk or negedge rst_n) if(!rst_n) begin cnt_6<=32'd0; beep_6<=1'b1; end else if(cnt_6==delay_6) begin cnt_6<=32'd0; beep_6<=~beep_6; end else cnt_6<=cnt_6+1; reg [31:0] cnt_7; reg beep_7; always@(posedge clk or negedge rst_n) if(!rst_n) begin cnt_7<=32'd0; beep_7<=1'b1; end else if(cnt_7==delay_7) begin cnt_7<=32'd0; beep_7<=~beep_7; end else cnt_7<=cnt_7+1; reg beep_out; always@(posedge clk or negedge rst_n) if(!rst_n) beep_out<=1'd0; else case(state%16) 0:beep_out<=beep_1; 1:beep_out<=beep_2; 2:beep_out<=beep_3; 3:beep_out<=beep_1; 4:beep_out<=beep_1; 5:beep_out<=beep_2; 6:beep_out<=beep_3; 7:beep_out<=beep_1; 8:beep_out<=beep_3; 9:beep_out<=beep_4; 10:beep_out<=beep_5; 11:beep_out<=beep_5; 12:beep_out<=beep_3; 13:beep_out<=beep_4; 14:beep_out<=beep_5; 15:beep_out<=beep_5; endcase assign beep=beep_out;endmodule

[/rihide]