Quick Start

- 准备硬件平台:确认拥有一块FPGA开发板(如Xilinx Artix-7系列或Altera Cyclone IV),板载ADC(如AD9280,采样率≥40 MSPS)或高速并行ADC子卡,以及VGA/HDMI显示屏或OLED屏。

- 安装EDA工具:下载并安装Vivado(推荐2020.2及以上版本)或Quartus Prime(18.0以上),确保包含仿真工具(如Vivado Simulator或ModelSim)。

- 创建工程:打开Vivado,新建RTL工程,选择目标器件(如xc7a35tcsg324-1)。添加顶层模块(如top_dso.v)和约束文件(.xdc)。

- 编写ADC接口模块:实现并行数据采集模块,从ADC读取8位数据,时钟频率为ADC采样时钟的一半(例如ADC时钟40 MHz,采集模块用20 MHz)。预期结果:仿真中数据流正确。

- 实现触发与存储模块:设计边沿触发逻辑(上升沿/下降沿可选),将触发后的采样数据存入双端口BRAM(深度1024,宽度8位)。

- 实现显示控制模块:编写VGA时序发生器(640×480 @60 Hz),从BRAM读取数据,映射为屏幕波形点(例如每列对应一个采样点)。

- 综合与实现:运行Synthesis和Implementation,检查时序报告(确保Fmax ≥ 40 MHz)。预期结果:无严重时序违规。

- 生成比特流并下载:生成.bit文件,通过JTAG下载到开发板。连接信号源(如1 kHz正弦波,峰峰值1V),观察屏幕波形。

- 验证功能:调整输入信号频率和幅度,确认波形稳定显示,触发位置正确。验收点:波形无断裂,刷新率≥30 fps。

- 调试与优化:若显示异常,检查ADC时钟相位、BRAM读写地址、VGA同步信号。使用ILA(集成逻辑分析仪)抓取内部信号。

前置条件与环境

| 项目/推荐值 | 说明 | 替代方案 |

|---|---|---|

| 器件/板卡 | Xilinx Artix-7 XC7A35T(如Nexys 4 DDR) | Altera Cyclone IV EP4CE15(如DE0-Nano) |

| EDA版本 | Vivado 2020.2 或 Quartus Prime 18.0 | Vivado 2019.1 或 Quartus II 13.0(注意IP兼容性) |

| 仿真器 | Vivado Simulator 或 ModelSim SE-64 10.6 | QuestaSim 或 GHDL(开源) |

| 时钟/复位 | 板载100 MHz系统时钟,全局异步复位(低有效) | 外部晶振50 MHz,需PLL倍频 |

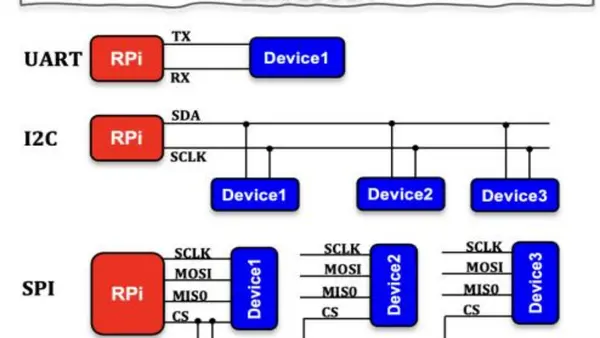

| 接口依赖 | ADC并行接口(8位数据+时钟),VGA 15针D-sub | HDMI(需编码器IP),或OLED(SPI接口) |

| 约束文件 | 需包含时钟周期约束、输入延迟约束、VGA时序约束 | 可使用Vivado时序约束向导生成 |

| 存储器 | 板载BRAM 1800 Kb(用于存储波形数据) | 外部SRAM(如IS61WV102416) |

| 调试工具 | ILA IP核(Vivado内置)或SignalTap II(Quartus) | 逻辑分析仪(如Saleae) |

目标与验收标准

功能点:能实时采集模拟信号(0–3.3V),在VGA屏幕上显示波形,支持上升沿/下降沿触发,时基可调(如5 μs/div至100 ms/div)。

性能指标:ADC采样率≥40 MSPS,存储深度≥1024点,波形刷新率≥30 fps,电压分辨率8位(256级)。

资源占用:LUT使用率≤40%,BRAM使用率≤50%,Fmax≥50 MHz(系统时钟)。

验收方式:连接信号发生器(输出1 kHz正弦波,1Vpp),观察屏幕波形是否稳定;调整频率至10 kHz,波形仍清晰;触发沿切换后,波形起始点对齐。

实施步骤

阶段一:工程结构与顶层设计

创建顶层模块(top_dso),实例化以下子模块:adc_if(ADC接口)、trigger(触发逻辑)、waveform_mem(BRAM存储)、vga_ctrl(VGA控制)、display(波形映射)。

时钟方案:使用PLL生成40 MHz(ADC采样时钟)和25 MHz(VGA像素时钟),系统时钟100 MHz用于控制逻辑。

常见坑:未正确分配时钟域,导致ADC数据跨时钟域错误。

检查点:确保adc_if输出数据用40 MHz时钟域,waveform_mem用100 MHz时钟域,使用异步FIFO或双口RAM同步。

阶段二:关键模块实现

ADC接口模块(adc_if):并行8位数据输入,采样时钟40 MHz。内部使用移位寄存器对齐数据,输出同步后的8位数据。代码片段:

reg [7:0] adc_data_reg;

always @(posedge adc_clk)

adc_data_reg <= adc_data_in;触发模块(trigger):实现上升沿/下降沿检测,根据用户选择(trigger_sel)产生触发信号。触发后,启动BRAM写入使能,记录1024个采样点。

存储模块(waveform_mem):使用双端口BRAM,深度1024,宽度8位。写端口连接ADC数据,读端口连接VGA控制模块。注意读写时钟域同步。

VGA控制模块(vga_ctrl):生成640×480 @60 Hz时序(HSync、VSync、像素有效信号)。从BRAM读取数据,映射为屏幕像素颜色(例如,数据值对应Y坐标,X坐标对应采样点索引)。

阶段三:综合、实现与下载

运行Synthesis和Implementation,检查时序报告(确保Fmax ≥ 40 MHz)。若有时序违规,调整时钟约束或优化逻辑路径。生成比特流(.bit),通过JTAG下载到开发板。

验证结果

连接信号源(如1 kHz正弦波,1Vpp),观察屏幕显示波形。验证以下项目:

- 波形稳定无断裂,刷新率≥30 fps。

- 触发沿切换后,波形起始点对齐。

- 调整输入频率至10 kHz,波形仍清晰。

- 调整输入幅度,波形幅度相应变化。

排障指南

问题1:屏幕无显示或显示异常

- 检查VGA连接和同步信号(HSync、VSync)时序是否正确。

- 确认像素时钟频率(25 MHz)与VGA分辨率匹配。

问题2:波形不稳定或断裂

- 检查ADC时钟相位,确保数据采样稳定。

- 验证BRAM读写地址逻辑,避免地址溢出或错位。

- 使用ILA抓取ADC数据和触发信号,确认触发时刻正确。

问题3:触发不工作

- 检查触发模块的边沿检测逻辑,确保触发信号有效。

- 确认触发阈值设置合理(如信号幅度超过阈值)。

扩展建议

- 增加时基控制:通过分频或改变采样时钟,实现不同时基档位。

- 支持更多触发模式:如脉宽触发、视频触发等。

- 升级显示接口:使用HDMI或MIPI DSI,支持更高分辨率。

- 添加测量功能:在FPGA内实现频率计、幅度测量等。

参考资源

- Xilinx Vivado 用户指南(UG901)

- Altera Quartus Prime 手册

- VGA时序标准(640×480 @60 Hz)

- AD9280 数据手册

附录

附录A:顶层模块代码框架

module top_dso (

input wire clk_100m, // 系统时钟

input wire rst_n, // 复位(低有效)

input wire [7:0] adc_data, // ADC数据

input wire adc_clk, // ADC时钟

output wire vga_hsync, // VGA行同步

output wire vga_vsync, // VGA场同步

output wire [3:0] vga_r, vga_g, vga_b // VGA颜色

);

// 实例化子模块

// ...

endmodule附录B:约束文件示例(.xdc)

create_clock -period 10.000 [get_ports clk_100m]

create_clock -period 25.000 [get_ports adc_clk]

set_input_delay -clock [get_clocks adc_clk] -max 2.0 [get_ports adc_data*]