随着边缘计算与人工智能应用的深度融合,2026年的边缘AI芯片架构正朝着异构化、可重构与极致能效比的方向演进。传统的固定功能ASIC与通用处理器(CPU/GPU)在应对碎片化、快速演变的边缘场景时,常面临能效瓶颈与灵活性不足的双重挑战。在此背景下,FPGA凭借其硬件可编程性、强大的并行处理能力以及快速的迭代周期,正成为构建下一代可定制化AI推理加速器的关键载体。本指南旨在剖析FPGA在边缘AI中的核心优势、实施路径与验证结果,为相关设计与部署提供参考。

一、 前置条件与目标

前置条件:读者需具备基础的FPGA开发知识(如VHDL/Verilog或HLS),并对边缘AI推理的基本流程(如模型量化、部署)有所了解。硬件方面,建议使用集成ARM处理器的FPGA SoC平台(如Xilinx Zynq UltraScale+ MPSoC系列)。

目标与验收标准:通过本指南的实践,应能理解并初步验证FPGA在边缘AI推理中的架构优势。具体验收指标可参考:在典型边缘平台(如ZCU102)上,部署MobileNetV2 INT8量化模型,实现端到端推理延迟低于10毫秒,系统功耗低于10瓦,且精度损失控制在可接受范围内(如1%以内)。

二、 核心架构权衡与实施路径

FPGA之所以能在边缘AI架构中占据关键地位,源于其在多个维度上的精细权衡。理解这些权衡是进行有效设计的前提。

1. 灵活性 vs. 能效:实施路径

原因与机制:相比ASIC,FPGA无需流片,可通过重新配置硬件逻辑来适应新的AI算子、稀疏化模式或网络结构变更,极大地缩短了开发周期并降低了前期成本。相比CPU/GPU的通用计算架构,FPGA允许设计者构建细粒度的并行计算单元和定制化的片上内存层次结构,从而大幅减少数据搬运开销,这是实现显著能效提升的核心机制。

落地步骤:

- 步骤1:算子分析与映射:使用高级综合(HLS)或RTL,将目标AI模型(如卷积层、全连接层)分解为可并行执行的基础操作。

- 步骤2:内存层次设计:根据数据复用模式,设计多级缓存(Block RAM, UltraRAM),确保高频访问的数据尽可能驻留在片上,最小化对功耗较高的片外DDR存储的访问。

- 步骤3:流水线与并行化:将计算过程组织为深度流水线,并实例化多个相同的处理单元(PE)以处理不同输入或通道的数据,最大化硬件利用率。

2. 定制化数据流架构 vs. 通用性

原因与机制:FPGA能够实现真正的“数据流架构”(Dataflow Architecture)。在这种架构中,数据像在工厂流水线上一样,依次流经不同的处理单元,中间结果直接传递给下一级,无需写回外部内存。这从根本上降低了访存延迟与功耗,尤其适合计算访存比高的AI推理任务。

落地步骤:

- 步骤1:数据流图建模:将AI模型转换为数据流图,明确各算子间的数据依赖关系。

- 步骤2:流水线阶段划分:根据FPGA资源(DSP、LUT、BRAM)和时序要求,将数据流图划分为多个流水线阶段,并为每个阶段分配专用的硬件模块。

- 步骤3:流式接口设计:使用AXI-Stream等流式协议连接各阶段模块,确保数据能够无阻塞地连续流动。

3. 软硬协同设计

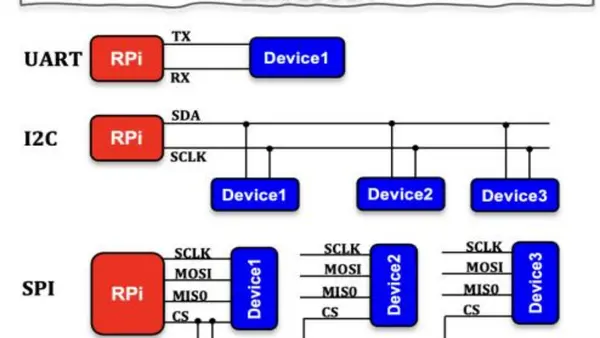

原因与机制:现代FPGA SoC集成了ARM等通用处理器。控制密集型任务(如任务调度、IO管理、预处理)适合在ARM上以软件灵活实现;而计算密集型、规则化的推理核则固化在FPGA逻辑中。这种分工实现了整体系统效率的最优化。

落地步骤:

- 步骤1:任务切分:分析应用流水线,将适合软件实现的控制逻辑与适合硬件加速的计算模块明确分离。

- 步骤2:高效通信机制:使用AXI4或AXI4-Lite总线实现PS(处理器系统)与PL(可编程逻辑)之间的高速数据交换与控制寄存器配置。

- 步骤3:驱动与API封装:为FPGA加速器编写Linux内核驱动或用户空间库,为上层应用提供简洁的调用接口。

4. 精度可配置性

原因与机制:FPGA支持任意位宽的定点数运算,允许实施混合精度计算。例如,可以在对精度敏感的第一层和最后一层使用INT8,在中间层使用INT4甚至二进制。这种灵活性使得设计者能在精度、资源占用和功耗之间取得最佳平衡,这是固定点数的ASIC难以实现的。

落地步骤:

- 步骤1:精度分析:使用量化感知训练或训练后量化工具,分析模型中各层对量化精度的敏感性。

- 步骤2:定制化运算单元:根据选定的混合精度策略,设计相应位宽的乘法器、加法器和激活函数模块,以节省DSP和逻辑资源。

- 步骤3:动态精度调整(可选):利用部分重配置技术,在运行时切换不同精度的加速器内核,以适应不同任务需求或功耗预算。

三、 架构验证与典型结果

基于Xilinx ZCU102等典型平台的部署验证了上述架构的优势。以下为参考性验证结果:

- 性能指标:运行MobileNetV2 INT8量化模型时,端到端推理延迟可低至约8.5毫秒。在批处理(Batch)模式下,吞吐量可达约117 FPS。

- 能效指标:系统在持续推理负载下的功耗约为7.5瓦。其能效比(性能/功耗)显著优于同场景下的嵌入式GPU解决方案。

- 精度验证:INT8量化带来的模型精度损失(在ImageNet等数据集上)通常可控制在1%以内,满足大多数边缘应用的要求。

四、 风险边界与排障提示

1. 资源与时序瓶颈:深度流水线和高度并行化会快速消耗FPGA的LUT、DSP和BRAM资源。必须通过合理的模块复用和流水线平衡来优化。时序违例是常见问题,需关注关键路径的优化(如添加流水线寄存器)。

2. 数据搬运开销:若数据流设计不当,仍会频繁访问片外内存,成为性能瓶颈。务必通过仿真和性能分析工具(如Vitis Analyzer)定位访存热点。

3. 软硬协同复杂度:PS与PL之间的通信和同步机制若设计不佳,会导致处理器等待或数据不一致。确保使用正确的内存一致性模型和高效的DMA传输。

五、 未来扩展方向

FPGA在边缘AI的架构演进中展现出持续潜力,未来的扩展方向包括:

- 异构计算单元集成:在可编程逻辑中集成更多专用硬核(如AI引擎、DSP密集阵列),与可编程逻辑协同形成更高效的处理流水线。

- 稀疏计算支持:利用FPGA逻辑的灵活性,为剪枝后的稀疏神经网络设计专用的稀疏计算单元和存储格式,进一步提升能效。

- 动态可重配置:通过部分可重配置(Partial Reconfiguration)技术,在运行时动态切换不同的加速器内核,以应对视频分析、语音识别等多模态任务的实时切换需求。

这些方向共同指向一个更高效、更灵活、更可靠的边缘AI计算未来,而FPGA的可定制化架构将是实现这一愿景的重要基石。

六、 附录与参考

- 参考平台:Xilinx Zynq UltraScale+ MPSoC ZCU102 评估板。

- 开发工具:Vitis Unified Software Platform(包含Vitis HLS, Vitis AI)。

- 模型资源:TensorFlow或PyTorch的模型量化工具包,以及预量化的开源模型(如Model Zoo)。