在复杂的FPGA设计中,时序约束是确保电路在目标频率下稳定运行的基石。随着设计规模扩大、时钟域增多,简单的周期约束已难以精确描述所有时序关系。多周期路径(Multicycle Path)与伪路径(False Path)作为高级时序约束的核心工具,能够精准指导综合与实现工具,避免因过度约束导致的实现困难或资源浪费。本指南将通过实战流程,系统讲解其设置方法、应用场景与常见陷阱。

前置条件与环境准备

在设置高级时序约束前,请确保设计环境已就绪:

- RTL代码:已完成功能验证,架构合理。约束的目的是描述已知时序关系,而非修复设计缺陷。

- 基础时钟约束:已正确定义所有时钟(create_clock, create_generated_clock)。

- 验证手段:准备好仿真环境(如VCS/QuestaSim)及上板测试工具(如逻辑分析仪),用于约束前后的功能与时序验证。

目标与验收标准

完成本指南后,您应能:

- 准确识别设计中需要多周期或伪路径约束的时序路径。

- 正确编写并应用

set_multicycle_path与set_false_path约束。 - 通过时序报告验证约束生效,且设计功能正确。

- 理解约束背后的原理,并能排查常见实施问题。

实施步骤

阶段一:识别与分类目标路径

在添加约束前,必须基于设计意图和时序报告,准确识别目标路径。

- 运行初始时序分析:在不添加高级约束的情况下,运行综合与布局布线,生成时序报告。

- 分析报告,识别候选路径:

1. 多周期路径候选:Slack为负或紧张,但逻辑上数据无需在每个时钟周期都稳定。典型场景包括:使能信号控制的计数器、多拍完成的算法单元、状态机中跨周期稳定的控制信号。

2. 伪路径候选:Slack为负,但路径两端逻辑不存在功能上的同步数据传输关系。典型场景包括:跨异步时钟域的路径(但尚未进行同步处理)、测试逻辑与功能逻辑之间、上电复位前即已稳定的配置路径。 - 关键原则:约束必须基于对数据流和控制流的深刻理解,避免仅凭Slack值盲目添加约束。

阶段二:编写多周期路径约束

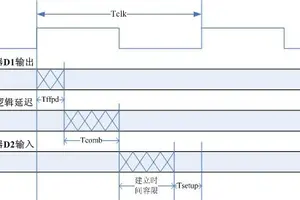

多周期路径约束的核心是告知时序分析工具,建立时间(Setup)和保持时间(Hold)的检查可以放宽到多个时钟周期后。

- 基本命令:使用

set_multicycle_path命令。

--setup N:指定建立时间检查在N个周期后进行(默认N=1)。

--hold N:指定保持时间检查在N个周期前进行。通常,-hold值应设为-setup值减1,以保持检查窗口的相对位置。 - 示例:一个使能信号每3个周期有效一次的数据路径。

set_multicycle_path -setup 3 -from [get_pins data_gen/en_reg/C] -to [get_pins data_proc/data_reg/D]

set_multicycle_path -hold 2 -from [get_pins data_gen/en_reg/C] -to [get_pins data_proc/data_reg/D] - 注意事项:

1. 尽量使用-from、-to精确指定路径起点和终点,慎用通配符。

2. 必须成对设置-setup和-hold,否则可能导致保持时间违例。

3. 明确约束的时钟边沿关系(-start/-end),对于跨时钟域的多周期路径尤为重要。

阶段三:编写伪路径约束

伪路径约束直接告知工具,某些路径无需进行时序分析。

- 基本命令:使用

set_false_path命令。 - 应用场景:

1. 异步时钟域之间(已通过同步器处理):

set_false_path -from [get_clocks clk_a] -to [get_clocks clk_b]

set_false_path -from [get_clocks clk_b] -to [get_clocks clk_a](双向约束)

2. 特定功能无关路径:

set_false_path -from [get_cells test_mode_reg] -to [get_cells *] - 注意事项:

1. 优先使用-from/-to指定时钟或单元,-through选项易产生意外覆盖,需谨慎。

2. 对于跨时钟域路径,必须确保RTL中已存在可靠的同步机制(如两级同步器),否则设置伪路径将掩盖亚稳态风险。

3. 伪路径约束会完全移除该路径的时序优化,确保它确实是功能上不可能或无需优化的路径。

阶段四:验证与迭代

添加约束后,必须进行多层次验证。

- 时序验证:重新运行实现流程,查看时序报告。

- 确认目标路径的Slack已按预期改善。

- 检查是否引入新的保持时间违例。

- 确认未影响其他关键路径的时序。 - 功能验证:进行动态仿真。

- 运行常规功能测试。

- 重点测试与约束路径相关的边界情况和极端条件。

- 确认约束没有改变设计的逻辑行为。 - 上板实测:在真实硬件上验证。

- 结合逻辑分析仪或ILA,观察约束路径上的信号实际时序。

- 进行长时间压力测试,排查间歇性故障或亚稳态。

原理与机制分析

多周期路径的本质是放宽时序分析工具默认的“单周期传输”假设。工具默认要求数据在一个周期内从起点传播到终点。多周期约束将建立时间检查窗口后移,并将对应的保持时间检查窗口前移,从而更贴合电路实际工作模式(如使能信号控制的数据流)。这能将优化资源(如逻辑复制、寄存器重定时)集中到真正关键的单周期路径上,提升设计性能与资源利用率。

伪路径的本质是移除那些在功能上不可能发生、或已通过其他机制(如同步器)保证安全的路径的时序分析负担。这能显著减少工具运行时间,并防止工具对这些路径进行不必要的、甚至有害的优化(例如,试图优化一个跨异步时钟域且未同步的路径,反而可能增加亚稳态概率)。其核心风险在于误判:如果将一条实际需要时序检查的路径错误地标记为伪路径,将导致工具忽略其时序问题,从而引发电路功能故障。

故障排查

- 问题:添加多周期约束后,出现保持时间(Hold)违例。

原因与解决:通常是因为只设置了-setup而未正确设置-hold。工具默认的保持时间检查仍在原时钟边沿。需补上set_multicycle_path -hold (N-1)约束。 - 问题:约束似乎未生效,时序报告无变化。

原因与解决:检查约束语法是否正确;使用report_timing_constraints命令查看约束是否被成功加载;确认-from/-to指定的对象名称与设计中的层次结构完全匹配。 - 问题:上板后,相关功能间歇性出错。

原因与解决:可能是多周期约束的周期数(N)小于实际电路需求。重新审查数据流,可能需要增大N值。也可能是伪路径约束错误地覆盖了实际需要同步的跨时钟域路径,此时应移除伪路径约束,并在RTL中增加同步器。 - 问题:工具运行时间未减少,甚至增加。

原因与解决:可能使用了过于宽泛的通配符(如*),导致工具需要处理大量约束对象。优化约束,使其更精确。

扩展与进阶实践

- 参数化约束:在Tcl脚本中定义变量(如

set MCP_CYCLES 3),提升约束的可读性与复用性。 - 异步时钟组约束:对于复杂的多时钟域设计,使用

set_clock_groups -asynchronous命令可以更简洁、安全地声明时钟域间的异步关系,其效果等同于为组间所有路径设置伪路径。 - 精确接口约束:对于FPGA与外部芯片的接口,使用

set_input_delay/set_output_delay,并结合set_max_delay/set_min_delay进行更精确的绝对延时约束。 - 约束文档化:为每条重要的高级约束添加注释,说明其设计意图、约束对象和原因。建立项目约束文档,这是团队协作和后期维护的关键。

参考与附录

- Xilinx UG903: Vivado Design Suite User Guide - Using Constraints.

- Intel Quartus Prime Standard Edition User Guide: Timing Analyzer.

- “Static Timing Analysis for Nanometer Designs” by J. Bhasker, R. Chadha.

(注:所有约束命令语法请以所用FPGA厂商工具的最新官方文档为准。)