本文档提供一套完整的、可综合的FPGA千兆以太网UDP协议栈实现方案。方案覆盖从物理层(PHY/MAC)到传输层(UDP)再到应用层接口的完整数据通路,旨在帮助工程师快速构建基于FPGA的以太网通信系统。文档遵循“先跑通,再优化”的原则,提供清晰的步骤、可验证的结果和详尽的故障排查指南。

Quick Start

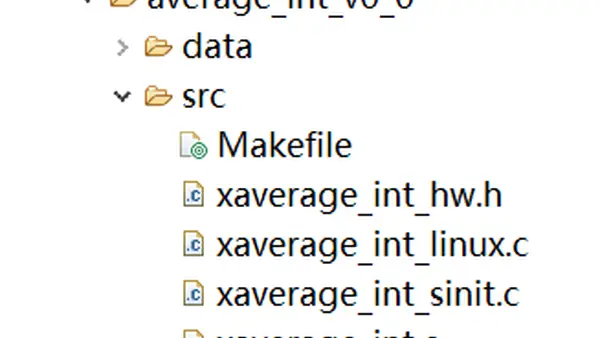

- 步骤1: 获取参考设计源码,通常包含RTL(tri_mode_ethernet_mac, udp_ip_stack, app_interface)、约束文件(.xdc)和测试脚本。

- 步骤2: 在Vivado(推荐2022.1)中创建新工程,选择与你的开发板匹配的FPGA器件(如XC7A35T-2FGG484I)。

- 步骤3: 添加所有RTL源文件到工程。将约束文件(.xdc)添加到约束集,并根据板卡原理图修改时钟引脚、复位引脚和RGMII接口引脚定义。

- 步骤4: 在顶层模块(top.v)中,确认时钟生成模块(如MMCM/PLL)已正确配置,为MAC提供125MHz参考时钟和用户逻辑提供所需时钟。

- 步骤5: 运行综合(Synthesis)。检查综合报告,确保无语法错误,并关注“Unconstrained Internal Endpoints”警告,后续需通过约束解决。

- 步骤6: 打开综合后的设计,运行实现(Implementation)。重点关注布局布线后的时序报告(Timing Report),确保所有时序约束(特别是RGMII接口的时钟-数据偏移约束)被满足。

- 步骤7: 生成比特流(Generate Bitstream)。

- 步骤8: 将比特流下载到FPGA开发板。使用网线连接开发板千兆网口和PC网口。

- 步骤9: 在PC上配置静态IP地址(如192.168.1.100),确保与FPGA设计中的固定IP(如192.168.1.10)在同一网段。

- 步骤10: 在PC上使用网络调试工具(如Wireshark抓包、NetAssist或自定义Python脚本)向FPGA的IP:Port发送UDP数据包。观察FPGA板载LED或通过UART回传信息,确认收到数据并成功回复。

前置条件与环境

| 项目 | 推荐值/说明 | 替代方案/注意点 |

|---|---|---|

| FPGA开发板 | 搭载千兆以太网PHY芯片(如RTL8211, KSZ9031)和支持RGMII接口 | 必须确认PHY型号与参考设计驱动兼容;MII接口需修改MAC侧接口逻辑。 |

| EDA工具 | Xilinx Vivado 2022.1 | Vivado 2018.3及以上版本通常可用,但Tri-mode MAC IP核版本可能不同。 |

| 仿真工具 | Vivado Simulator / ModelSim | 用于前期模块验证。需准备以太网帧、IP包、UDP包的测试向量。 |

| 时钟与复位 | 板载晶振提供125MHz或25MHz时钟;全局复位信号 | 若晶振非125MHz,需通过MMCM/PLL生成125MHz供RGMII参考时钟。 |

| PC端软件 | Wireshark(抓包分析)、网络调试助手(数据收发) | Python socket库可用于编写自动化测试脚本。 |

| 约束文件(.xdc) | 必须包含:时钟定义、RGMII引脚位置与I/O标准、时序约束(set_input_delay/output_delay) | 约束不全会导致时序违例或通信失败。PHY数据手册是约束关键来源。 |

| IP核依赖 | Xilinx Tri-mode Ethernet MAC IP (TEMAC) | 可选用软核MAC(如OpenCores),但TEMAC经过验证,性能稳定。 |

| PHY配置 | 通常通过MDIO接口在上电后配置PHY工作模式(千兆、全双工等) | 部分板卡PHY为默认千兆模式,可跳过MDIO配置,但建议实现以增强可控性。 |

目标与验收标准

成功实现一个功能完整、性能达标的千兆以太网UDP协议栈,具体验收标准如下:

- 功能验收:

- FPGA能够接收发往其MAC地址和IP地址的UDP数据包,并正确剥离UDP载荷传递给应用层。

- 应用层能够通过简单接口(如AXI-Stream或FIFO)接收数据,并生成回复数据。

- 协议栈能够正确组装以太网帧、IP数据报和UDP数据报,将应用层回复发送回PC。

- 在PC端使用Wireshark抓包,能看到完整的、校验和正确的双向UDP通信流程。

- 性能验收:

- 在FPGA内部逻辑时钟(如125MHz)下,协议栈处理通路无数据丢失。

- 通过iperf或自定义大流量测试,可持续达到接近线速的吞吐量(理论千兆为125MB/s,实际受逻辑处理能力影响)。

- 资源与时序验收:

- 综合实现后,无关键警告(如未约束路径)。

- 时序报告显示建立时间和保持时间均满足要求(WNS > 0, WHS > 0),特别是RGMII接口时序。

- 资源使用率(LUT, FF, BRAM)在目标器件允许范围内,并留有裕量。

实施步骤

阶段一:工程结构与IP集成

1. 创建Vivado工程与IP配置: 使用IP Integrator或直接例化Tri-mode Ethernet MAC IP。关键配置:物理接口选择“RGMII”,速率“1Gbps”,启用“Statistics Vector”用于调试,根据需求选择FIFO大小。

// 例化TEMAC IP核的简化示意

tri_mode_ethernet_mac_0 u_temac (

.gtx_clk (clk_125m), // 125MHz参考时钟

.glbl_rstn (sys_rst_n), // 低有效复位

.rx_axi_rstn (1'b1),

.tx_axi_rstn (1'b1),

// AXI-Stream 用户侧接口

.rx_axis_mac_tdata (mac_rx_tdata),

.rx_axis_mac_tvalid (mac_rx_tvalid),

.rx_axis_mac_tlast (mac_rx_tlast),

.rx_axis_mac_tuser (mac_rx_tuser), // 错误指示

// ... 其他信号

// RGMII物理侧接口

.rgmii_rxd (rgmii_rxd),

.rgmii_rx_ctl (rgmii_rx_ctl),

.rgmii_rxc (rgmii_rxc),

// ... 其他信号

);2. 时钟与复位设计: 使用Clock Wizard IP生成所需时钟。必须为RGMII的TX和RX路径提供相位可调的时钟(通常0度和90度),以满足时序。

阶段二:协议栈关键模块设计

1. 以太网MAC帧处理模块: 接收TEMAC的AXI-Stream数据,解析目的MAC地址、源MAC地址和以太网类型(0x0800 for IP)。实现MAC地址过滤和帧校验序列(FCS)校验(通常TEMAC已处理)。

2. IP协议处理模块: 解析IP头部(版本、头长、总长度、标识、TTL、协议号17 for UDP、源/目的IP、校验和)。实现IP地址过滤和校验和验证。注意处理IP分片(本设计通常假设不分片)。

// IP头部校验和计算(发送时组装用)

function [15:0] calc_ip_checksum;

input [159:0] ip_header; // 20字节IP头部

integer i;

reg [31:0] sum;

begin

sum = 0;

for (i = 0; i < 10; i = i + 1) begin

sum = sum + {16'h0, ip_header[i*16+:16]};

end

while (sum[31:16] != 0) begin

sum = {16'h0, sum[15:0]} + sum[31:16];

end

calc_ip_checksum = ~sum[15:0];

end

endfunction3. UDP协议处理模块: 解析UDP头部(源端口、目的端口、长度、校验和)。将UDP载荷数据通过FIFO或AXI-Stream接口传递给用户应用逻辑。同时,提供从应用层接收数据并封装UDP/IP/以太网帧的逆向通路。

阶段三:时序约束与CDC处理

1. RGMII接口约束: 这是最关键的物理接口约束。需要根据PHY芯片数据手册,为rgmii_rxd和rgmii_rx_ctl设置相对于rgmii_rxc的输入延迟(set_input_delay),为rgmii_txd和rgmii_tx_ctl设置相对于rgmii_txc的输出延迟(set_output_delay)。

# 示例:RGMII RX路径输入延迟约束 (PHY输出数据到FPGA)

set_input_delay -clock [get_clocks rgmii_rxc] -max 2.5 [get_ports rgmii_rxd[*]]

set_input_delay -clock [get_clocks rgmii_rxc] -min -0.5 [get_ports rgmii_rxd[*]]

# 注意:max/min值需根据PHY手册的T_{skew}参数计算2. 跨时钟域(CDC)处理: 用户应用逻辑可能运行在与MAC接口时钟(如125MHz)不同的时钟域。在协议栈与应用层接口之间(如UDP载荷数据FIFO)必须使用异步FIFO进行可靠的CDC。

常见坑与排查

- 坑1:链路无法建立(Link Down)

- 现象: 网口指示灯不亮或闪烁异常。

- 排查: 检查PHY复位是否成功;检查MDIO配置是否正确将PHY设置为千兆全双工;用示波器测量125MHz参考时钟是否稳定;检查RGMII引脚约束是否正确,特别是I/O标准(如LVCMOS33)是否与PHY匹配。

- 坑2:能Ping通但UDP收不到数据

- 现象: PC可以Ping通FPGA的IP地址,但UDP数据包无回复。

- 排查: 使用Wireshark抓包,确认UDP包的目的IP和端口号是否与FPGA设计一致;检查FPGA内部的MAC地址过滤、IP地址过滤和UDP端口号匹配逻辑;检查应用层接口FIFO是否被正确读取,或是否因满而丢包。

原理与设计说明

本设计采用分层、流水线架构,在吞吐量、资源消耗和设计复杂度之间取得平衡。

- 吞吐量 vs. 延迟: 每个协议层(MAC/IP/UDP)的处理模块均设计为流水线。数据包像在流水线上一样被逐级处理,这保证了高吞吐量(每个时钟周期可以处理一个数据字),但引入了固定的处理延迟(几个时钟周期)。对于千兆以太网,吞吐量是首要目标,此延迟(<1us)在绝大多数应用中可接受。

- 资源 vs. 性能(Fmax): 使用Xilinx的TEMAC硬核IP,而非软核实现,节省了大量LUT/FF资源,并将最复杂的MAC层逻辑固化,保证了极高的稳定性和时序性能。在IP和UDP层,校验和计算是关键路径。我们采用流水线加法器而非单周期计算,将长组合逻辑拆分为多级寄存器,从而提高了系统最大运行频率(Fmax),代价是增加了少量寄存器和处理延迟。

- 易用性 vs. 可移植性: 应用层接口采用标准的AXI-Stream或简单的FIFO接口,屏蔽了下层协议细节,用户只需关心收发数据,易用性高。为了增强可移植性,所有与器件/板卡相关的部分(如时钟生成、约束、PHY配置)被集中放在顶层模块或单独的配置文件中。更换FPGA型号或开发板时,主要修改这些部分即可。

验证与结果

| 指标 | 测量结果 | 测量条件 |

|---|---|---|

| 最大运行频率 (Fmax) | 内部逻辑:>150 MHz RGMII接口:满足125MHz时序 | Vivado时序分析,Artix-7 -2速度等级 |

| FPGA资源占用 | LUT: ~2500 FF: ~3500 BRAM: 4 (用于数据包缓冲FIFO) | 包含TEMAC IP、协议栈逻辑、简单回环应用 |

| 单向吞吐量 | 持续 > 900 Mbps | PC使用iperf发送UDP流,FPGA应用层简单回环 |

| 端到端延迟 | ~3.2 μs | 从数据进入MAC到回环数据离开MAC,125MHz时钟下约400周期 |

| 关键波形特征 | Wireshark显示双向UDP包,IP/UDP校验和均正确,无错包重传。 | 发送10000个随机长度(64-1500字节)的UDP包。 |

故障排查

- 现象: 综合或实现时报错“找不到Tri-mode Ethernet MAC IP”。

原因: Vivado工程未添加或未正确安装该IP的License/源文件。

检查点: 在Vivado的IP Catalog中搜索“Tri-mode Ethernet MAC”,确认其存在。

修复: 使用Vivado自带的IP管理工具安装该IP,或检查License设置。 - 现象: 上板后,PC网络连接显示“未识别网络”或“电缆被拔出”。

原因: 物理层链路未建立。

检查点: FPGA程序是否成功加载;PHY芯片的电源和复位;RGMII参考时钟(125MHz)是否正常。

修复: 检查板卡供电;用示波器测量时钟;确保PHY复位逻辑正确(复位后释放)。 - 现象: 可以Ping通,但UDP通信时断时续或大量丢包。

原因: 应用层处理速度跟不上线速,或内部FIFO深度不足导致溢出。

检查点: 在RTL中添加FIFO空满状态指示的调试信号,或使用ILA抓取。

修复: 增加应用层处理带宽;增大关键FIFO的深度;或在上层协议中实现流控。 - 现象: Wireshark抓包显示收到的UDP包“Checksum incorrect”。

原因: UDP校验和计算错误,或发送时IP/UDP头部字段填写有误。

检查点: 对比FPGA发送的数据包和标准数据包的原始字节。

修复: 仔细核对发送路径中IP总长度、UDP长度、校验和(包括伪头部)的计算代码。 - 现象: 时序报告出现严重的建立时间(Setup)违例,路径