AXI4-Stream是AMBA协议家族中专为高效流数据传输设计的核心协议,在视频处理、通信和高速数据采集等领域应用广泛。本指南旨在提供一个从理论到实践的完整实施路径,通过一个具体的视频流传输项目,系统讲解如何在FPGA中设计、实现并验证一个功能完备的AXI4-Stream接口,确保设计的正确性、时序收敛与可验证性。

快速开始

本指南将引导您完成一个基于AXI4-Stream协议的视频流传输系统构建。您将设计一个视频时序发生器作为Master,一个FIFO作为Slave,并通过仿真与上板调试验证整个数据通路。

前置条件与环境

- 硬件平台:推荐使用集成ARM处理器或原生支持AXI总线的FPGA开发板,例如Xilinx Zynq-7000系列或Intel Cyclone V SoC。

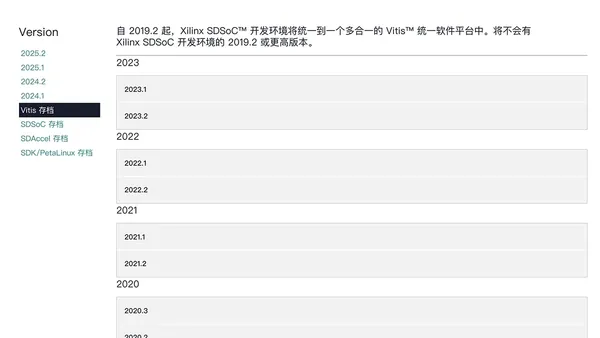

- 软件工具:建议使用近三年内的稳定版本开发套件,如Vivado或Quartus Prime。

- 时钟与复位:系统主时钟通常设置为100MHz,但需根据目标视频分辨率调整。复位信号应采用低电平有效、异步复位同步释放的设计模式。

- 视频源与接收:视频源可使用内部彩条生成器模块,接收端可连接HDMI TX等视频输出IP核。

- 必备工具:精确的时序约束文件与在线调试工具(如Vivado ILA或Quartus SignalTap II)为项目成功的关键。

目标与验收标准

- 功能正确性:Master能依据视频时序正确产生像素数据与握手信号(tvalid, tlast);Slave能无误接收;整个握手过程严格遵循AXI4-Stream协议,无死锁或数据丢失。

- 性能指标:数据通路在目标时钟频率下无时序违例,实际带宽能满足视频流理论需求。

- 资源占用:逻辑与存储资源(如LUT、FF、BRAM)消耗在合理预期范围内。

- 验证结果:仿真波形与上板实测波形一致,系统能稳定驱动下游IP显示无闪烁、无错位的图像。

实施步骤

阶段一:工程结构与接口定义

- 创建清晰的工程目录结构,区分设计文件、约束文件、仿真脚本与IP核目录。

- 定义顶层模块及AXI4-Stream Master接口。核心信号必须包括:时钟(aclk)、复位(aresetn)、数据(tdata)、数据有效(tvalid)、接收就绪(tready)、数据包结束(tlast)。

- 关键点:在顶层对异步复位信号进行同步释放处理;确保tlast信号的生成逻辑与视频行结束时刻严格对齐。

阶段二:关键模块设计

- AXI4-Stream Master(视频时序发生器):设计一个状态机或计数器,在视频有效图像区域内产生连续的像素数据(如彩条)。tvalid信号应仅由Master内部的数据准备状态驱动,独立于Slave的tready信号。这是实现协议解耦的基础。

- AXI4-Stream Slave(数据缓冲):建议直接使用Vivado或Quartus提供的FIFO IP核。配置时,务必开启AXI4-Stream接口模式,并勾选传递tlast信号的选项。FIFO深度需至少能缓冲一整行视频数据,以平滑上下游速率差异。

阶段三:时序约束与跨时钟域处理

- 时钟约束:为系统主时钟创建基准约束(create_clock)。

- I/O延迟约束:若AXI4-Stream接口连接至片外器件或另一时钟域,必须设置合理的输入延迟(set_input_delay)和输出延迟(set_output_delay)。

- 跨时钟域处理:若视频像素时钟与AXI4-Stream接口时钟不同源,则构成跨时钟域传输。此时,像素数据必须通过异步FIFO进行安全传递,相关的帧/行同步控制信号需经过同步器(两级寄存器)处理,以避免亚稳态。

阶段四:仿真验证

编写Testbench,重点模拟“背压”场景:在仿真中随机或周期性地将Slave的tready信号拉低,验证Master的tvalid和tdata能否在tready无效时保持稳定,并在tready恢复有效后继续正确传输数据。这是检验协议握手逻辑健壮性的核心测试。

阶段五:上板调试

- 使用ILA/SignalTap抓取AXI4-Stream接口的关键信号波形。

- 观察要点:

1. tvalid为高时,tdata是否连续变化?

2. 每次tvalid与tready同时为高的时钟沿,是否代表一次成功的数据传输?

3. 每行视频的最后一个像素数据,其对应的tlast信号是否为高?

原理与机制分析

AXI4-Stream协议的核心是TVALID/TREADY握手机制。TVALID由数据发送方(Master)控制,表示数据有效;TREADY由数据接收方(Slave)控制,表示可以接收。只有当两者在同一个时钟上升沿同时为高时,数据传输才发生。这种机制完美解耦了生产者和消费者的速率,但也在设计中引入了几个关键权衡点:吞吐量与延迟的平衡(FIFO深度)、资源消耗与最高运行频率的取舍、以及代码的易用性与在不同平台间的可移植性。

验证结果

一个成功的实现应达成以下结果:设计在目标器件上达到或超过预期的运行频率;逻辑与存储资源占用符合预估;仿真显示数据吞吐率达到理论带宽;上板实测带宽满足视频流需求,且握手效率(有效传输周期占比)较高,系统能长时间稳定工作。

故障排查指南

- 无数据传输:检查握手是否僵持。常见原因是Slave的tready始终为低,或Master的tvalid因内部逻辑错误未能拉高。

- 图像错位或撕裂:重点检查tlast信号是否生成错误,或跨时钟域同步处理不当,导致帧/行同步信号错拍。

- 时序违例:检查输出路径逻辑是否过于复杂,优化关键路径,或重新评估时钟频率是否合理。

- 上板图像不稳定(闪烁、雪花):高度怀疑亚稳态问题。检查所有跨时钟域信号是否都通过了正确的同步器或异步FIFO处理。

- FIFO溢出或读空:调整FIFO深度,或分析上下游数据速率是否匹配,优化数据产生/消耗逻辑。

- 资源占用异常:检查代码是否被综合出意外的锁存器,或IP核配置是否使用了不必要的大型资源模式。

扩展与优化

在完成基础功能后,可考虑以下扩展:为Master添加可配置的视频分辨率与帧率;实现多路AXI4-Stream流的仲裁与调度;将Slave端替换为DMA控制器,实现视频数据直接写入DDR内存;或集成更复杂的视频处理IP(如缩放、色彩空间转换),构建完整的视频处理流水线。

参考资源

- ARM® AMBA® 4 AXI4-Stream Protocol Specification

- Xilinx PG146: AXI4-Stream Infrastructure IP Suite

- Intel Avalon® Streaming Interface Specifications

附录:关键信号列表

| 信号名 | 方向(Master侧) | 描述 |

|---|---|---|

| ACLK | 输入 | 全局时钟信号 |

| ARESETn | 输入 | 全局复位,低电平有效 |

| TVALID | 输出 | 主设备驱动,表示数据有效 |

| TDATA[W-1:0] | 输出 | 数据总线,宽度可配置 |

| TREADY | 输入 | 从设备驱动,表示可接收数据 |

| TLAST | 输出 | 包边界指示,如一行视频结束 |