嘿,同学!如果你正在电子、通信、计算机或自动化等专业“打怪升级”,那么全国大学生FPGA创新设计赛(简称FPGA大赛)绝对是你不能错过的“高级副本”。它不只是一场考试,更像是一个能让你把课本知识变成真本事的“练功房”。从算法设计、写代码(Verilog/VHDL)、仿真调试到把程序“烧”进板子里跑起来,这一整套流程走下来,你的“全栈能力”会得到质的飞跃——这正是我们成电国芯FPGA培训一直强调的核心。更重要的是,这段闪闪发光的竞赛经历,会成为你考研复试或求职面试时,最有力的“秘密武器”。

一、读懂题目:别急着写代码,先“拆解”它

FPGA大赛的题目往往很“潮”,紧贴AI加速、图像处理、通信、工业控制这些前沿领域。题目通常是开放式的,给你一块开发板,让你去实现一个具体的功能或系统。

1. 你会遇到哪些题型?

- 算法加速类:比如给CNN卷积层、FFT变换或者排序算法做个“硬件加速引擎”。这考的是你怎么把软件算法“翻译”成高效的并行硬件结构,既要跑得快,又要省资源。

- 信号处理与通信类:设计数字滤波器、实现QPSK调制解调,或者搞一个以太网通信栈。这里很考验你对通信原理的理解和对时序逻辑的精准把控。

- 控制与接口类:用FPGA控制电机、做PID控制器,或者驱动VGA/HDMI屏幕显示。你需要熟悉SPI、I2C这些外设“对话”协议,并把它们整合成一个系统。

- 创新应用类:结合AIoT、边缘计算等概念,设计像智能小车视觉系统、语音识别终端这类好玩的项目。这类题目更看重你的创意和构建完整系统的能力。

2. 破题三步法,帮你理清思路

看到题目千万别一头扎进代码里!我们建议你分三步走:

- 需求细化:把大赛描述里可能有点“模糊”的要求,变成清晰、可量化的技术指标。比如处理速度要多快?精度要求多少?FPGA的资源(像LUT、寄存器)能用多少?

- 方案调研:去查查有没有现成的开源设计(IP核)或者论文里的高效结构。结合自己团队的实力,选择一个最可行的实现架构,比如是用流水线,还是状态机,或者多核并行?

- 模块划分:用“自顶向下”的思路,把整个系统像搭积木一样分成几个功能模块。最关键的是,要严格定义好模块之间怎么“握手”、数据多宽、时钟是否同步。这一步做好了,团队协作和后期调试会顺利很多。

二、备赛全攻略:从找队友到最终答辩

1. 组队:找到你的“神队友”(备赛初期)

一个理想的团队,通常需要这三种角色:

- “军师”/算法担当:负责核心算法研究和系统方案设计,需要理论扎实,有大局观。

- “码农”/RTL实现担当:负责用Verilog把设计“敲”出来,并进行模块仿真。需要代码写得规范、严谨,对时序和资源消耗特别敏感。

- “侦探”/验证调试担当:负责搭建测试环境、上板调试、整理文档。需要耐心细心,有强大的“抓Bug”能力。

大家技能可以各有侧重,但最好都对整个流程有基本了解,这样沟通起来才没有障碍。培养这种“一专多能”的工程师,正是成电国芯课程设计的初衷。

2. 技能升级:这些“内功”必须练(备赛中期)

- 写好Verilog代码:竞赛不是搞研究,代码的可读性、可维护性很重要。学习好的编码风格,比如寄存器输出、同步设计、合理地使用状态机。

- 掌握仿真与调试:玩转ModelSim或Vivado Simulator,学会写能自动检查结果的测试平台。记住,“仿真通过”不等于“板上成功”,但我们要争取把90%的问题在仿真阶段就解决掉。

- 理解时序约束:搞懂建立时间和保持时间,学会写基本的时序约束文件(.xdc或.sdc)。这是让你的系统稳定跑在高频的关键,也是高手和新手的重要分水岭。

- 熟练使用工具:深入掌握一种主流开发工具(Vivado或Quartus),包括使用IP核、抓取波形调试(ILA/ChipScope)、分析功耗等等。

3. 最后冲刺:打磨作品,准备答辩(备赛后期)

- 文档与展示:技术报告和答辩PPT是评委了解你工作的窗口。逻辑要清晰,重点突出你的创新点、遇到的难点以及怎么解决的。多用图表、波形图、实物照片,少用大段文字,量化性能指标(比如比软件快了多少倍)最有说服力。

- 稳定性测试:进行长时间、各种边界条件下的“压力测试”。一个偶尔会出错的炫酷功能,得分可能还不如一个百分百稳定的基础功能。

- 模拟答辩:反复演练,控制好时间。提前想想评委可能会问什么技术细节,比如“为什么这里选用这个算法?”“当时出现时序违例,你是怎么解决的?”

三、获奖学长学姐是怎么做的?

我们分析了成电国芯多位获奖学员的案例,发现了他们的成功秘诀:

案例一:轻量化CNN图像识别系统(全国一等奖)

- 精准选题:抓住了“边缘AI”的热点,但把范围缩小到“轻量化”和“特定场景(如交通标志识别)”,避免了题目太大做不完。

- 软硬协同优化:没有简单照搬TensorFlow模型,而是对网络进行了“瘦身”(剪枝、量化),并设计了高效的脉动阵列来做卷积计算,大大提升了能效比。

- 打造完整系统:不仅做了加速核,还搭建了从摄像头采集、图像预处理、加速计算到LCD显示的全套系统,展示了强大的工程实现能力。

案例二:高精度数字锁相放大器(全国二等奖)

- 吃透理论:团队花了很多时间深入研究锁相放大原理,从而设计出了更优的数字解调结构。

- 重视基础模块:在滤波器设计和噪声抑制这些看似“不起眼”的模块上下足了功夫。正是这些扎实的工作,保证了系统的高精度,给评委留下了严谨的印象。

- 用数据说话:在报告和答辩中,用了大量对比数据(比如信噪比提升多少、测量误差降低多少)来证明自己方案的优越性,说服力爆表。

四、你的竞赛之路,成电国芯来助力

备赛路上挑战不少,但你绝不是一个人在战斗。成电国芯FPGA培训平台希望能为你提供这些支持:

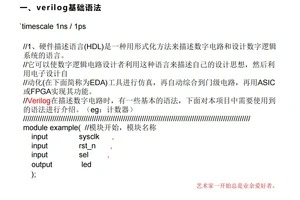

- 系统课程:从Verilog语法、仿真验证,到FPGA设计进阶、高速接口、SOPC,帮你构建完整的知识体系,弥补课堂学习的不足。

- 项目实战:我们准备了多个从易到难的真实项目(比如数字钟、VGA显示、简易CPU、图像处理器),让你在动手实践中巩固技能,积累经验。这些项目本身也是绝佳的竞赛素材。

- 竞赛专题辅导:定期开设竞赛专题直播和讲座,由有获奖经验的讲师为你解析历年赛题、分享备赛技巧、在线答疑。

- 社区与答疑:加入我们的学员社区,和全国各地的FPGA爱好者一起交流。当你遇到技术瓶颈时,能快速得到帮助。

最后想对你说:

参加FPGA大赛,是一次对技术、毅力和团队合作的全面锻炼。获奖当然值得开心,但备赛过程中收获的硬核技能、工程思维和解决问题的能力,才是你未来职业发展中真正的“财富”。别犹豫了,从现在开始规划,系统学习,勇敢组队,深入实践吧!成电国芯愿意成为你FPGA探索之路上的得力伙伴,助你在竞赛的舞台上闪闪发光,赢在起跑线上。