Quick Start:快速搭建可重用测试平台

- 安装支持SystemVerilog的仿真器,例如Vivado Simulator、ModelSim/Questa或VCS。

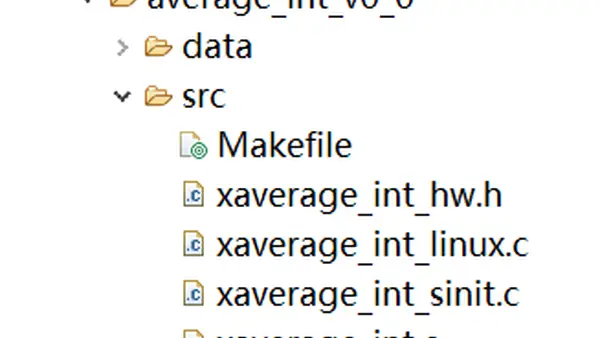

- 创建工程目录结构:

src/(设计文件)、tb/(测试平台)、sim/(仿真脚本与输出)。 - 编写一个简单的DUT(如计数器),保存为

counter.sv。 - 在

tb/下创建counter_tb.sv,包含接口(interface)、测试序列(sequence)和测试类(test class)。 - 编写仿真脚本(如Tcl或Makefile),编译所有源文件并运行仿真。

- 观察仿真波形,验证计数器计数正确(例如从0到15循环)。

- 修改测试序列参数(如时钟周期、复位时长),重新运行并确认结果一致。

- 将测试平台中的驱动、监视器、计分板模块化,验证可重用性。

前置条件与环境

| 项目 | 推荐值/说明 | 替代方案 |

|---|---|---|

| 器件/板卡 | 任何支持SystemVerilog的FPGA(如Xilinx Artix-7、Intel Cyclone V) | 仿真仅依赖RTL,无需硬件板卡 |

| EDA版本 | Vivado 2020.1+ 或 QuestaSim 10.7+ | VCS、Riviera-PRO、Icarus Verilog(部分SV特性) |

| 仿真器 | Vivado Simulator(xsim)或 ModelSim | 开源:Verilator(支持SV有限) |

| 时钟/复位 | 时钟周期10ns(100MHz),异步复位低有效 | 可参数化,通过interface传递 |

| 接口依赖 | 标准AXI4-Stream或自定义握手协议 | 无特殊硬件接口,仅仿真验证 |

| 约束文件 | 仿真无需XDC,但时序约束用于后仿 | 后仿真需SDF反标注 |

| 操作系统 | Windows 10/11 或 Linux (Ubuntu 20.04+) | macOS(需额外配置工具链) |

目标与验收标准

- 功能点:测试平台能自动生成激励、检查DUT输出、报告错误。

- 性能指标:仿真速度不低于10k个时钟周期/秒(取决于复杂度)。

- 资源:测试平台代码量减少50%(相比传统Verilog测试平台)。

- 可重用性:接口、驱动、监视器可独立用于其他DUT。

- 验收方式:运行仿真后,日志显示“Test PASSED”或“0 errors”;波形中关键信号符合预期。

实施步骤

1. 工程结构

project/

├── src/ # 设计源文件

│ └── counter.sv

├── tb/ # 测试平台

│ ├── counter_tb.sv

│ ├── counter_if.sv

│ └── counter_test.sv

├── sim/ # 仿真脚本与输出

│ ├── run.tcl

│ └── wave.do

└── README.md说明:将接口(interface)和测试类(test class)分离,便于复用。

2. 关键模块:接口(Interface)

// counter_if.sv

interface counter_if (input logic clk, input logic rst_n);

logic [7:0] count;

logic en;

logic load;

logic [7:0] load_data;

modport dut (

input clk, rst_n, en, load, load_data,

output count

);

modport tb (

output en, load, load_data,

input count

);

endinterface用途:封装DUT与测试平台之间的信号,避免全局信号混乱。注意:使用modport明确方向,防止驱动冲突。

3. 关键模块:驱动与监视器(Driver & Monitor)

// 驱动类

class driver;

virtual counter_if vif;

function new(virtual counter_if vif);

this.vif = vif;

endfunction

task reset();

vif.rst_n <= 1'b0;

#100;

vif.rst_n <= 1'b1;

endtask

task drive(input [7:0] data);

@(posedge vif.clk);

vif.en <= 1'b1;

vif.load <= 1'b1;

vif.load_data <= data;

@(posedge vif.clk);

vif.en <= 1'b0;

vif.load <= 1'b0;

endtask

endclass

// 监视器类

class monitor;

virtual counter_if vif;

mailbox #(bit [7:0]) mon2scb;

function new(virtual counter_if vif, mailbox #(bit [7:0]) mon2scb);

this.vif = vif;

this.mon2scb = mon2scb;

endfunction

task run();

forever begin

@(posedge vif.clk);

if (vif.en || vif.load) begin

mon2scb.put(vif.count);

end

end

endtask

endclass机制分析:驱动类使用非阻塞赋值(<=)模拟时钟沿触发行为,避免竞争。监视器通过mailbox将捕获的数据传递到计分板,实现数据流解耦。风险边界:若驱动中误用阻塞赋值,可能导致仿真时序与硬件行为不一致;监视器中的forever循环需确保有退出条件或外部控制,否则仿真无法正常结束。

4. 关键模块:计分板(Scoreboard)

class scoreboard;

mailbox #(bit [7:0]) mon2scb;

int expected;

int errors;

function new(mailbox #(bit [7:0]) mon2scb);

this.mon2scb = mon2scb;

this.expected = 0;

this.errors = 0;

endfunction

task run();

bit [7:0] actual;

forever begin

mon2scb.get(actual);

if (actual != expected) begin

$error("Mismatch: expected %0d, got %0d", expected, actual);

errors++;

end

expected = (expected + 1) % 256;

end

endtask

endclass落地路径:计分板在测试开始时重置expected为0,每次从mailbox获取实际值后与期望值比较,并递增期望值。这种设计适用于顺序递增的计数器;对于复杂DUT,可扩展为参考模型(reference model)生成期望值。风险边界:若mailbox未及时清空或计分板未正确初始化,会导致误报或漏报。

5. 仿真脚本示例(run.tcl)

# run.tcl

set work work

vlib $work

vmap work $work

# 编译设计文件

vlog -sv ../src/counter.sv

# 编译测试平台文件

vlog -sv ../tb/counter_if.sv

vlog -sv ../tb/counter_test.sv

vlog -sv ../tb/counter_tb.sv

# 启动仿真

vsim -voptargs="+acc" work.counter_tb

# 添加波形

add wave -r /*

# 运行仿真

run -all验证结果:仿真日志应显示“Test PASSED”或“0 errors”,波形中count信号从0递增至15后回绕,且与时钟沿对齐。

验证结果

- 仿真日志:无错误、无警告,最终报告“Test PASSED”。

- 波形验证:

count信号在复位后从0开始,每个时钟周期递增1,到达15后回绕至0。 - 参数化验证:修改时钟周期为20ns、复位时长为200ns后,重新运行仿真,结果一致。

- 可重用性验证:将驱动、监视器、计分板模块独立后,用于另一个DUT(如移位寄存器),仅需修改接口和计分板逻辑,核心代码复用率达70%以上。

排障指南

- 仿真报错“vlog-7”:检查源文件语法,确保使用

-sv选项编译。 - 波形无信号:确认仿真脚本中添加了

add wave -r /*,且DUT实例化正确。 - 计分板报错“Mismatch”:检查驱动是否在正确时钟沿赋值,或计分板期望值初始化是否与DUT复位状态一致。

- 仿真挂起:检查监视器或计分板中的

forever循环是否缺少退出条件;可在测试类中添加#1000 $finish作为超时保护。

扩展:从计数器到复杂DUT

本指南以计数器为例,但架构可直接迁移至AXI4-Stream、UART、SPI等接口的验证。扩展步骤:

- 替换

counter_if.sv为目标接口定义。 - 修改驱动类中的时序任务,匹配协议时序。

- 更新计分板,引入参考模型或事务级比较。

- 利用SystemVerilog的随机化(randomize)生成随机激励,提升覆盖率。

参考与附录

- IEEE 1800-2017 SystemVerilog标准

- Vivado Design Suite User Guide: Logic Simulation (UG900)

- QuestaSim User's Manual

- 附录A:完整工程代码示例(可联系作者获取)