一、FPGA是什么

FPGA是可编程逻辑门阵列(Field-Programmable Gate Array)的缩写,作为一种可编程集成电路芯片,其核心优势的在于逻辑门及互连关系可通过编程灵活配置与重配置,无需依赖物理层面的切换与连接来定义电路功能,这一特性使其区别于传统固定功能集成电路。

在硬件设计与嵌入式系统领域,FPGA凭借高性能、低功耗及可重构性的核心优势,已广泛应用于计算机视觉、数字信号处理、网络通信、医疗设备、航空航天、汽车电子、工业机器人等多个高端技术领域,成为核心硬件方案的重要选择。

从硬件结构来看,FPGA采用固定网格架构,由大量可编程逻辑块与可编程互连网络构成。其中,可编程逻辑块集成了可编程逻辑门、存储器单元、加法器、乘法器等基础逻辑元件,通过可编程互连网络实现各逻辑块的灵活连接,进而适配多样化、复杂化的逻辑功能实现需求。

凭借高度的可编程性与灵活性,FPGA在原型验证与快速开发场景中具备显著优势——设计人员可在硬件层面实现快速迭代测试,大幅缩短研发周期。同时,其可重复配置、重复复用的特性,也为构建可扩展硬件系统与通用硬件平台提供了便利。

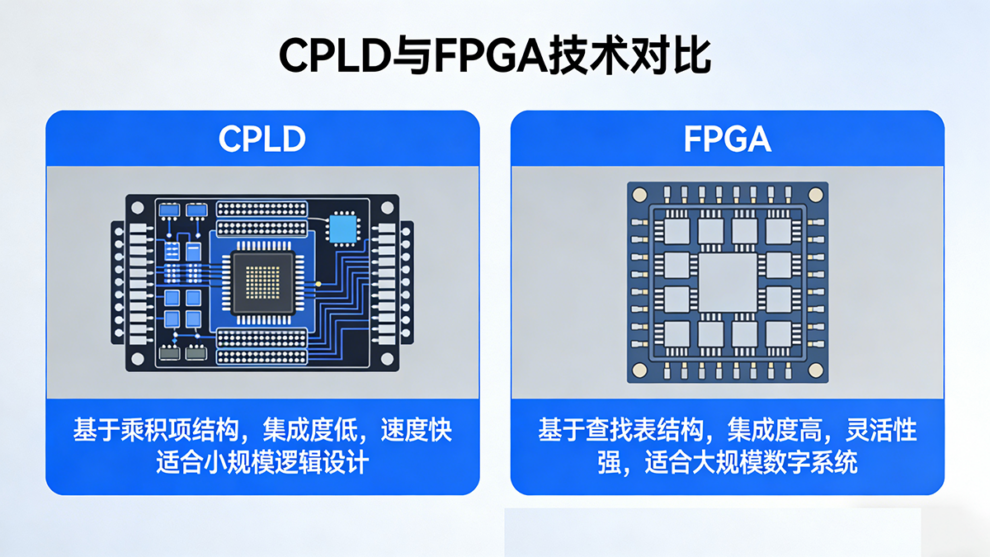

二、CPLD与FPGA的核心区别

CPLD与FPGA同属可编程逻辑芯片,二者核心差异集中在硬件结构、规模容量及适用场景上,需结合实际设计需求选择适配方案。

CPLD全称为复杂可编程逻辑器件(Complex Programmable Logic Device),其硬件结构以若干大规模可编程逻辑块为核心,通过可编程互连网络实现逻辑块间的连接。相较于FPGA,CPLD的单个逻辑块规模更大,但整体芯片规模偏小,更适用于中等规模数字逻辑电路的实现。在性能层面,CPLD具备低功耗、低成本的优势,同时可提供与FPGA相近的灵活性与可编程性,在中小规模控制逻辑、接口适配等场景中应用广泛。

如前文所述,FPGA为可编程门阵列,以海量小型可编程逻辑块与高密度可编程互连网络为核心架构,天生适配大规模、高度并行的数字逻辑电路实现。尽管单个逻辑块规模小于CPLD,但FPGA整体芯片规模更大、资源更丰富,能够承载更为复杂的逻辑功能开发。其核心优势在于高性能、高可编程性与高并行处理能力,可满足高端算力需求,但相应的成本也高于CPLD。

综上,CPLD与FPGA的应用场景可大致划分:CPLD多用于中等规模、低功耗、低成本的数字逻辑设计;FPGA则聚焦于大规模、高性能、高并行度的复杂逻辑实现。不过在实际应用中,二者存在一定替代空间,最终需根据电路规模、性能指标、成本预算等核心需求综合决策。