FPGA工程师为什么这么难招?

作为一个在 FPGA 圈子里摸爬滚打了一年多的老鸟,看到 “为啥 FPGA 工程师这么难招” 这个问题,忍不住想结合自己的经历唠唠。咱先不说行业供需那些大道理,就从入门阶段的 “头秃” 体验说起吧。

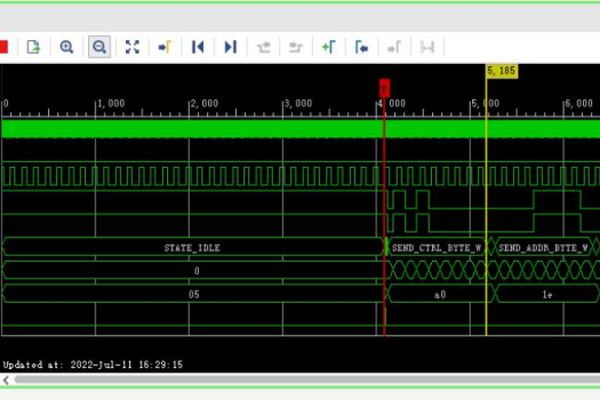

刚接触 FPGA 的时候,第一关就是 HDL 语言和硬件思维的双重门槛。你以为会写代码就行?太天真了!除了啃 Verilog 或者 VHDL,还得看懂原理图、会调硬件电路,对数字电路的底层逻辑得门儿清。举个例子,同样是写代码,C 语言是一条道走到黑的串行执行,而 HDL 里每个 always 块都是并行跑的,一不小心就会陷入 “代码能跑但时序全崩” 的陷阱。新手最容易犯的错就是照搬模板,结果写出来的代码资源浪费严重,覆盖率低到让人想砸键盘。这时候你才发现,光懂语法没用,得有硬件思维 —— 得盯着 RTL 视图分析数据流,像拼拼图一样琢磨每个模块怎么协同工作,没点耐心和悟性根本玩不转。

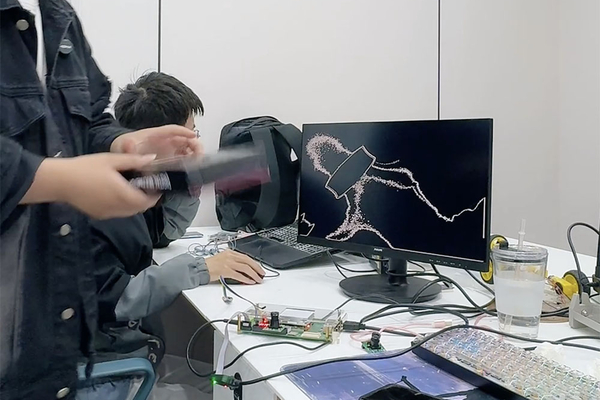

再看看高校教育这块。现在电子专业的学生,大部分要么扎堆学单片机、ARM 搞软件,要么死磕硬件设计,真正系统学 FPGA 的少之又少。为啥?老师自己都未必精通啊!高校里的教授大多忙着搞科研、发论文,能抽出时间教学生用 FPGA 工具的屈指可数。本科生阶段,能学到 “点亮数码管” 就算结课成就,研究生呢?导师接了 FPGA 相关的项目,往往直接甩给学生自己摸索,美其名曰 “锻炼能力”,实则全靠自学。这种环境下,除了少数自己啃资料、泡论坛的狠人,大部分学生根本没机会踏入这个门槛,更别说产生兴趣了。

而且 FPGA 这玩意儿,本质上是个 “工具 + 应用” 的复合体。你以为会写代码就能上岗?做图像开发得懂数字图像处理,做通信得啃通信原理,做信号处理得玩转 MATLAB 仿真和算法推导。企业招人的时候,动不动就要求 “熟悉 XX 领域应用”,相当于既要你会开车,还得懂修车,甚至得能根据路况改装车辆。这种复合型要求,直接把一大批停留在 “点亮 LED” 阶段的新手拒之门外,剩下的候选人里,能达到 “可用水平” 的,没个三五年实战经验根本拿不下来 —— 这也是为啥招聘信息里常挂着 “硕士以上”“3 年经验” 的原因。

再说企业这边的顾虑。FPGA 开发成本高得让人肉疼:一片 Xilinx K7 系列芯片,涨价前最便宜的 70T 都要七八十,要是用高端型号,成本直接上天。而且开发周期堪称 “时间杀手”:改个标点符号就得重新编译,项目大点的,编译一次花一两小时是家常便饭,i7+32G 的配置都得咬牙扛着。仿真结果和实际硬件运行经常 “两副面孔”,时序问题能让人熬秃头顶,最后还得实打实地上板测试,高低温老化、DDR 速率调试这些坑一个接一个,优化最后 10% 的性能比前面 90% 还费劲儿。资本都是逐利的,能靠 ARM、DSP 甚至纯硬件解决的问题,谁愿意在 FPGA 上砸时间砸钱?所以岗位本身就不多,企业招人时自然想找 “即插即用” 的熟手,最好一来就能扛项目,门槛自然水涨船高。

这几年情况有点变化:半导体行业火了,高性能计算、图像处理、通信设备这些领域对 FPGA 的需求蹭蹭涨,岗位数量明显多了。但尴尬的是,人才培养根本跟不上。FPGA 工程师的成长是 “慢工出细活”,从入门到独立做项目,没个三五年根本成不了气候。而市场需求突然爆发,导致行业里稍微有点经验的人立刻成了香饽饽 —— 大厂提前和高校实验室挂钩,直接预定研究生;中小公司只能靠高薪挖人,可资深工程师就那么些,挖完了就只能对着简历库叹气。更别说还有一部分人熬到资深后,转头投奔 IC 设计等薪资更高的领域,进一步加剧了人才缺口。

最后说点现实的:FPGA 工程师的工资在半导体行业里算中等偏上,但和互联网大厂比起来还是差点意思。好处是加班没那么狠 —— 毕竟编译代码就得半天,想加班都得等编译完不是?但架不住行业门槛高、成长慢,性价比一对比,很多应届生更愿意选容易入门、薪资更亮眼的方向。圈子就这么大,需求却越来越大,难招是必然的。

说到底,FPGA 工程师的难招,本质上是 “高门槛培养” 和 “爆发式需求” 的矛盾:入门难导致人才储备少,开发成本高导致岗位 “宁缺毋滥”,行业升温又放大了供需缺口。想破局?要么等高校教育跟上实战需求,要么盼着工具链优化降低门槛 —— 但在此之前,企业可能还得继续在人才市场里 “大海捞针”,而从业者嘛,继续在时序调试和代码编译中 “佛系脱发” 吧,手动狗头。

"愿我的文字能带给您一丝美好"

分享海报

FPGA工程师为什么这么难招?

作为一个在FPGA圈子里摸爬滚打了一年多的老鸟,看到“为啥FPGA工程师这么难招”这个问…

FPGA线上课程平台|最全栈的FPGA学习平台|FPGA工程师认证培训

FPGA在线学习平台

评论

A 为本文作者,G 为游客总数:0