一、文档实现功能介绍

本文档实现在 VIVADO 下面新建一个 FPGA 开发工程,然后采用时序和计数实现 LED 的流水显示, 工程新建方法请参考文档《开发软件安装和介绍/VIVADO简介及软件下新建ZYNQ工程教程》。

二、ZYNQ 工程建立

| 起始页(或file->Project->New) | 创建新工程(CreateNew Project) |

| 向导起始页面 | 点击 Next- > |

| ProjectName(工程名) | 工程名:fpga_01 _pl_led_stream工程路径: (自己选择,不要有中文路径)勾选Create ProjectSubdirectory,点击Next- > |

| AddSource(添加设计源文件) | 点击 Next- > |

| AddExsixtingIP(添加已有的 IP) | 点击 Next- > |

| AddConstraints(添加已有约束文件) | 点击 Next- > |

| DefaultPart(默认配置,芯片选型) | Family->Zynq-7000 Package- >clg400Speed->7010选-1,7020选-27010版本选择目标器件:xc7z010clg400-1 7020版本选择目标器件:xc7z020clg400-2点击 Next- > |

| NewProjectSummary(新建工程概况) | 确认工程信息,选型等,点击 Finish 完成 |

三、具体实现步骤

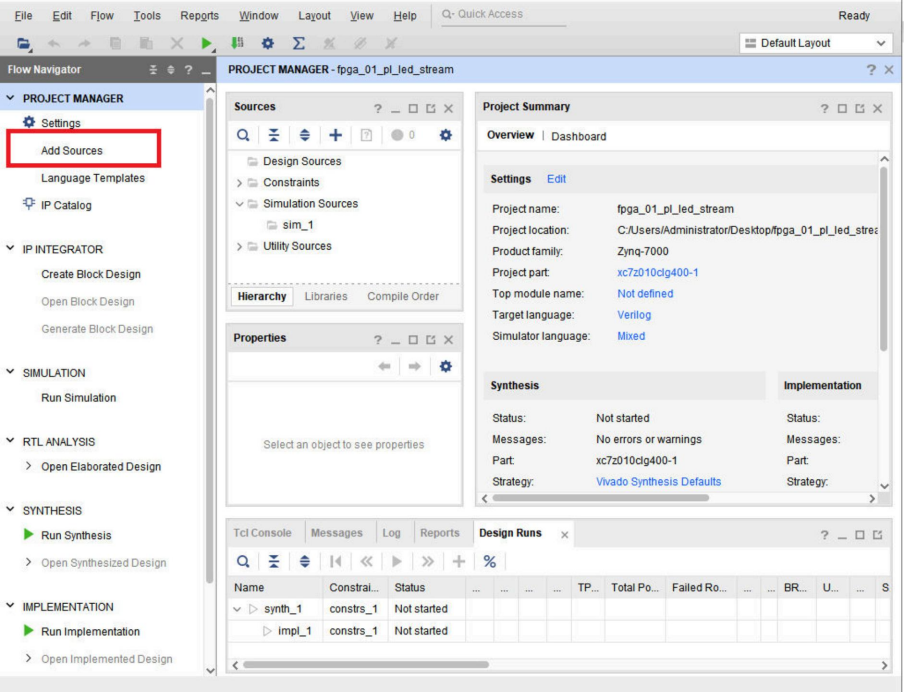

首先工程管理栏点击 Add Sources 添加我们需要编写设计的流水灯代码文件:

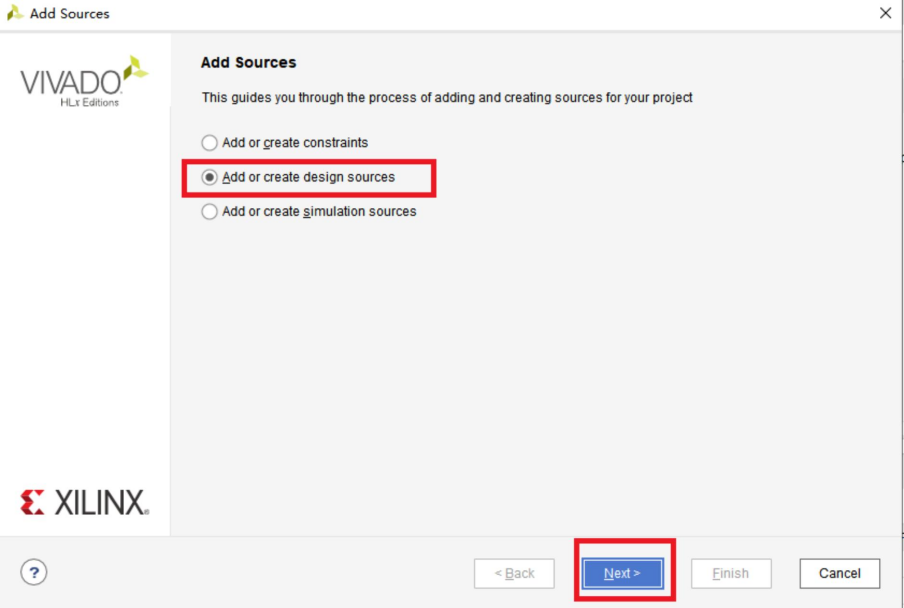

弹出的界面勾选Add or create design sources,表示添加或者新建一个设计文档,然后点击next:

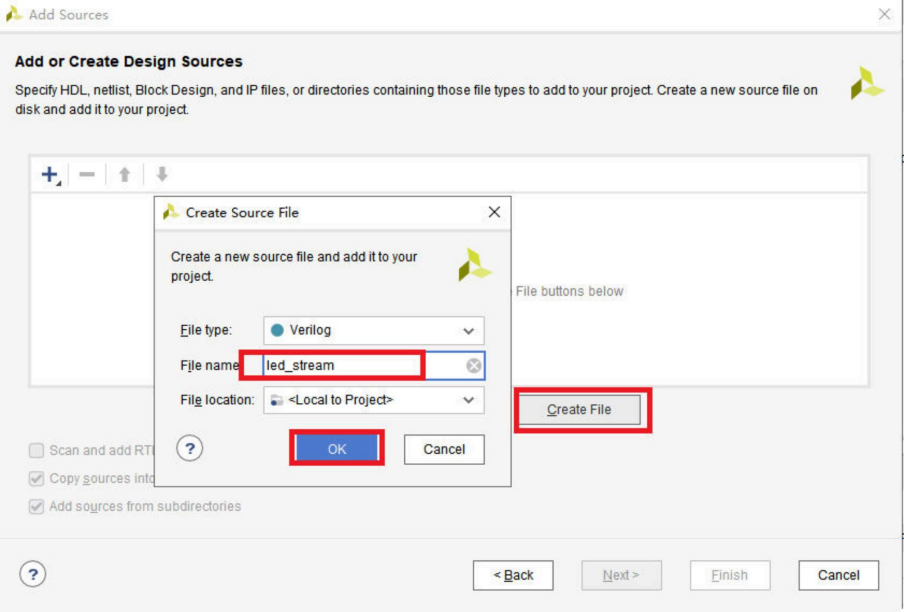

然后点击Create File,弹出的子对话框中,File Type默认是verilog,如果采用VHDL编写,则选择为VHDL。我们默认采用verilog。File Name填入verilog文件名,我们这里填入的是led_stream。然后点击OK。

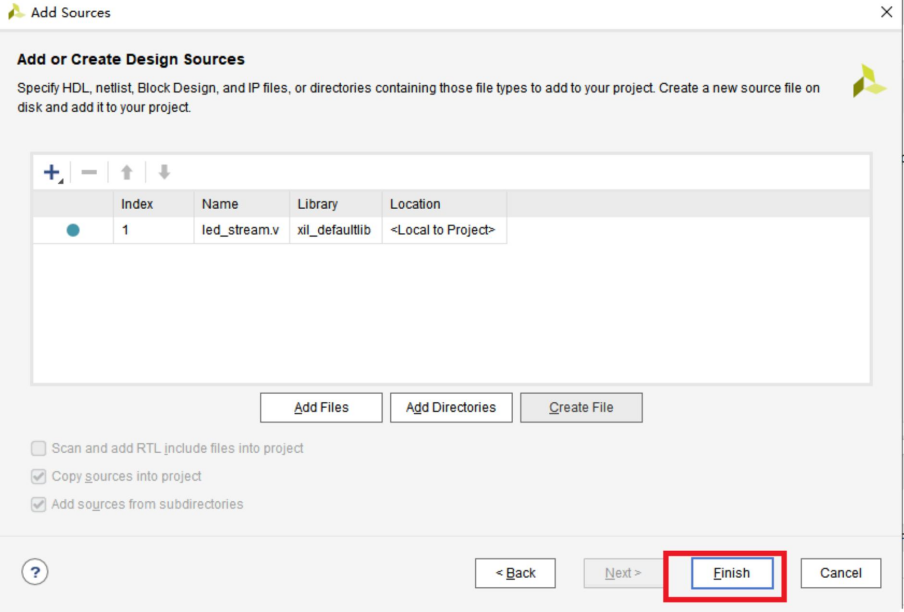

点击Finish完成文档创建。

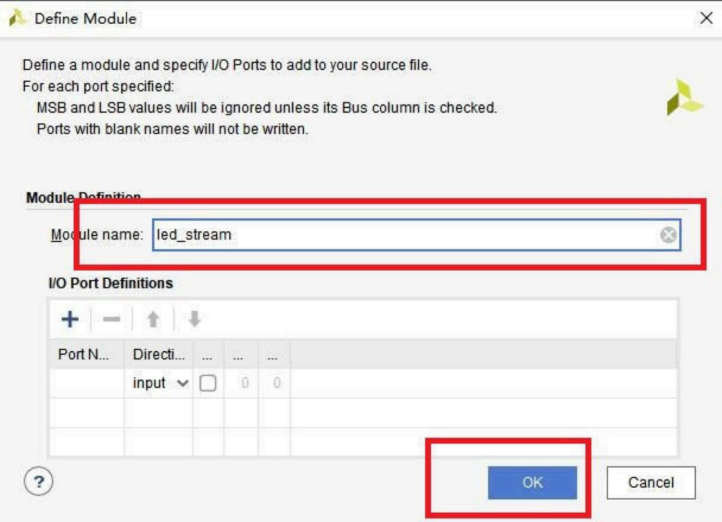

点击Finish之后,弹出对应文档的模块名称。这里我们默认led_stream,然后点击OK。

然后在弹出的对话框默认点击OK。

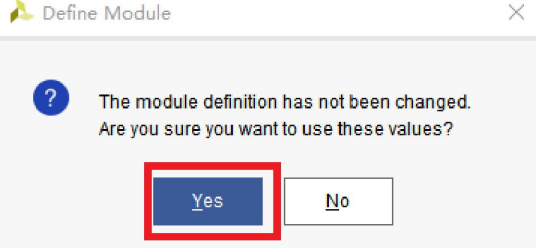

我们可以看到,led_stream模块和文档已经在设计文件层次窗口中。

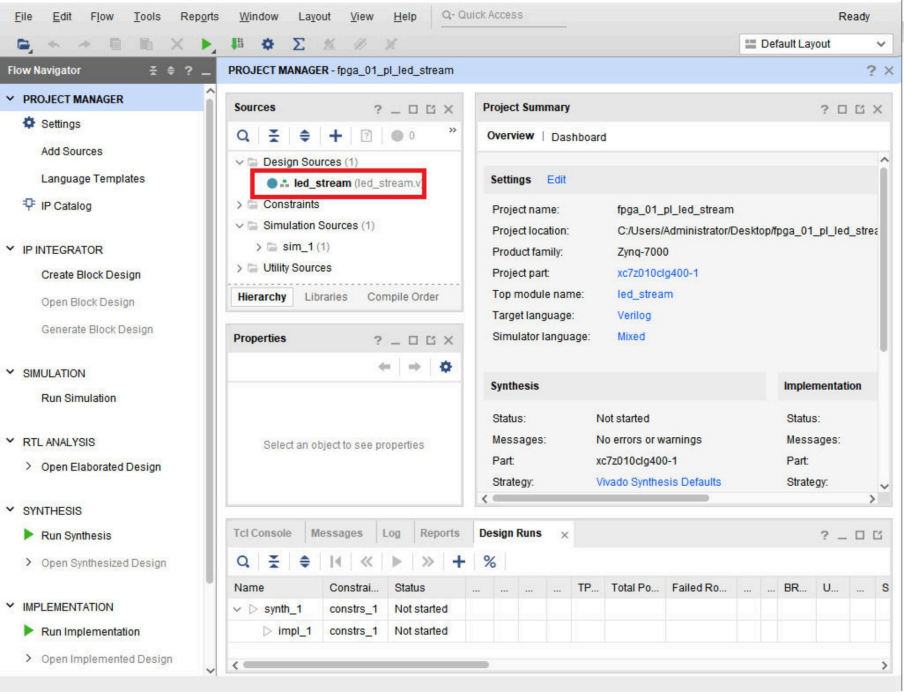

我们双击打开led_stream然后对其进行编辑,添加如下代码(代码请从对应的demo拷贝,这里拷贝pdf文字格式会发生变化):

module led_stream(

output reg [3:0] led, // LED4 to LED1, 1 on, 0 off

input clk, // FPGA PL clock, 50 MHz

input rst_n // FPGA reset pin

);

reg [31:0] cnt;

reg [1:0] led_on_number;

//clock input 50000000

parameter CLOCK_FREQ =50000000;

parameter COUNTER_MAX_CNT=CLOCK_FREQ/2-1; //change time 0.5s

always @(posedge clk, negedge rst_n) begin

if(!rst_n) begin

cnt <= 32'd0;

led_on_number <= 2'd0; end

else begin

cnt <= cnt + 1'b1;

if(cnt == COUNTER_MAX_CNT) begin//计数0.5s

cnt <= 32'd0;

led_on_number <= led_on_number + 1'b1;

end

end

end

always @(led_on_number) begin

case(led_on_number)

0: led <= 4'b0001;

1: led <= 4'b0010;

2: led <= 4'b0100;

3: led <= 4'b1000;

endcase

end

endmodule代码中,晶振使用的外部晶振,50M频率,所以CLOCK_FREQ为50*1000*1000,我们让一个计数器cnt从0计数到50M晶振频率下的半秒钟时间的值改变led输出,所以计数器最大值等于CLOCK_FREQ/2-1=24999999,即让led_on_number自动加1,然后清零重新计数。led_on_number为2位,到3之后变为0重新计数,led_on_number状态数值对应0-3范围,最终通过代码的case语句来选择点亮哪一个led,将四个LED对应的LED位置1。

开始综合,点击工程管理栏的Run Synthesis:

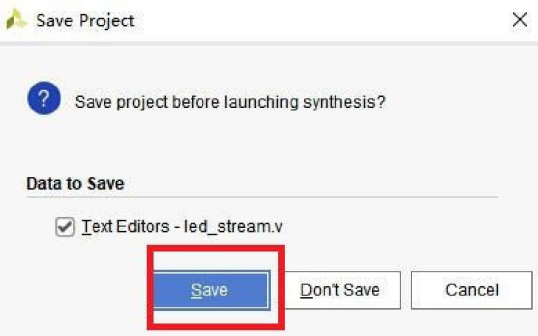

然后弹出的对话框点击Save:

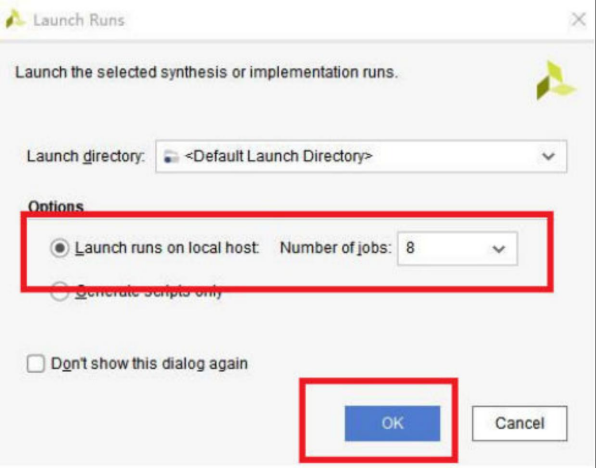

然后弹出的Launch Runs对话框根据电脑配置选择Jobs数量(代表综合消耗的进线程,VIVADO目前已验证过支持12线程,采用锐龙的R5-2600X处理器,因为它是6核12线程),由于这里电脑配置是I7-7700K,四核八线程,所以最多可以选择8个。综合过程很耗CPU性能,所以如果想要综合过程中流畅使用电脑,可以少选两个线程。选完线程数量,点击OK进行综合(综合过程很慢,请耐心等待):

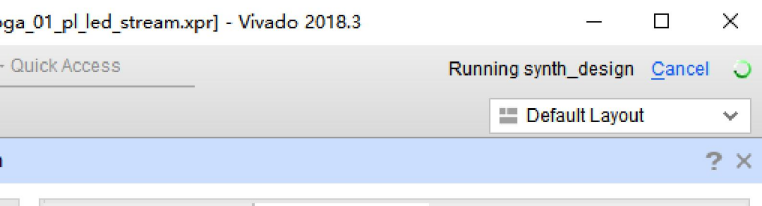

综合状态可以在右上角看到已经开始运行。

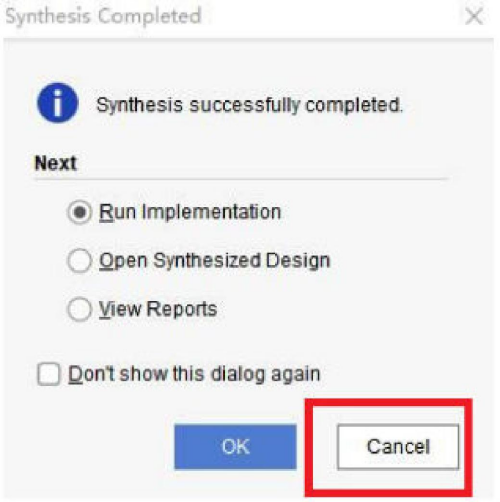

完成综合后,弹出的综合完成对话框中我们点击Cancel取消。不要进行Implementation。

四、引脚绑定

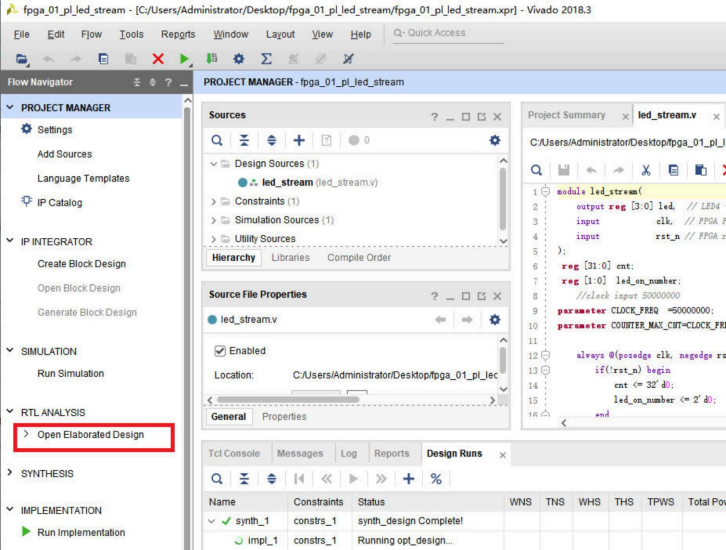

由于我们还没有进行管脚绑定,所以我们需要先绑定管脚在进行Implementation实现,最后布局布线最后生成BIT文件。我们接下来进行绑定管脚。我们点击工程管理栏的RTL ANALYSIS下面的>open Elaborated Design:

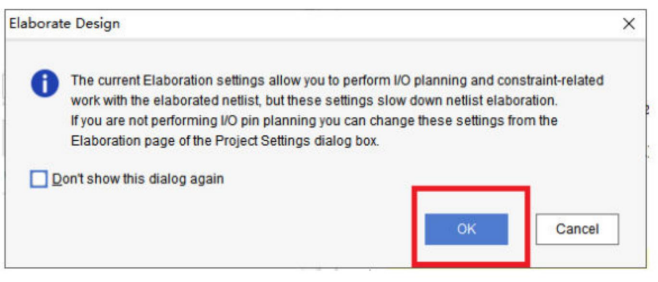

弹出的对话框我们选择OK:

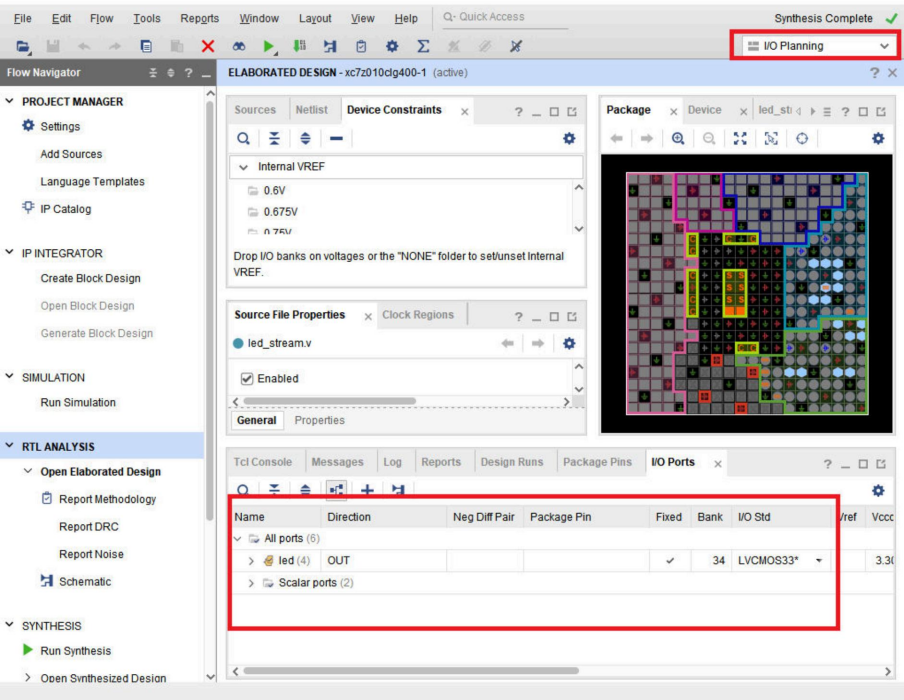

然后右上角,软件运行状态下面的视图选择。我们默认是Default Layout,但是我们要进行IO绑定,我们选择I/OPlanning。

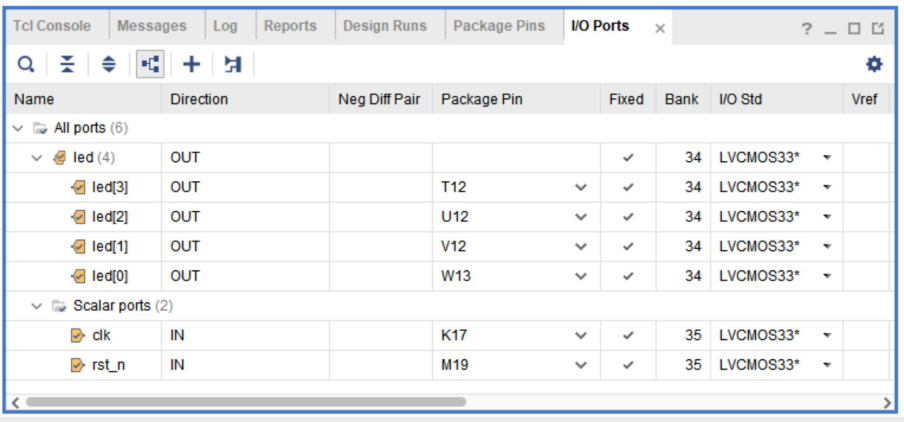

选择I/OPlanning之后出现如下视图,在下面窗口部分,I/OPorts即可进行IO管脚绑定。根据原理图绑定的管脚如下所示,LED和时钟,按钮复位信号均为3.3V电平标准,LVCMOS33,关于引脚,大家可以查阅原理图和硬件手册,下图:复位使用我们板子的KEY3(FPGA_KEY2),引脚绑定如下图:

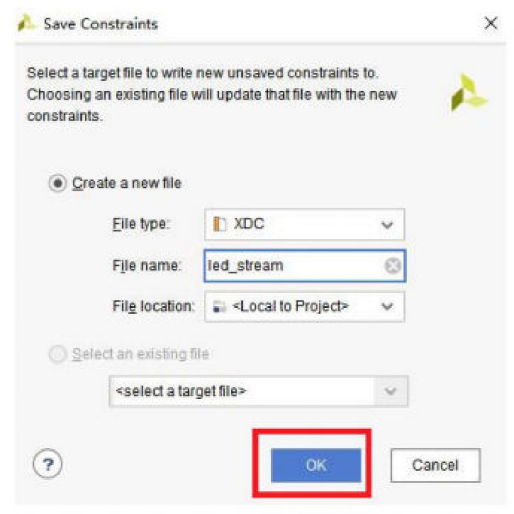

按下ctrl+s保存,弹出的保存对话框,填入管脚约束文件名。我们这里取为led_stream:

五、生成BIT文件

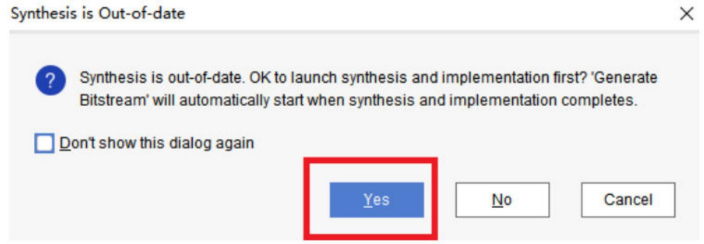

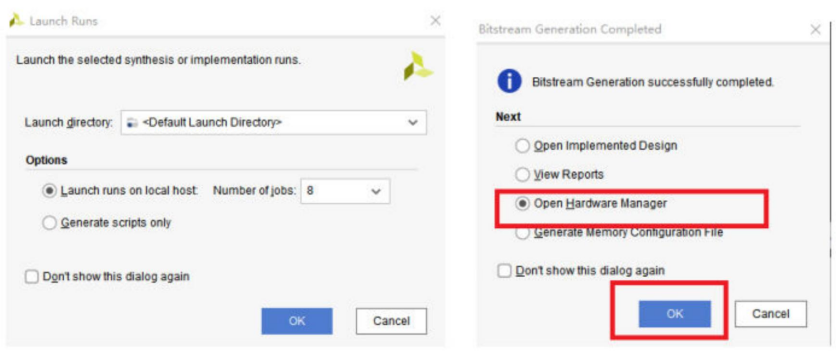

我们点击工程管理栏的PROGRAM AND DEBUG下面的Generate Bitestream生成BIT文件。(也可以先点击IMPLEMENTATION下面的Run implementation先进行实现,实现包括布局布线,这里直接省车bit文件包含了实现操作)。弹出的对话框为综合信息过期。这里默认点击OK(由于软件综合后才能有模块的顶层引脚信息,才能进行绑定管脚。我们绑定管脚之后,软件认为工程信息发生了变更所以需要再次综合)。

接着还会弹出综合线程数量对话框。我们也选择默认(这里使用的电脑最大是8),然后点击OK。然后软件开始了生成比特流的一系列工作。总流程是:综合->实现(布局布线)->生成bit文件。

我们等待软件运行这些操作结束,结束后弹出如下对话框,这里我们选择打开硬件管理器Open Hardware Mnager:

六、下载验证

上一节步骤,弹出的硬件管理界面,这个时候可以插上我们的ZYNQ开发板的下载器USB接口(TYPE-C的JTAG口),开发板上电。

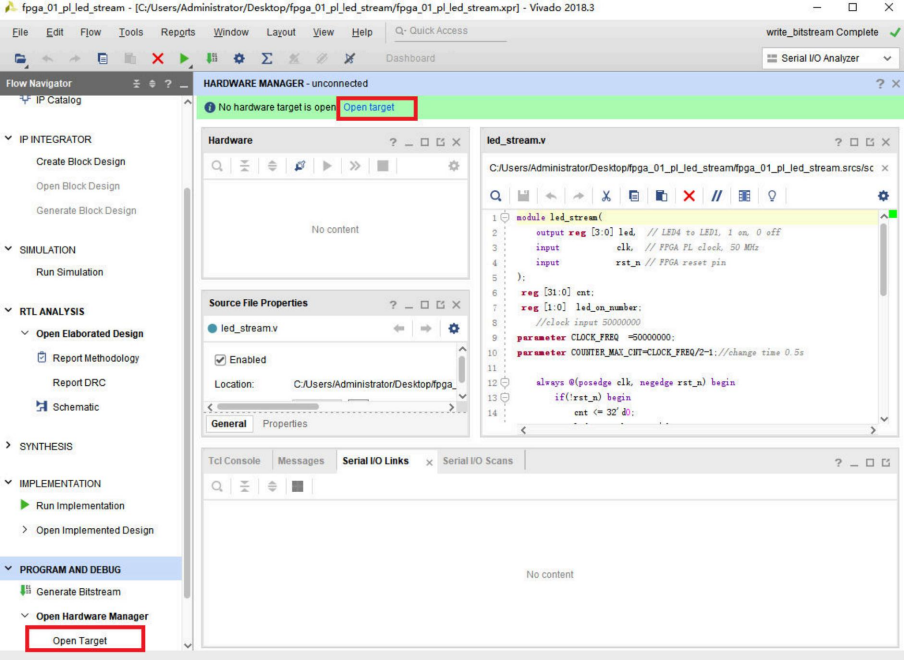

我们打开VIVADO硬件管理的方式也可以从左下角Open hardware manager打开。我们点击上方Opentarget:

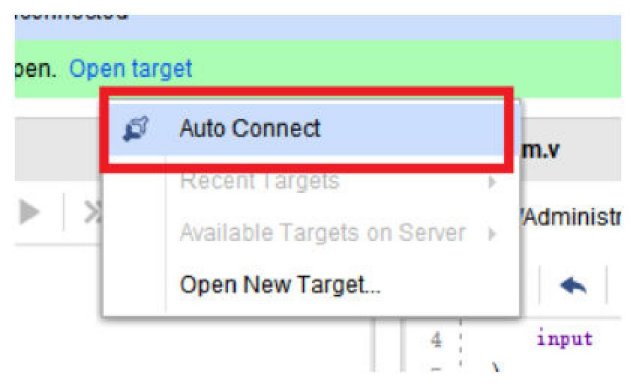

弹出的下拉界面选择点击Auto target,自动连接目标开发板。点击之后待连接完成。

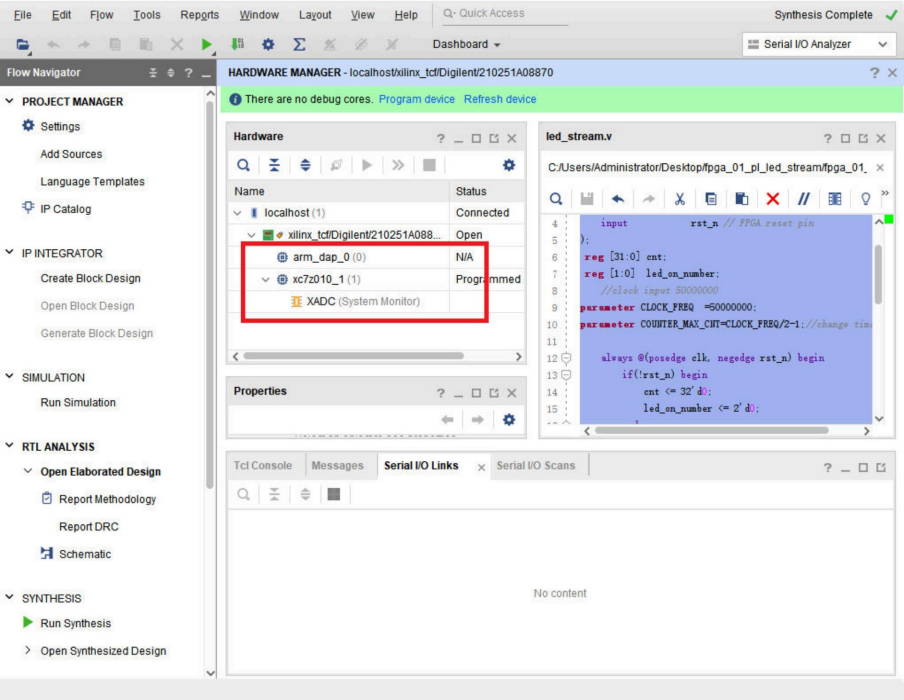

连接完成之后,可以看到Hardware窗口出现了两个设备,一个是arm的dap,一个是xc7z20芯片。上方我们点击Program Device进行烧写配置(断电就丢失。需要下载到FLASH的方法成我们在后面专门的教程继续详细介绍步骤),除了点击上Program device,还可以选中xc7z020右键选择program来烧写BIT:

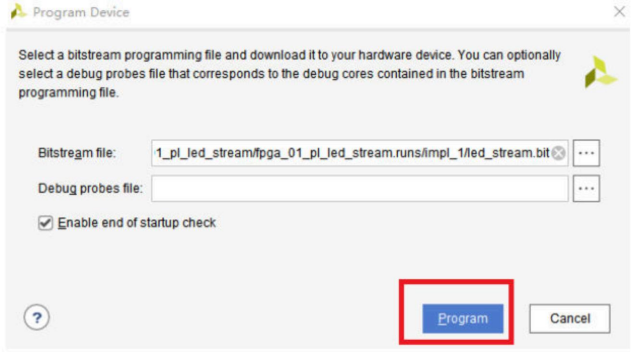

弹出的烧写对话框,默认都不改动,其中Bitstream file表示选择的bit文件,也就是上面我们生成的bit文件。点击program:

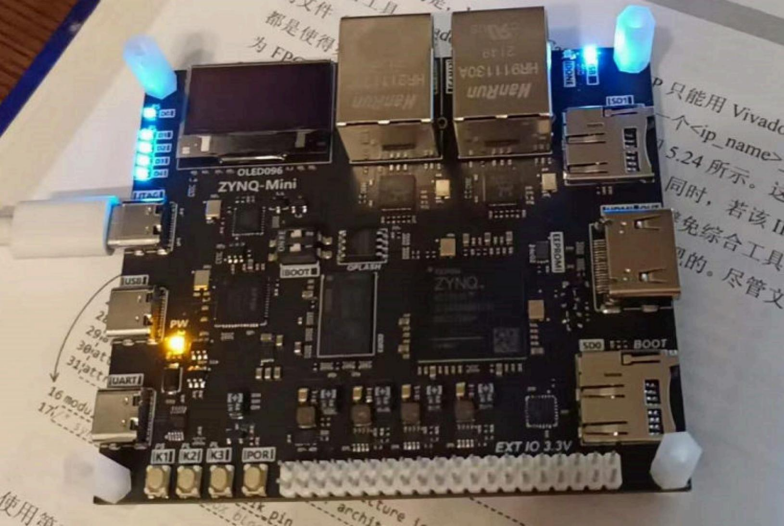

烧写完成。我们可以看到四个PL的LED以0.5秒周期流动亮起。本节教程结束。

未来

二牛学FPGA

用户_15388

用户_15381