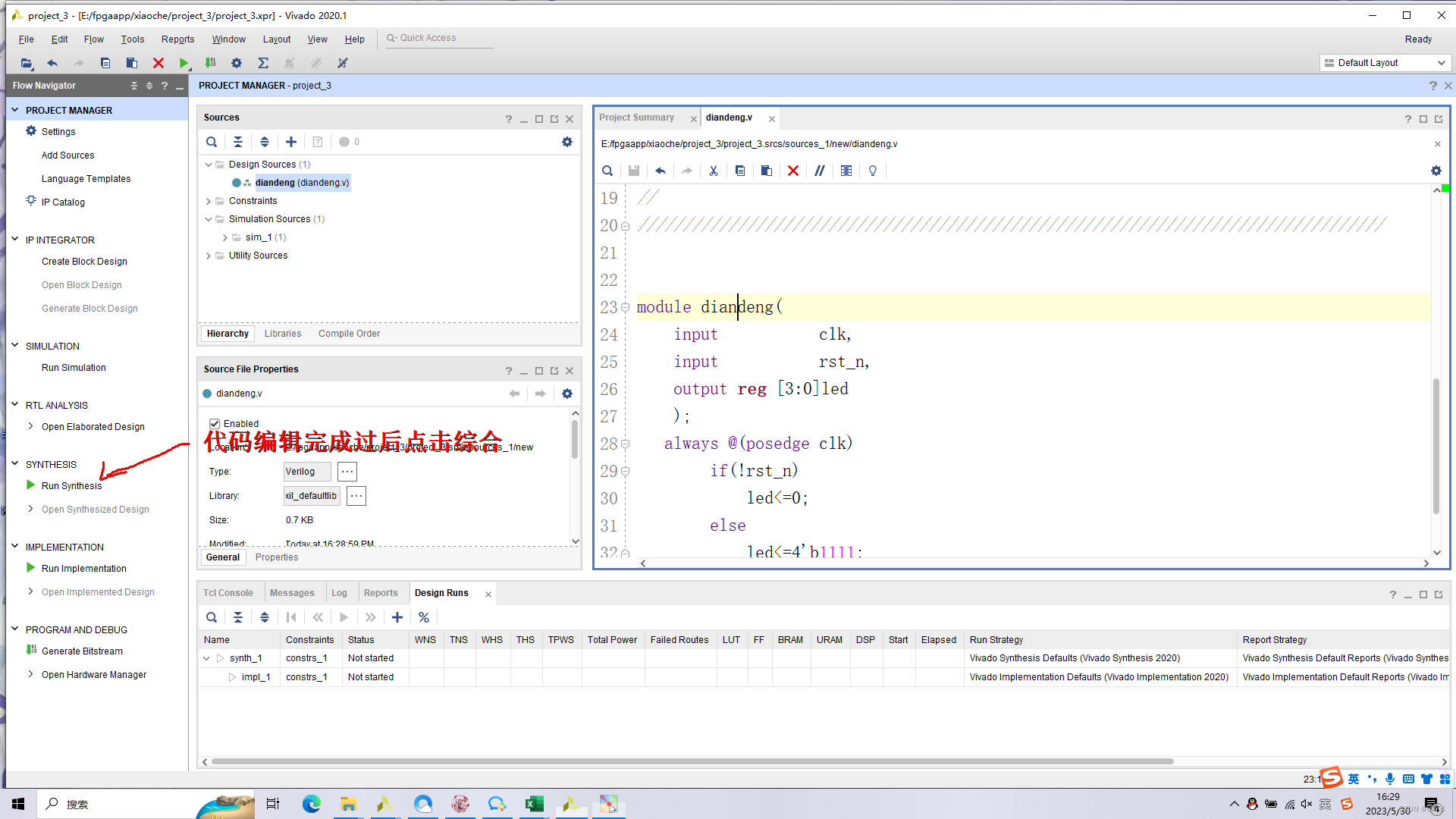

这是一个简单的Verilog点灯模块,声明了一个时钟信号clk、一个复位信号rst_n和一个4位的输出寄存器led。

在always @(posedge clk)块中,使用了一个条件语句。如果复位信号rst_n为低电平(即复位有效),则将led寄存器的值设为0。否则,每当时钟上升沿到来时,将led寄存器的值设为4'b1111(二进制表示)。

module sy1(

input clk,

input rst_n,

output reg[3:0]led

);

always @(posedge clk)

if(!rst_n)

led<=0;

else

led<=4'b1111;

endmodule简而言之,这个模块是一个简单的寄存器,当复位信号为低电平时将led寄存器清零,否则在每个时钟上升沿将其设为15(二进制表示)。

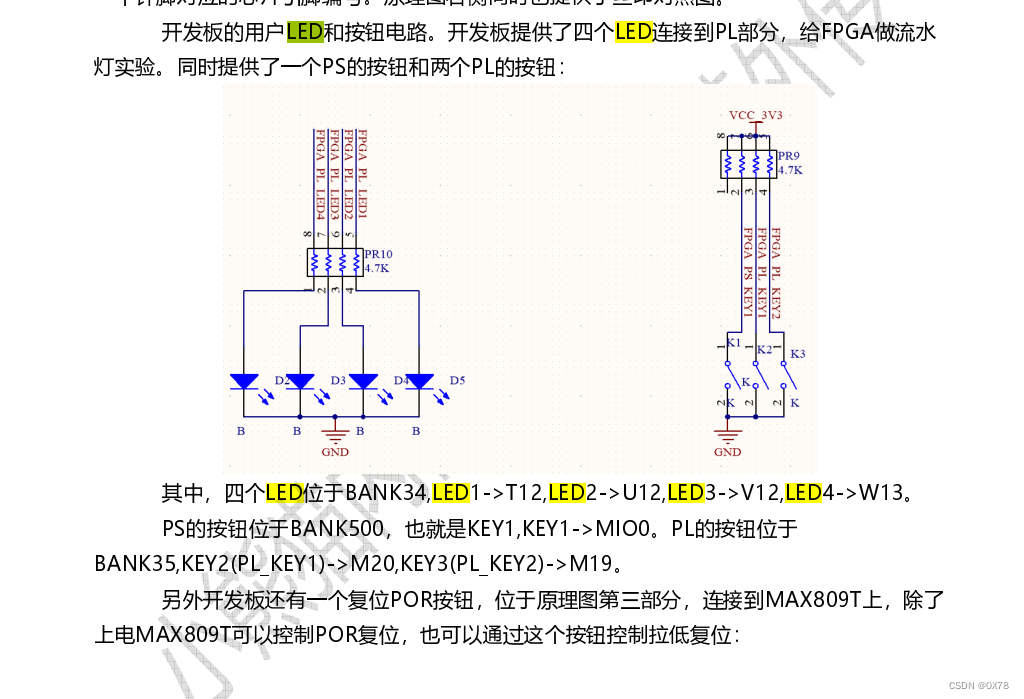

而我们的led则对应ZYNQ ECO开发板上四个led灯,led<=1111,及四个高电平;

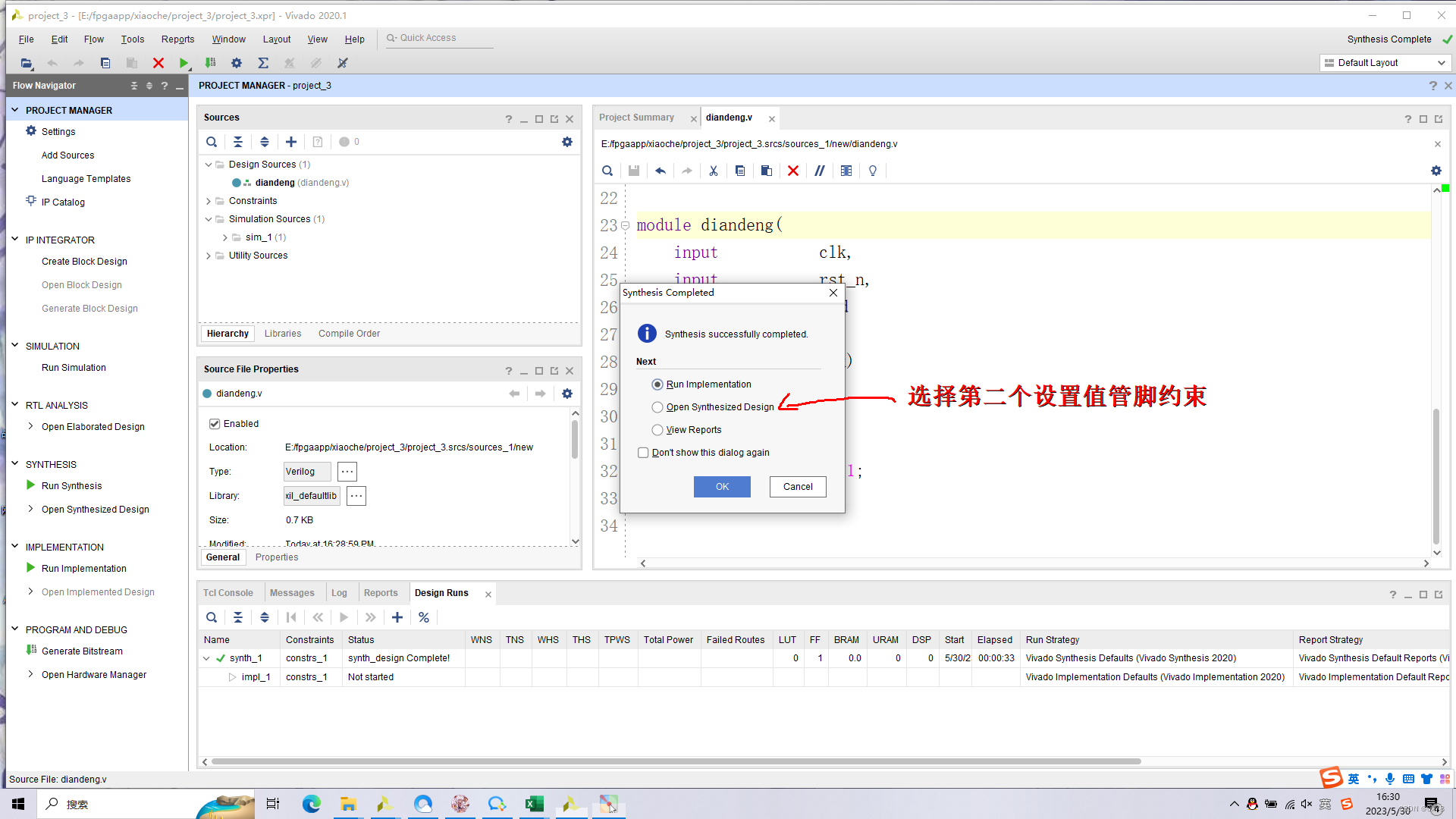

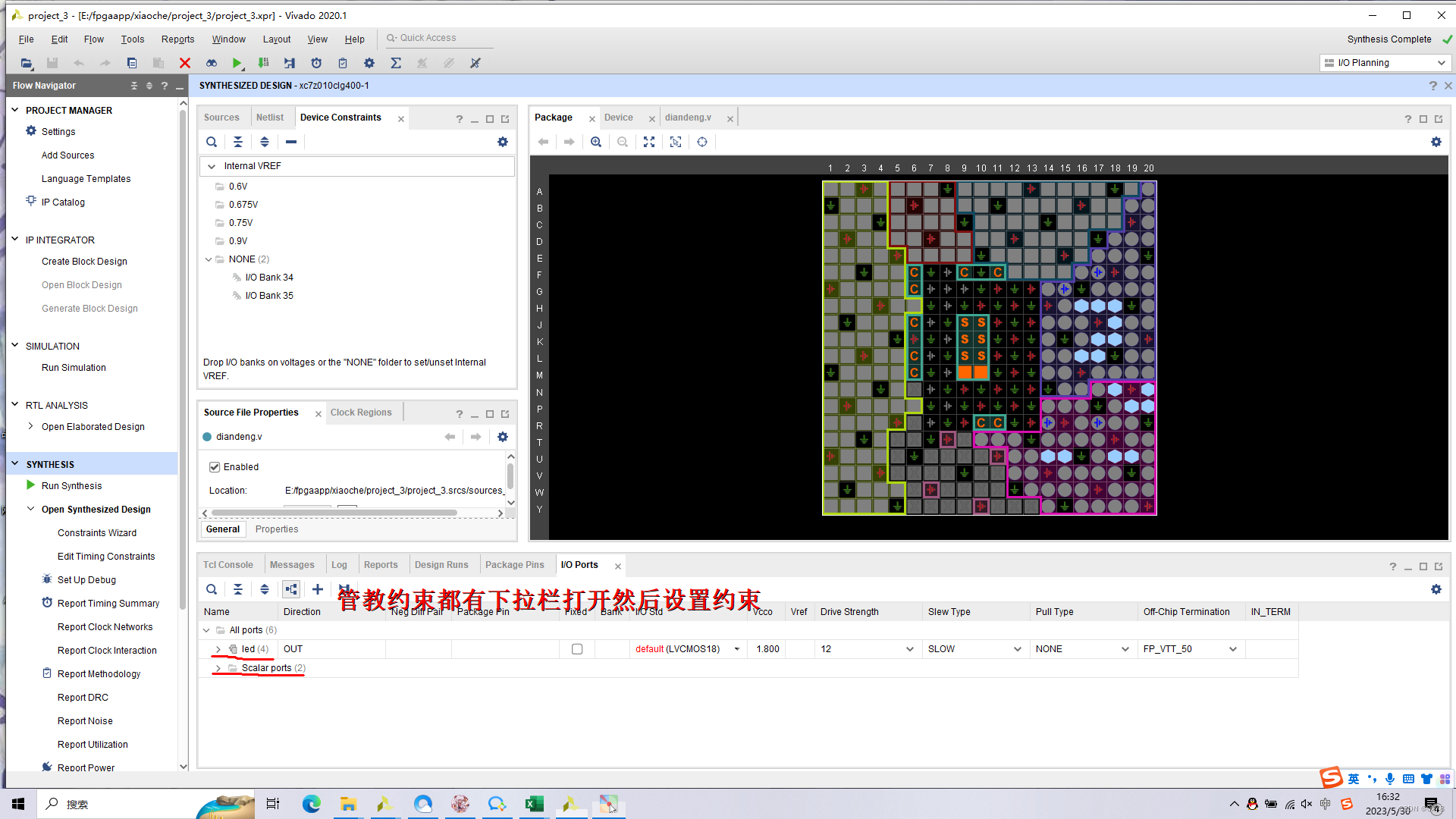

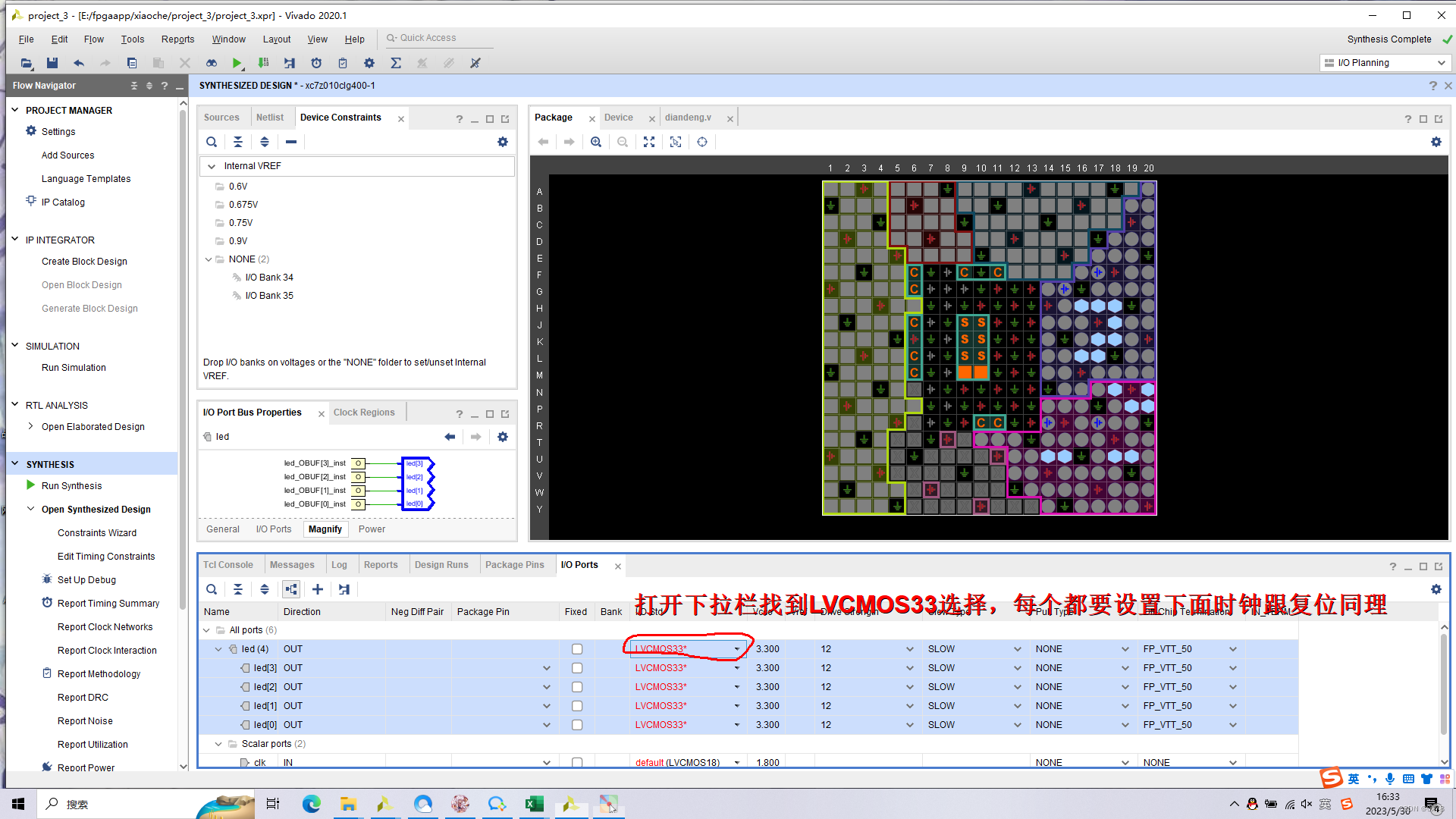

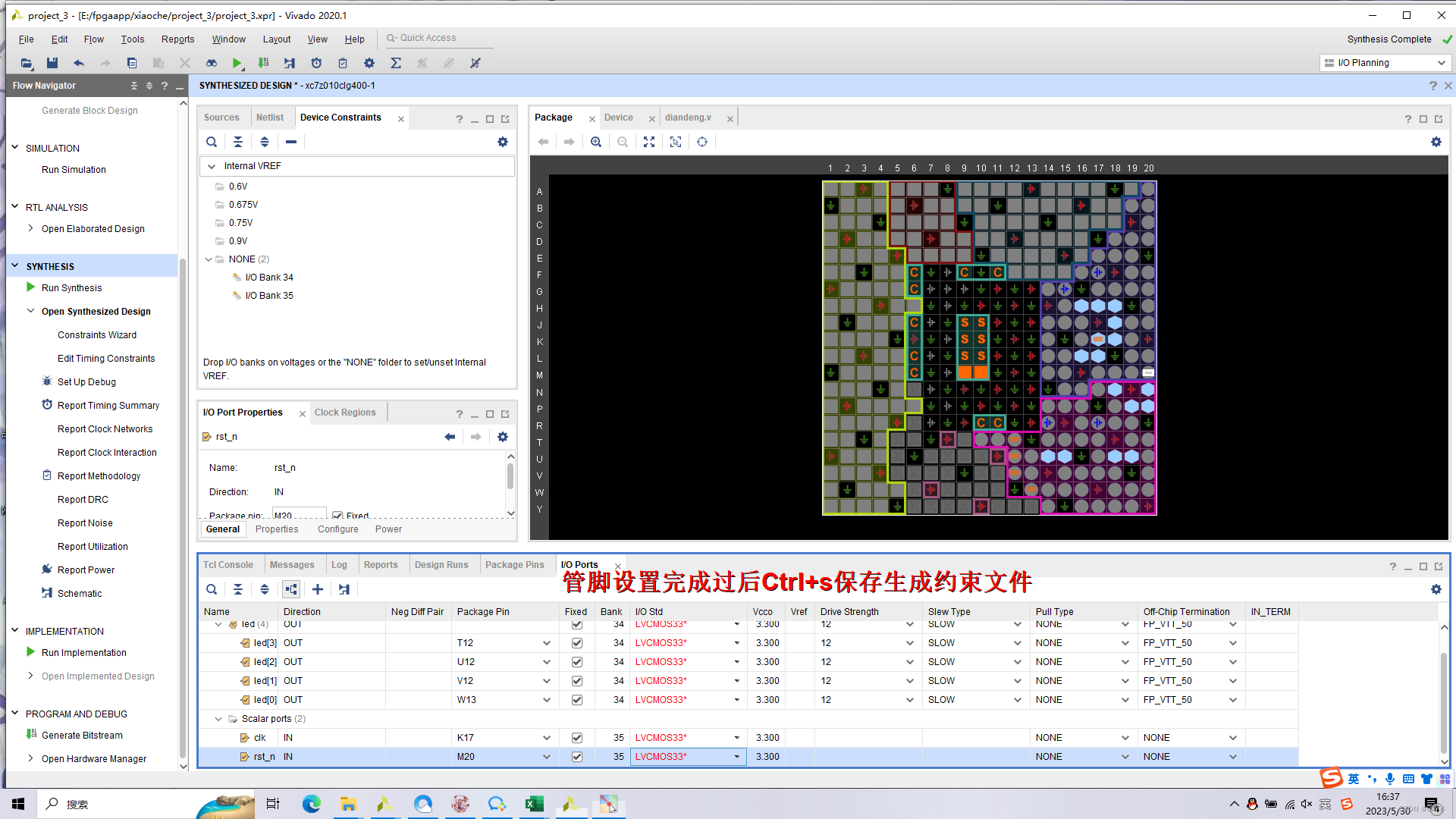

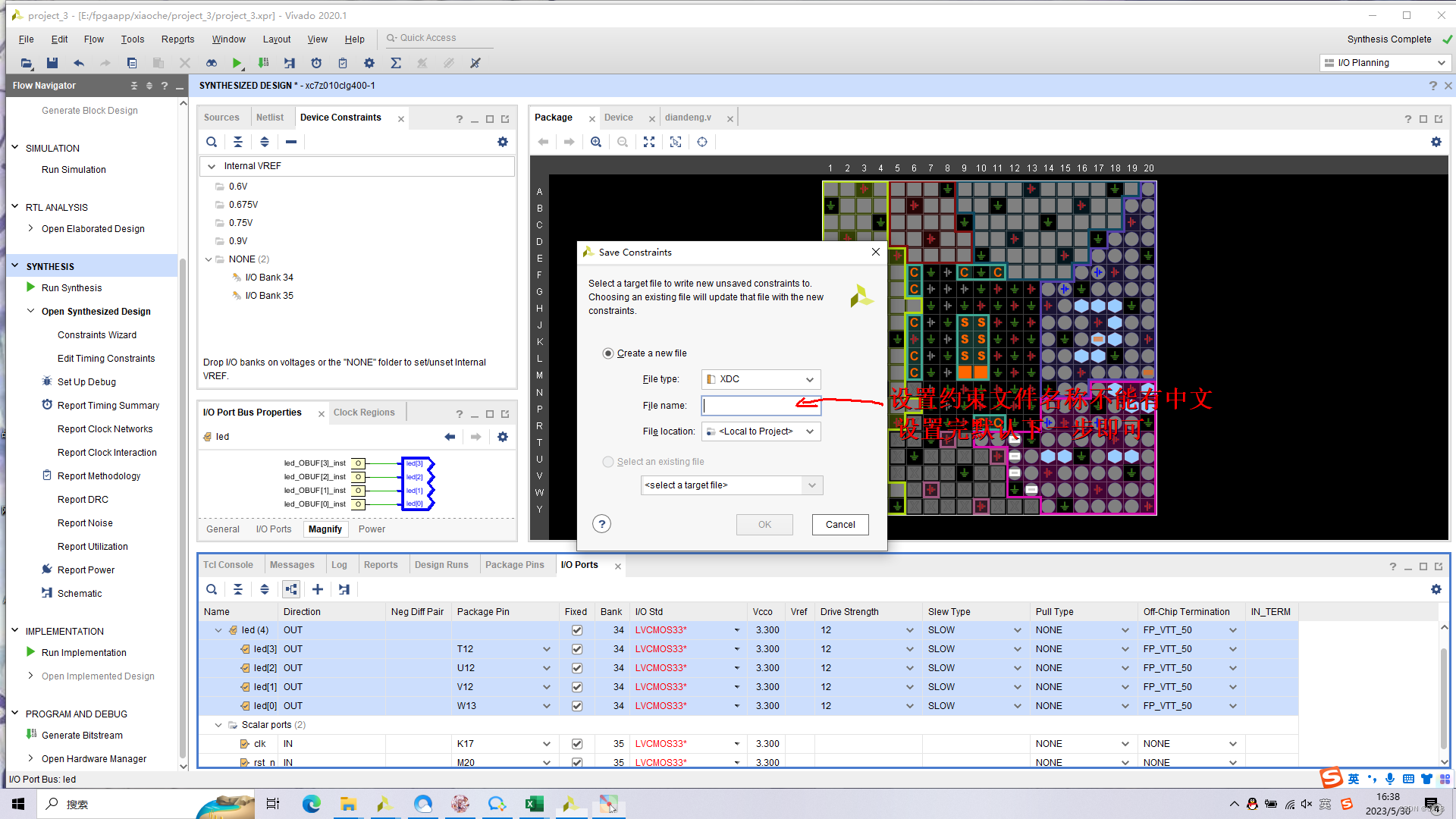

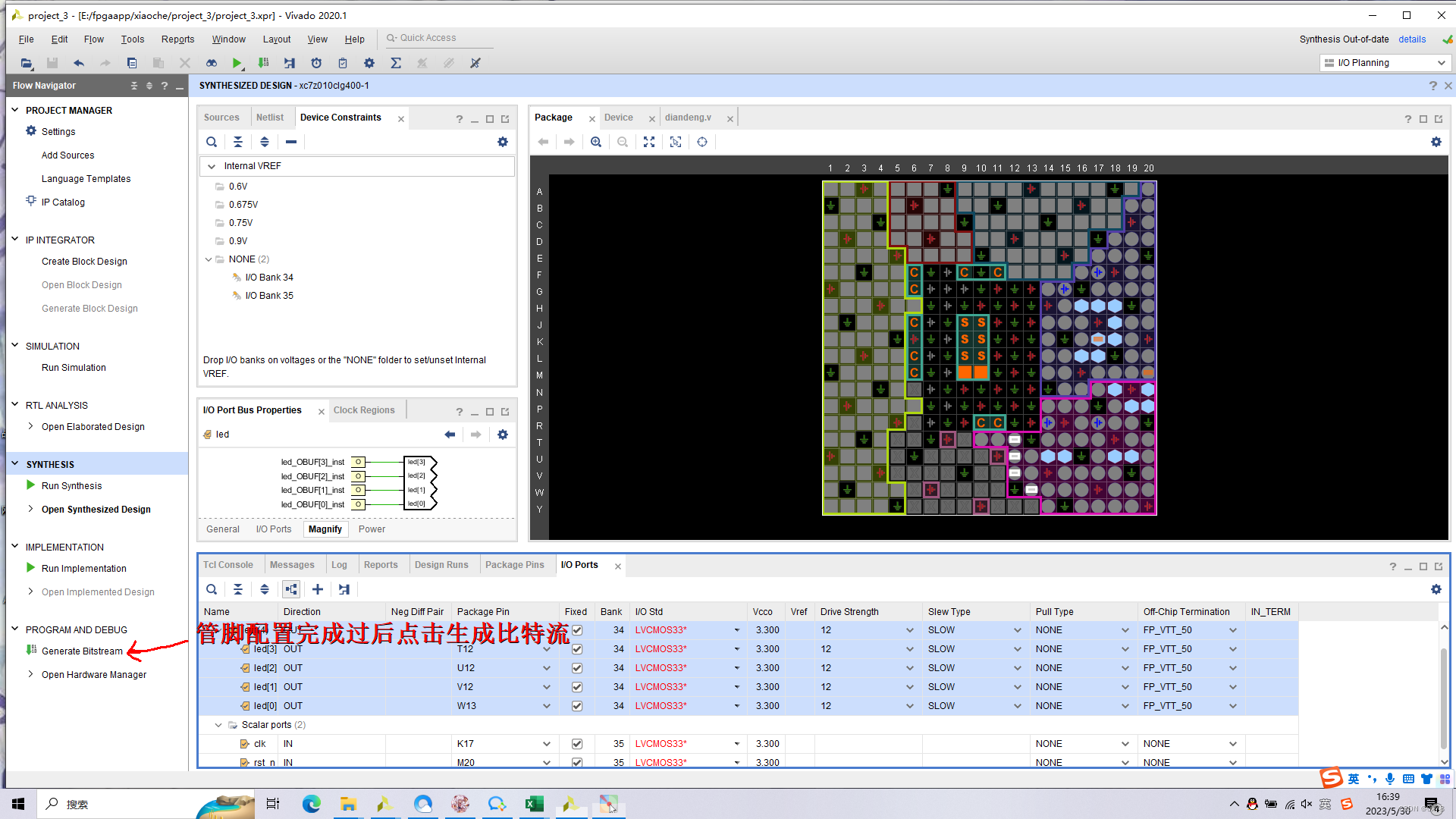

下面将led于相应引脚绑定

我们查看ZYNQ ECO 硬件说明书 可得到对应引脚

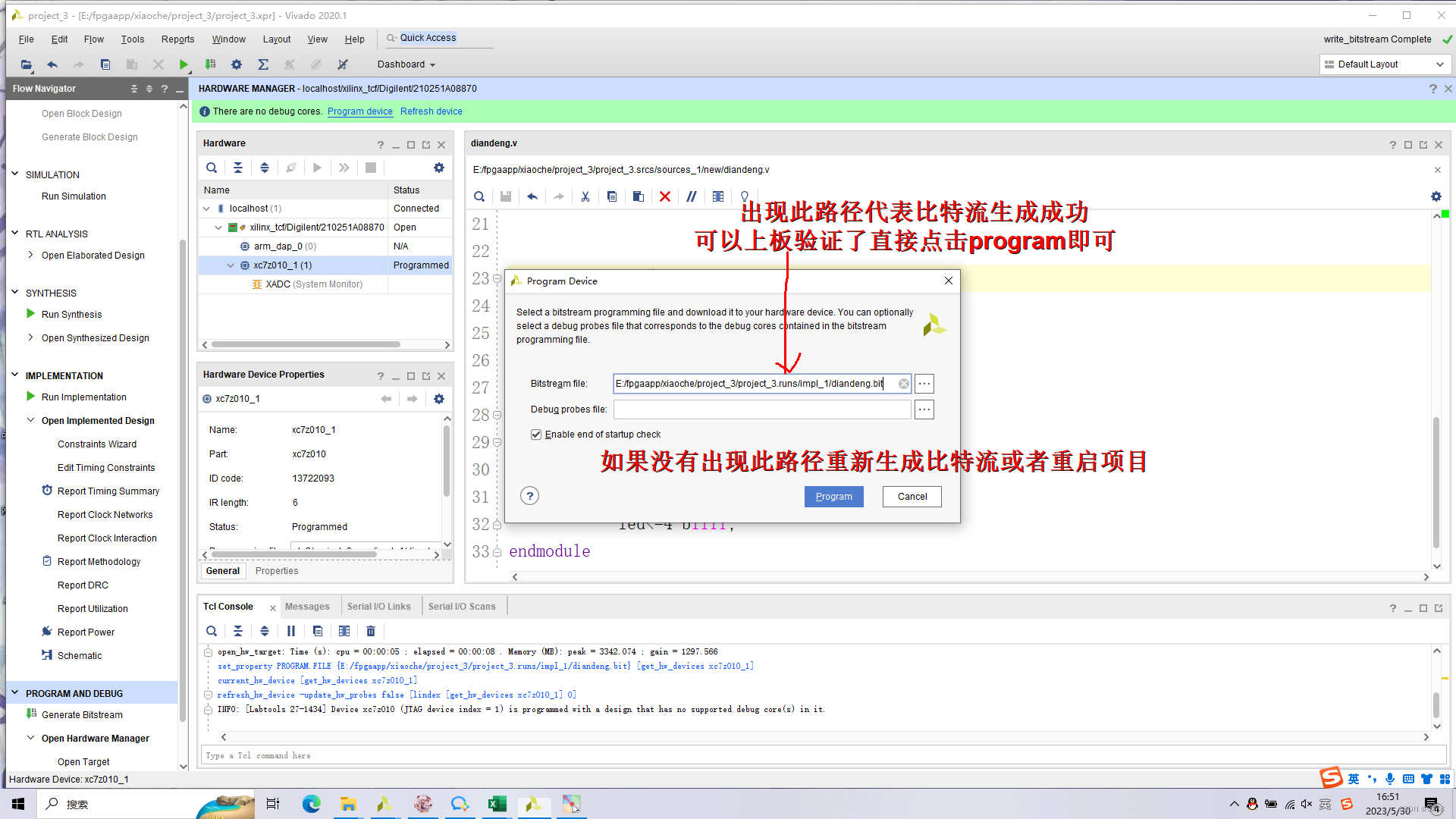

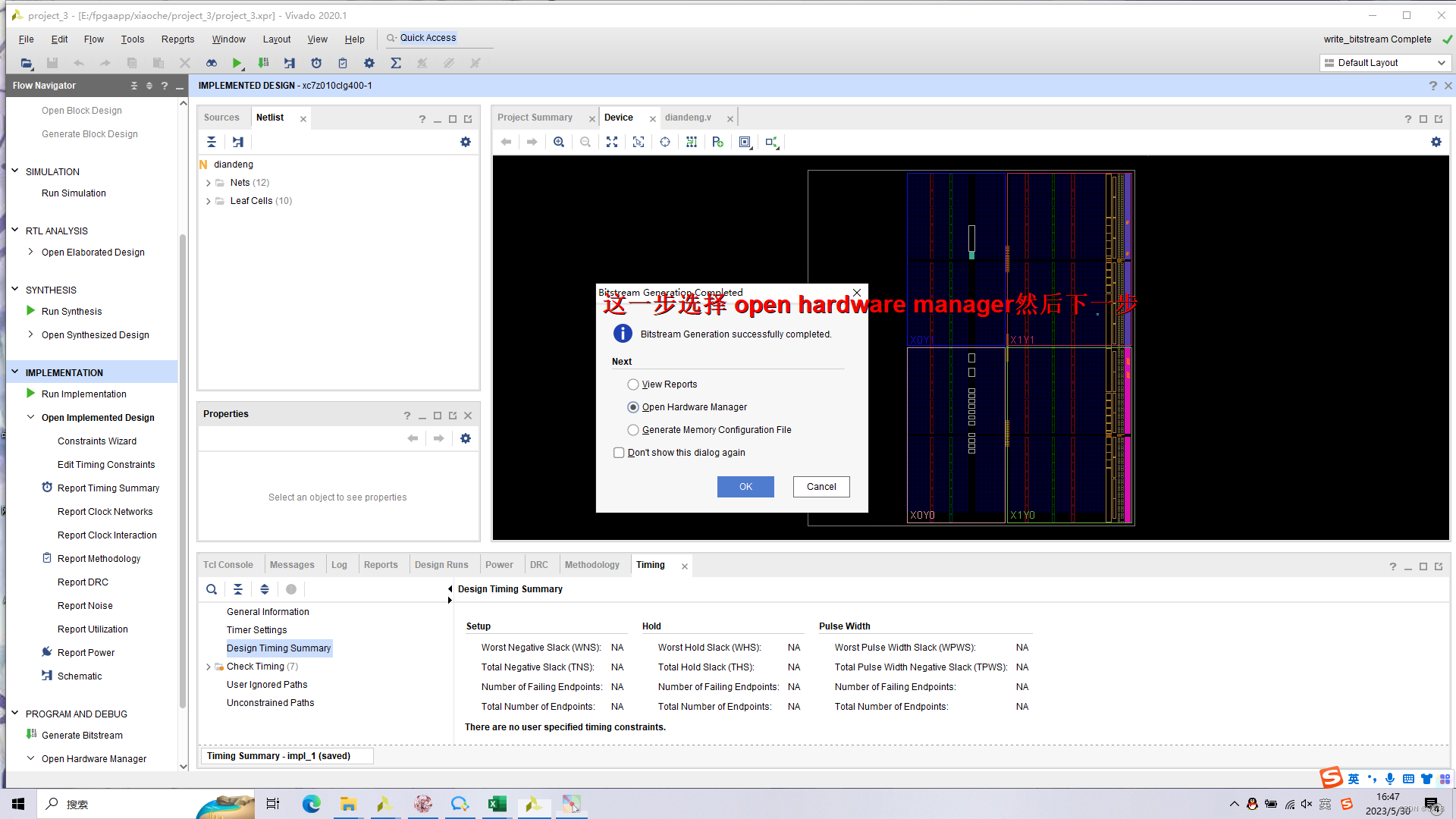

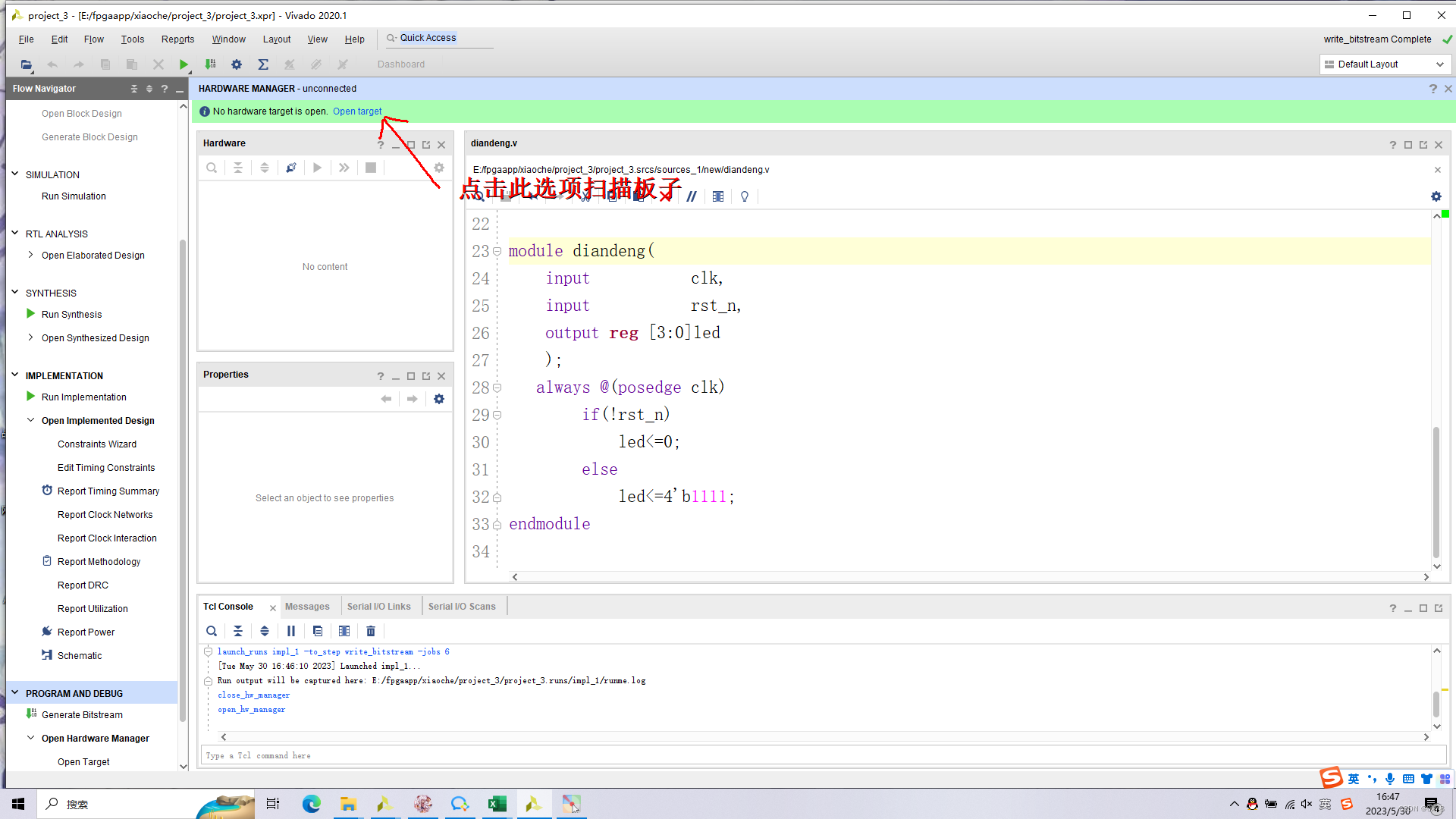

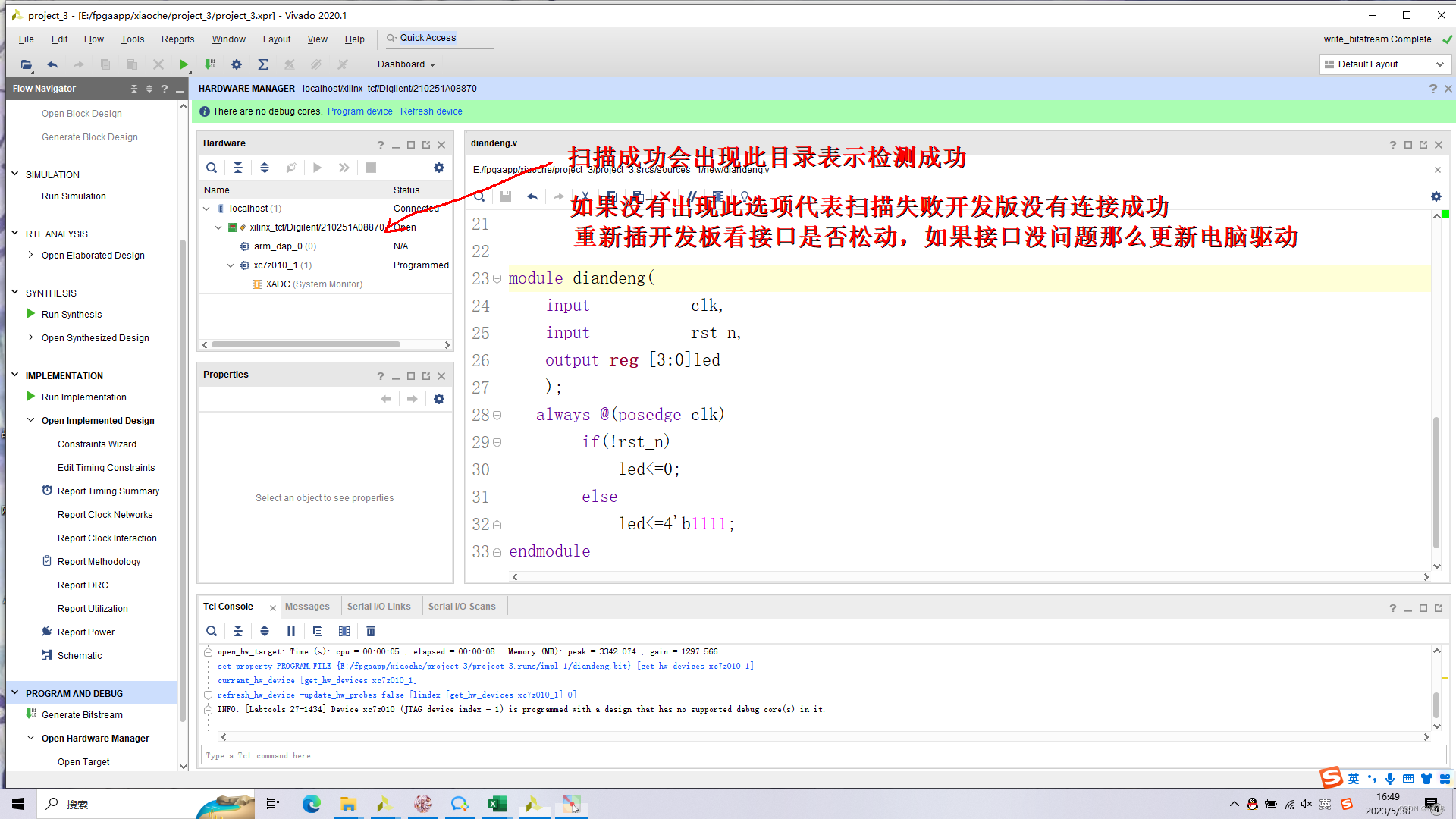

至此就可实现点灯。