误区一:盲目敲代码,却对FPGA底层架构视而不见

症状表现:

- 认为FPGA编程等同于软件编程,仅关注Verilog语法而忽视硬件实现逻辑

- 无法解释LUT(查找表)如何替代传统门电路,更不懂布线资源与时钟域管理

- 开发中频繁遭遇时序违例、资源利用率爆炸等问题却无从下手

本质剖析:

FPGA的"可编程"本质是硬件重构而非软件执行。

- LUT魔方:每个4/6输入LUT本质是SRAM存储的真值表,通过烧写16/64位二进制数实现任意组合逻辑

- 布线迷宫:可编程互联资源占芯片面积60%以上,糟糕的代码会导致布线拥塞(如过度使用全局信号)

- 时钟血脉:理解全局/区域时钟网络、MMCM/PLL配置是避免亚稳态的关键

破局之道:

- 手绘FPGA架构图:标注LUT/FF/DSP/RAM位置,理解跨时钟域路径

- 使用ChipScope逐周期抓取信号,观察RTL代码如何映射到物理资源

- 精读《FPGA架构白皮书》(如Xilinx 7系列CLB详解)

误区二:把HDL当C语言,陷入"伪硬件思维"陷阱

经典谬误:

- 试图用for循环实现并行计算(实际综合出超长组合逻辑链)

- 在always块内混合使用阻塞/非阻塞赋值导致仿真与实现结果背离

- 迷信"代码简洁"而忽视硬件代价(如用除法运算符消耗上百个DSP)

硬件思维觉醒指南:

✅ 模块化映射:

// 软件思维:按执行顺序编写

always @(*) begin

c = a + b;

d = c * 2;

end

// 硬件思维:显式构建数据通路

assign c = a + b; // 加法器模块

assign d = c << 1; // 移位器模块✅ 时空转换艺术:

- 面积换速度:流水线拆解长组合逻辑(如32位乘法拆为4级流水)

- 速度换面积:时分复用逻辑单元(需配合状态机控制)

实战训练:

- 用Vivado Schematic Viewer反推代码生成的电路结构

- 对比同一算法的行为级描述与RTL级描述的资源消耗(如FFT实现)

误区三:闭门造车,忽视系统级战场

血泪教训:

- 能实现千兆以太网MAC层,却因未考虑PCB阻抗匹配导致误码率超标

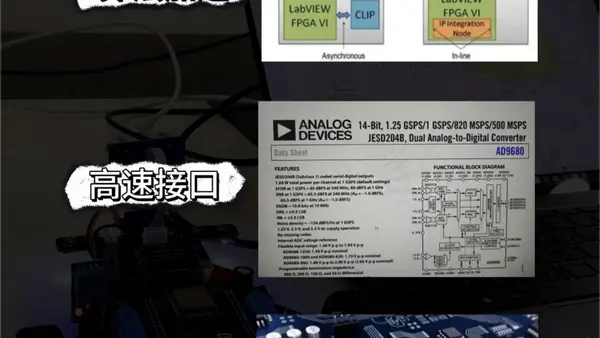

- 完成AD采集逻辑设计,却因未配置好JESD204B接口协议无法连接高速ADC

- 开发图像处理IP核,但因不熟悉AXI-Stream流控协议无法集成到Vitis平台

FPGA工程师的三大战场:

| 战场维度 | 必备技能 | 致命雷区 |

|---|---|---|

| 板级设计 | 高速PCB设计、电源树规划、散热仿真 | 未做信号完整性分析导致DDR4不稳定 |

| 协议栈 | PCIe Gen4/USB 3.0/JESD204C | 误用8b/10b编码导致光模块失锁 |

| 系统集成 | Zynq MPSoC软硬协同、HLS加速器优化 | 未隔离PS/PL电源域引发芯片烧毁 |

破圈策略:

- 拆解大厂开发板(如KCU105):学习PCIe金手指布线、电源滤波电路设计

- 使用IBERT工具进行眼图测试,直观观察高速串行信号质量

- 参与ORAN联盟项目,实战5G前传eCPRI接口开发

误区四:数字逻辑根基不牢,空中楼阁终将崩塌

基础薄弱典型症状:

- 分不清同步复位与异步复位的时序影响(导致Recovery Time违规)

- 不理解FSM安全编码准则(遭遇单粒子翻转导致状态机跑飞)

- 对时钟偏斜(Skew)/时钟抖动(Jitter)的量化影响毫无概念

数字逻辑四大神功:

- 卡诺图炼金术:化简复杂组合逻辑(如7段数码管译码器)

- 状态机心法:

- 时序分析奥义:

- 功耗管控秘技:

重生计划:

- 重做《数字电路设计300题》(重点训练竞争冒险分析)

- 用Tcl脚本自动化生成时钟约束(create_clock -period 5 [get_ports clk])

- 在Artix-7上复刻经典CPU架构(如RISC-V五级流水线)

金牌培训师终极建议

- 硬件认知革命:

每周解剖一个Xilinx官方IP核(如Aurora 64b/66b),学习其参数化设计思想 - 工具链掌控:

掌握Vivado Tcl命令集,实现从综合到比特流的全流程自动化 - 生态突围:

加入Xilinx Adaptive Compute Clusters(ACCs),获取最新Versal系列开发资源 - 跨界融合:

学习Python+Cocotb搭建验证框架,用机器学习优化FPGA布局布线

警示:FPGA不是终点,而是打开异构计算世界的钥匙。拒绝做"逻辑搬运工",要成为硬件架构设计师!