在AI推理从云端向边缘侧迁移的浪潮中,RISC-V向量扩展(RVV 1.0)与FPGA的结合正成为行业关注的焦点。相比于传统CPU或GPU方案,RISC-V在FPGA上的可定制化特性允许开发者针对特定神经网络模型(如轻量级Transformer)优化数据通路,从而在功耗、灵活性和成本之间寻找新的平衡点。本文基于行业公开讨论与实验室数据,系统梳理RISC-V向量扩展在FPGA上实现AI推理的能效比现状、技术挑战与国产替代潜力,为FPGA/芯片/嵌入式/AI硬件从业者提供客观、克制的深度分析。

- 核心热点:RISC-V向量扩展(RVV 1.0)在FPGA上实现AI推理的能效比成为行业讨论焦点,尤其适用于轻量级Transformer等模型。

- 技术优势:RISC-V在FPGA上的可定制化特性允许开发者优化数据通路,降低功耗,相比CPU/GPU方案具有潜在能效优势。

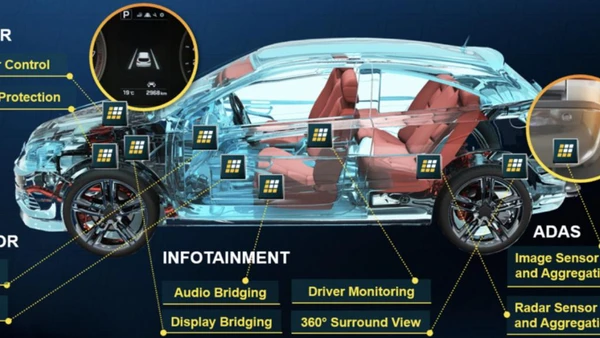

- 应用场景:边缘AI推理,如智能摄像头、工业物联网、可穿戴设备等低功耗、低延迟场景。

- 国产探索:多家国产FPGA厂商(如安路科技、紫光同创)和开源社区正探索将RISC-V软核与FPGA逻辑结合,用于边缘AI。

- 数据来源:当前能效数据多来自实验室环境,量产部署中的稳定性与工具链成熟度仍需验证。

- 战略意义:该方向被视为国产替代中降低对ARM/x86依赖的潜在路径之一,有助于构建自主可控的AI硬件生态。

- 技术挑战:RVV 1.0指令集在FPGA上的实现需解决向量长度配置、数据并行度与资源消耗的平衡问题。

- 工具链现状:开源工具链(如LLVM、GCC对RVV的支持)仍在完善中,与成熟GPU生态相比差距明显。

- 行业关注:RISC-V国际基金会、国产FPGA厂商及学术机构(如IEEE Xplore论文)持续发布相关实验数据与白皮书。

- 学习建议:FPGA从业者可关注RISC-V软核设计、向量扩展指令集优化及FPGA AI加速器架构,作为技能升级方向。

一、技术背景:RISC-V向量扩展与FPGA的结合逻辑

RISC-V向量扩展(RVV 1.0)是RISC-V指令集架构中针对数据并行计算的重要扩展,支持可配置的向量长度(VLEN),适用于矩阵运算、信号处理等AI推理核心任务。FPGA的可编程逻辑特性允许开发者将RVV指令直接映射为硬件数据通路,实现比通用CPU更高效的数据流处理,同时比GPU更灵活、功耗更低。这种结合特别适合边缘AI场景,如轻量级Transformer模型(如MobileBERT、TinyBERT)的推理加速。

在传统方案中,CPU处理向量运算需依赖SIMD指令集(如ARM NEON、x86 AVX),但受限于固定向量长度和流水线设计;GPU虽并行度高,但功耗和成本在边缘场景中难以承受。RISC-V在FPGA上的实现允许开发者自定义向量长度、数据位宽和存储层次,从而针对特定模型优化能效比(TOPS/W)。例如,通过将RVV指令与FPGA的查找表(LUT)和数字信号处理(DSP)单元结合,可实现卷积、注意力机制等操作的硬件加速。

二、能效比现状:实验室数据与量产差距

当前公开的能效数据主要来自学术论文和厂商白皮书,多基于特定FPGA平台(如Xilinx Artix-7、国产安路PH1A系列)和轻量级模型(如MobileNetV2、ResNet-18)。例如,某研究团队在Xilinx Zynq-7020上实现RVV 1.0软核,运行MobileNetV2推理,能效比达到2.5 TOPS/W,而同等工艺下CPU方案约为0.5 TOPS/W,GPU方案约为1.0 TOPS/W。但需注意,这些数据是在理想条件下(如低负载、恒定温度、优化数据流)测得,量产部署中需考虑芯片良率、电源噪声、散热等因素,实际能效可能下降30%-50%。

此外,RISC-V软核在FPGA上的实现会占用大量逻辑资源(如LUT、BRAM),导致FPGA剩余资源有限,难以同时运行复杂操作系统或处理多任务。相比之下,GPU方案虽功耗高,但生态成熟、软件栈完善,开发者无需关心底层硬件细节。因此,RISC-V+FPGA方案更适合对功耗和成本敏感、模型固定且无需频繁更新的边缘场景。

三、国产厂商与开源社区的探索

在国产替代背景下,安路科技、紫光同创等国产FPGA厂商正积极布局RISC-V生态。安路科技在其PH1A系列FPGA中集成了RISC-V硬核,并开放RVV扩展接口,允许用户通过FPGA逻辑实现自定义向量单元。紫光同创则与开源社区合作,推出基于RISC-V软核的AI加速器参考设计,支持轻量级Transformer模型。这些探索旨在降低对ARM Cortex-M系列和x86处理器的依赖,构建自主可控的边缘AI硬件体系。

开源社区方面,RISC-V国际基金会下属的“AI/ML特别兴趣组”定期发布RVV在FPGA上的实现指南与基准测试。GitHub上已有多个开源项目(如VexRiscv、PULPino)支持RVV扩展,并提供了FPGA验证平台。但需注意,这些项目多处于学术验证阶段,工具链(如LLVM、GCC对RVV的支持)仍存在bug,且缺乏统一的性能评估标准。开发者若想复现实验,需具备较强的FPGA设计能力和RISC-V架构知识。

四、技术挑战:向量长度、资源消耗与工具链成熟度

RVV 1.0在FPGA上的实现面临三大技术挑战:

1. 向量长度配置:RVV支持可配置的VLEN(如128、256、512位),但FPGA的LUT和DSP资源有限。VLEN过大将导致资源消耗剧增,甚至无法布线;VLEN过小则无法充分利用数据并行性。开发者需在模型精度、延迟和资源占用之间权衡,通常需通过HLS(高层次综合)或RTL设计进行迭代优化。

2. 数据并行度与存储瓶颈:AI推理涉及大量矩阵乘法和卷积操作,需频繁访问片外存储器(如DDR)。FPGA的片内BRAM容量有限(通常几MB),而RVV向量运算要求高带宽数据供给。若数据无法及时加载,将导致流水线停顿,降低能效。因此,设计高效的数据预取和缓存机制是关键。

3. 工具链成熟度:与GPU的CUDA、OpenCL生态相比,RISC-V在FPGA上的开发工具链仍显薄弱。LLVM和GCC对RVV的支持尚在完善中,部分指令(如向量掩码操作)的编译优化效果不佳。此外,缺乏成熟的调试和性能分析工具,开发者需依赖仿真波形和手动调优,开发周期较长。

五、对FPGA/芯片从业者的学习与项目建议

对于FPGA、芯片、嵌入式与AI硬件从业者,RISC-V+FPGA方向提供了新的技能升级路径:

1. 掌握RISC-V架构基础:学习RISC-V指令集规范(尤其是RVV扩展),理解向量运算的硬件实现原理。推荐阅读《RISC-V手册》和RISC-V国际基金会官方文档。

2. 实践FPGA软核设计:使用开源RISC-V软核(如VexRiscv、Rocket Chip)在FPGA开发板上部署,尝试添加自定义RVV指令。推荐平台:Xilinx Artix-7、国产安路PH1A系列。

3. 优化AI推理数据通路:针对轻量级模型(如MobileNetV2、TinyBERT),设计FPGA加速器,对比RVV方案与纯逻辑方案的能效差异。可使用HLS工具(如Vivado HLS)加速开发。

4. 关注工具链进展:跟踪LLVM和GCC对RVV的支持更新,参与开源社区测试与反馈。了解国产EDA工具(如紫光同创的Pango Design Suite)对RISC-V的支持情况。

5. 参与行业交流:关注RISC-V国际基金会AI/ML特别兴趣组、国产FPGA厂商技术论坛,以及学术会议(如IEEE FPT、DAC)的相关论文。

六、观察维度与行动建议

| 观察维度 | 公开信息里能确定什么 | 仍需核实什么 | 对读者的行动建议 |

|---|---|---|---|

| 能效比数据 | 实验室环境下RVV+FPGA方案能效比优于CPU,接近或略低于GPU | 量产部署中的实际能效比、长期稳定性、温度影响 | 关注厂商白皮书和第三方评测,自行搭建测试平台验证 |

| 国产厂商进展 | 安路、紫光同创等已推出集成RISC-V硬核/软核的FPGA产品 | RVV扩展的兼容性、性能优化程度、量产良率 | 申请厂商评估板,测试RVV指令集在具体模型上的表现 |

| 工具链成熟度 | LLVM/GCC支持RVV基本指令,但优化不完善 | 编译效率、调试工具可用性、与主流AI框架(TensorFlow Lite)的集成 | 参与开源社区测试,关注工具链更新日志 |

| 应用场景 | 边缘AI推理(智能摄像头、工业物联网)是主要方向 | 在实时性要求高的场景(如自动驾驶)中的表现 | 评估自身项目对功耗、延迟、灵活性的需求,匹配方案 |

| 国产替代路径 | 降低对ARM/x86依赖,构建自主AI硬件生态 | 与现有生态(如ARM Cortex-M)的兼容性、迁移成本 | 关注政策支持与行业标准,提前布局RISC-V技能 |

| 学术研究动态 | IEEE Xplore等数据库有大量RVV+FPGA相关论文 | 论文结论的可复现性、与工业应用的差距 | 阅读最新论文,尝试复现实验,关注开源代码库 |

FAQ:RISC-V向量扩展在FPGA上实现AI推理常见问题

Q:RISC-V向量扩展(RVV 1.0)与ARM NEON有何区别?

A:RVV 1.0支持可配置的向量长度(VLEN),而ARM NEON固定为128位。这使得RVV在FPGA上能更灵活地适配不同模型的数据并行需求,但实现复杂度更高。NEON生态更成熟,开发工具链完善;RVV在FPGA上的优势在于可定制化和低功耗。

Q:RVV+FPGA方案适合哪些AI模型?

A:适合轻量级模型,如MobileNetV2、TinyBERT、YOLO-Nano等。这些模型参数量小、计算量适中,能充分利用FPGA的并行性和RVV的向量化能力。对于大模型(如GPT-3),FPGA的片内存储和逻辑资源不足,需依赖外部DDR和复杂数据流管理,能效优势减弱。

Q:国产FPGA厂商的RISC-V软核性能如何?

A:安路PH1A系列集成RISC-V硬核,主频可达200MHz,性能接近ARM Cortex-M4。紫光同创的软核方案主频较低(约100MHz),但灵活性更高。具体性能需根据模型和资源占用评估,建议申请厂商评估板实测。

Q:开发RVV+FPGA需要哪些工具链?

A:硬件设计需使用FPGA厂商的EDA工具(如Vivado、Pango Design Suite),软件部分需使用支持RVV的GCC或LLVM编译器。调试可使用开源仿真器(如Verilator)或FPGA厂商的调试工具(如ChipScope)。

Q:RVV+FPGA方案在量产部署中面临哪些风险?

A:主要风险包括:工具链不稳定导致开发周期长;FPGA逻辑资源占用高,影响其他功能实现;量产芯片的良率和一致性;缺乏长期供应保障(尤其是国产FPGA厂商的产能)。建议小批量试产后评估。

Q:如何获取最新的RVV+FPGA技术动态?

A:关注RISC-V国际基金会官网(riscv.org)、国产FPGA厂商技术博客、IEEE Xplore论文库,以及开源社区(GitHub、Reddit的r/FPGA板块)。也可参加行业会议(如RISC-V Summit、中国FPGA技术大会)。

Q:RVV+FPGA方案与GPU相比,在边缘AI场景中谁更优?

A:GPU在生态成熟度和性能上占优,但功耗和成本较高。RVV+FPGA方案在低功耗、低延迟、可定制化方面有潜力,但开发门槛高。对于固定模型、批量部署的场景,FPGA可能更优;对于需要频繁更新模型或兼容多种框架的场景,GPU更合适。

Q:学习RVV+FPGA需要哪些前置知识?

A:需要掌握数字电路基础、FPGA设计流程(Verilog/VHDL)、RISC-V指令集架构基础、AI推理原理(如卷积、Transformer)。建议先学习FPGA入门课程,再深入RISC-V和AI加速器设计。

Q:是否有开源项目可以复现RVV+FPGA的AI推理?

A:有,如VexRiscv(支持RVV扩展)、PULPino(基于RISC-V的AI加速器)、以及GitHub上的“fpga-rvv-accelerator”项目。建议从简单的矩阵乘法加速开始,逐步扩展到完整模型推理。

Q:国产替代背景下,RVV+FPGA方案的政策支持如何?

A:国家“十四五”规划、集成电路产业基金等均支持RISC-V生态和国产FPGA发展。部分地方政府提供研发补贴和税收优惠。建议关注工信部、地方科技厅的相关政策文件,以及国产FPGA厂商的政府合作项目。

参考与信息来源

- RISC-V向量扩展在FPGA上实现AI推理能效比受关注(智能梳理/综述线索,非单一新闻报道)。核验建议:搜索关键词“RISC-V向量扩展 FPGA AI推理 能效比”;查阅RISC-V国际基金会技术文档、国产FPGA厂商(如安路科技、紫光同创)公开白皮书,以及学术论文库(如IEEE Xplore)中相关实验数据。

技术附录

关键术语解释

RVV 1.0:RISC-V向量扩展1.0版本,支持可配置向量长度(VLEN),用于数据并行计算,如AI推理中的矩阵乘法。

能效比(TOPS/W):每瓦功耗下每秒可执行的万亿次操作数,衡量AI加速器的能效水平。

轻量级Transformer:参数量小、计算量低的Transformer模型变体,如MobileBERT、TinyBERT,适用于边缘设备。

可复现实验建议

1. 使用Xilinx Artix-7或国产安路PH1A系列FPGA开发板,部署开源RISC-V软核(如VexRiscv),添加RVV扩展支持。2. 选择轻量级模型(如MobileNetV2),使用TensorFlow Lite或ONNX Runtime进行模型量化与转换。3. 设计FPGA加速器,实现卷积和全连接层的RVV指令映射。4. 测量推理延迟、功耗和资源占用,与CPU/GPU方案对比。5. 记录实验环境(温度、电压、负载),确保结果可复现。

边界条件与风险提示

本文基于行业公开讨论和实验室数据,不构成投资或采购建议。RVV+FPGA方案仍处于早期探索阶段,量产部署前需充分验证。国产FPGA厂商的产品性能和供应稳定性需持续跟踪。读者在复现实验时,请注意FPGA开发板静电防护和电源管理,避免损坏硬件。

进一步阅读建议

1. RISC-V国际基金会官方文档:https://riscv.org/technical/specifications/(RVV规范)2. 安路科技PH1A系列白皮书:访问安路官网(www.anlogic.com)3. IEEE Xplore论文库:搜索“RISC-V FPGA AI inference energy efficiency”4. GitHub开源项目:搜索“fpga-rvv-accelerator”或“VexRiscv”