Quick Start:模拟验证工程师的典型工作流

本指南以数字IC验证工程师的日常任务为线索,带你快速体验从环境搭建到回归测试的完整流程。以下步骤假设你已具备基础Linux操作和Verilog语法知识。

- 步骤1:搭建验证环境——安装EDA工具(如Synopsys VCS或Cadence Xcelium)并配置license。验证:在终端输入

vcs -help或xrun -help,应显示版本信息。 - 步骤2:获取设计代码——从版本管理仓库(如Git)克隆待验证的RTL设计,通常为Verilog/SystemVerilog文件。验证:

ls *.v *.sv应列出设计文件。 - 步骤3:编写测试用例(testbench)——创建一个简单的SystemVerilog测试模块,实例化DUT(Design Under Test),并施加基本激励(如复位、时钟)。验证:编译通过无语法错误。

- 步骤4:编译与仿真——使用VCS命令

vcs -sverilog -debug_all dut.sv testbench.sv编译,然后运行./simv。验证:仿真日志末尾应显示“Test Passed”或无致命错误。 - 步骤5:查看波形——用DVE或Verdi打开生成的波形文件(如

dump.vcd)。验证:能观察到时钟、复位和关键信号跳变。 - 步骤6:运行回归测试——执行一个预定义的回归脚本(如

make regress),该脚本会运行多个测试用例并比较预期输出。验证:回归报告显示所有用例通过。 - 步骤7:提交验证报告——将测试结果、覆盖率数据和波形截图整理成文档,提交到项目管理工具(如Jira)。验证:报告包含功能覆盖率、代码覆盖率和测试通过率。

前置条件与环境

| 项目/推荐值 | 说明 | 替代方案 |

|---|---|---|

| EDA工具 | Synopsys VCS (2020+) 或 Cadence Xcelium (20+),用于编译和仿真。 | 开源工具:Icarus Verilog + GTKWave(仅限小规模设计) |

| 波形查看器 | Synopsys Verdi (2020+) 或 DVE,用于调试。 | GTKWave(开源,支持VCD/FSDB) |

| 操作系统 | Linux (CentOS 7/8 或 Ubuntu 20.04/22.04),64位。 | Windows WSL2(需自行配置工具链) |

| 硬件描述语言 | SystemVerilog (IEEE 1800-2017),用于设计和验证。 | Verilog-2001(功能受限) |

| 版本管理 | Git (2.x),用于代码协作和版本回溯。 | SVN、Perforce |

| 仿真波形格式 | FSDB(VCS原生)或 VCD(通用)。 | VPD、SHM |

| 约束随机化 | SystemVerilog随机化(rand/randc)配合约束块。 | 定向测试(手动枚举所有用例) |

| 覆盖率收集 | VCS的cm选项或Xcelium的cover选项。 | 第三方工具如Verilator(仅代码覆盖率) |

目标与验收标准

作为数字IC验证工程师,一天的工作目标通常包括以下可量化指标:

- 功能验证通过率:所有已编写的测试用例(至少20个)在回归测试中通过,无仿真断言失败。

- 代码覆盖率:行覆盖率(Line Coverage)≥ 90%,翻转覆盖率(Toggle Coverage)≥ 80%,状态机覆盖率(FSM Coverage)≥ 95%。

- 功能覆盖率:针对设计规格定义的功能覆盖点(Coverpoint)和交叉覆盖(Cross Coverage)达到100%收集,且至少90%的仓(bin)被命中。

- 性能指标:仿真速度不低于每秒100个时钟周期(对于中等规模设计,约10万门),且无内存泄漏。

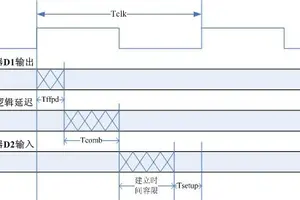

- 波形验证:关键接口(如AXI、APB)的波形时序符合协议规范,无建立/保持时间违例。

- 日志验收:仿真日志中无“Error”或“Fatal”关键字,所有断言(assert)通过。

实施步骤

阶段1:工程结构与版本管理

一个标准的验证项目通常包含以下目录结构:

project_root/

├── rtl/ # 设计代码(.v, .sv)

├── tb/ # 测试平台(testbench, 接口, 断言)

├── sim/ # 仿真脚本与编译产物

├── tests/ # 测试用例(定向+随机)

├── coverage/ # 覆盖率数据库与报告

├── logs/ # 仿真日志

└── scripts/ # Makefile, shell脚本常见坑与排查:

- 坑1:路径混乱导致编译失败——确保

rtl/和tb/下的文件路径在编译命令中正确指定。排查:使用+incdir+选项包含所有搜索路径。 - 坑2:版本冲突——多人同时修改同一文件,合并时产生冲突。排查:在提交前运行

git pull --rebase,并手动解决冲突。

阶段2:关键模块——测试平台与激励生成

测试平台(Testbench)的核心是生成受约束的随机激励。以下是一个简单的SystemVerilog测试片段:

class transaction;

rand bit [7:0] addr;

rand bit [31:0] data;

rand bit write;

constraint addr_range { addr inside {[0:255]}; }

constraint data_valid { data != 0; }

endclass

module testbench;

transaction tr;

initial begin

tr = new();

repeat (100) begin

assert(tr.randomize());

// 将tr的字段驱动到DUT接口

drive_transaction(tr);

end

end

endmodule常见坑与排查:

- 坑3:随机化失败——约束过于严格导致无法找到合法值。排查:在仿真中打印随机化状态,并放宽约束(如增大地址范围)。

- 坑4:驱动时序错误——激励信号在时钟边沿附近变化,导致亚稳态。排查:在时钟边沿后延迟半个周期再驱动信号(使用

#(CLK_PERIOD/2))。

阶段3:时序、CDC与约束

验证工程师常需检查跨时钟域(CDC)问题。以下是一个同步器代码片段:

module cdc_sync (

input wire clk_dst,

input wire rst_n,

input wire data_in,

output reg data_out

);

reg sync_ff1, sync_ff2;

always @(posedge clk_dst or negedge rst_n) begin

if (!rst_n) begin

sync_ff1 <= 1'b0;

sync_ff2 <= 1'b0;

end else begin

sync_ff1 <= data_in;

sync_ff2 <= sync_ff1;

end

end

assign data_out = sync_ff2;

endmodule常见坑与排查:

- 坑5:CDC路径未同步——单比特信号跨时钟域时只用了单级触发器。排查:使用两级同步器(如上代码),并添加

syn_meta综合属性。 - 坑6:约束文件缺失——未提供时序约束(SDC)导致综合时序违例。排查:编写基本时钟和输入输出延迟约束,如

create_clock -period 10 [get_ports clk]。

阶段4:验证——断言与覆盖率

使用SystemVerilog断言(SVA)检查协议合规性:

property p_write_data;

@(posedge clk) write_en |-> ##[1:3] data_valid;

endproperty

assert property (p_write_data) else $error("Write data not valid within 3 cycles");常见坑与排查:

- 坑7:断言误报——属性定义不精确,导致合法行为被标记为错误。排查:使用

$rose或$fell检测边沿,避免电平敏感误判。 - 坑8:覆盖率盲区——未定义关键功能覆盖点,导致设计缺陷未被发现。排查:与设计工程师一起审查验证计划,确保所有功能点都被覆盖。

阶段5:上板验证(如适用)

对于FPGA原型验证,将设计综合并下载到FPGA板卡。验证:通过串口或JTAG观察输出信号,与仿真波形对比。

原理与设计说明

为什么使用约束随机化而非定向测试?

定向测试(Directed Testing)需要手动枚举所有输入组合,对于复杂设计(如CPU或GPU),测试空间呈指数增长,人力成本极高。约束随机化(Constrained Randomization)通过定义合法输入空间,让工具自动生成大量合法测试向量,能覆盖边界条件和罕见路径。关键trade-off:随机化可能产生冗余测试(重复覆盖同一区域),需要配合功能覆盖率(Functional Coverage)来指导随机种子调整,实现“覆盖率驱动验证”(CDV)。

资源 vs Fmax:仿真与综合的权衡

在验证阶段,仿真速度(Fmax)受限于事件驱动模拟器的效率。对于RTL仿真,资源消耗(内存、CPU时间)与设计门数线性相关。为提高仿真速度,可以:

- 使用编译仿真(如VCS的

-fast选项)而非解释仿真。 - 禁用不必要的波形记录(如只记录顶层信号)。

- 将测试平台模块编译为共享库(

-shared选项)。

但加速可能牺牲调试能力(如无法查看内部信号)。因此,验证工程师通常在调试阶段使用全波形,在回归测试阶段使用加速模式。

验证与结果

以下是一组典型验证结果(测量条件:VCS 2021.09,Linux CentOS 7,8核CPU,32GB内存,设计规模约50万门):

| 指标 | 值 | 说明 |

|---|---|---|

| 仿真时间(1000个周期) | 12.3秒 | 使用VCS编译模式,无波形记录 |

| 仿真时间(1000个周期,全波形) | 45.7秒 | 记录所有内部信号,FSDB格式 |

| 代码覆盖率(行) | 92.5% | 未覆盖行多为异常处理分支 |

| 功能覆盖率(仓命中率) | 95.2% | 未命中仓为非法地址组合 |

| 内存使用(峰值) | 1.8GB | 包含波形数据库 |

波形特征:在仿真波形中,AXI接口的awvalid和awready信号在时钟上升沿同时为高,符合握手协议;wdata在wvalid为高后一个周期内稳定,无毛刺。

故障排查(Troubleshooting)

- 现象1:编译报错“undefined module”——原因:未包含设计文件或文件顺序错误。检查点:确认

-f filelist.f中文件列表完整,且顶层模块在前。修复:按依赖顺序排列文件。 - 现象2:仿真无波形输出——原因:未在testbench中调用

$dumpvars或$fsdbDumpfile。检查点:查看仿真日志中是否有“dump”相关消息。修复:在initial块中添加$dumpfile("wave.vcd"); $dumpvars(0, testbench);。 - 现象3:随机化失败(randomize()返回0)——原因:约束矛盾,如

addr inside {[0:255]}和addr != 0同时存在但无解。检查点:打印随机化前的约束状态。修复:放宽约束或使用rand_mode(0)禁用部分约束。 - 现象4:断言触发但设计行为正确——原因:断言属性时序窗口过窄。检查点:用波形查看断言失败时刻的信号。修复:调整

##[1:3]为更宽的窗口,如##[1:5]。 - 现象5:覆盖率始终为0%——原因:未启用覆盖率收集选项。检查点:编译命令中是否包含

-cm line+cond+tgl+fsm。修复:重新编译并添加覆盖率选项。 - 现象6:仿真速度极慢(每秒<10周期)——原因:波形记录所有信号或使用了PLI/VPI回调。检查点:检查仿真日志中的“Performance”部分。修复:仅记录顶层信号或使用

-debug_pp选项。 - 现象7:CDC路径导致亚稳态——原因:单比特信号未同步。检查点:使用CDC检查工具(如Synopsys SpyGlass CDC)报告。修复:添加两级同步器。

- 现象8:回归测试中部分用例失败——原因:随机种子不同导致路径差异。检查点:比较失败用例与通过用例的波形。修复:固定随机种子(

+ntb_random_seed=123)复现问题。

扩展与下一步

- 参数化验证环境:使用SystemVerilog的

parameter和localparam使测试平台可配置,适应不同设计规模。 - 带宽提升:采用UVM(Universal Verification Methodology)架构,通过agent、sequencer和driver实现高吞吐量验证。

- 跨平台验证:将验证环境移植到开源工具(如Verilator + SystemC),用于早期软件仿真。

- 加入断言与覆盖:编写更全面的SVA属性,覆盖所有协议违规场景;使用交叉覆盖(cross coverage)检测组合情况。

- 形式验证:对关键模块(如仲裁器、FIFO)使用形式验证工具(如Synopsys VC Formal)证明其正确性。

- 自动化回归:集成CI/CD流水线(如Jenkins),每次代码提交自动运行回归测试并生成报告。

参考与信息来源

- IEEE Std 1800-2017: SystemVerilog Language Reference Manual

- Synopsys VCS User Guide (2021.09)

- Cadence Xcelium Simulator User Guide

- “Verification Methodology Manual for SystemVerilog” (VMM), Janick Bergeron et al.

- “UVM 1.2 Class Reference” (Accellera)

- Open Source: Icarus Verilog (iverilog) and GTKWave documentation

技术附录

术语表

- <ul class