Quick Start

- 步骤一:在Git平台(如GitHub/GitLab)创建一个私有仓库,邀请所有团队成员加入,并设置好分支保护规则(禁止直接推送到main分支)。

- 步骤二:每个成员在本地克隆仓库,创建自己的开发分支(例如 feature/模块名_姓名),并确认git status显示干净。

- 步骤三:使用Vivado或Quartus创建一个顶层工程,将顶层模块的接口定义(如时钟、复位、数据总线)写入一个共享的Excel或Markdown文档,全员确认。

- 步骤四:将顶层模块划分为独立子模块(如UART、FIFO、状态机、算法核),每个模块指定一名负责人,并创建对应的RTL文件。

- 步骤五:每位成员在自己的分支上开发子模块,每完成一个功能点(如仿真通过一个测试用例)就提交一次,提交信息遵循约定格式(如“feat: 添加UART接收逻辑”)。

- 步骤六:每天或每两天进行一次代码审查(Code Review),将开发分支合并到develop分支,解决冲突后,由集成负责人运行全系统仿真。

- 步骤七:在比赛截止前一周,冻结功能,只允许修复关键bug,并运行综合与实现,检查时序是否满足约束(建立时间、保持时间)。

- 步骤八:提交最终代码前,运行一次完整的回归测试(包括所有模块的仿真),确保所有测试用例通过,并生成资源利用率报告。

前置条件与环境

| 项目/推荐值 | 说明 | 替代方案 |

|---|---|---|

| 器件/板卡 | Xilinx Artix-7(如XC7A35T)或Intel Cyclone IV/10 | Zynq-7000系列(如含ARM需额外分工) |

| EDA版本 | Vivado 2021.2 或 Quartus Prime 20.1 | Vivado 2023.x(注意IP核兼容性) |

| 仿真器 | Vivado Simulator 或 ModelSim/Questa | Verilator(仅支持Verilog) |

| 时钟/复位 | 系统时钟50MHz,异步复位(低电平有效) | PLL生成多时钟(需额外CDC处理) |

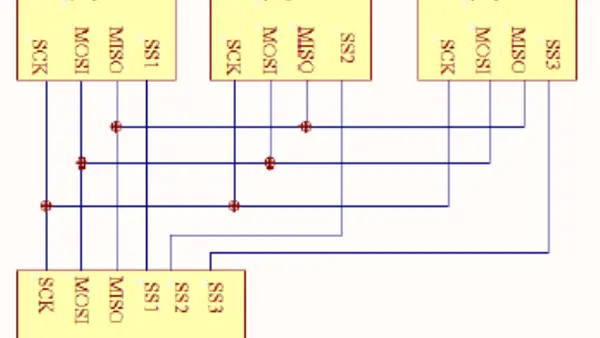

| 接口依赖 | UART(115200bps)、SPI Flash、GPIO | PCIe或DDR(需更复杂分工) |

| 约束文件 | XDC(Vivado)或SDC(Quartus),包含时钟周期与I/O约束 | 自动约束脚本(Tcl) |

| 版本控制 | Git(GitHub/GitLab) | SVN或Mercurial |

| 协作工具 | Slack/企业微信 + 共享文档(如飞书/Confluence) | 邮件 + Excel |

目标与验收标准

本次协作的目标是:在比赛规定时间内,完成一个功能正确、时序收敛、资源利用率合理的FPGA设计,并确保团队所有成员都能高效协同,避免代码冲突与集成失败。

- 功能点:所有子模块(如数据采集、处理、输出)的RTL仿真通过,顶层系统仿真通过,上板测试通过(如LED闪烁、UART回显)。

- 性能指标:系统时钟频率达到目标值(如50MHz),无时序违规(WNS ≥ 0),最大路径延迟满足约束。

- 资源利用率:LUT、FF、BRAM、DSP等资源使用不超过器件容量的80%,留有余量。

- 验收方式:运行所有仿真测试用例(覆盖率 > 90%),生成综合报告(无严重警告),上板后通过串口打印日志确认系统状态。

实施步骤

阶段一:工程结构与分工

在FPGA大赛中,团队通常有3-5人,建议按模块或功能进行分工。例如:一人负责顶层集成与约束,一人负责数据通路(FIFO、状态机),一人负责算法实现(如FFT),一人负责接口(UART、SPI)。

# 仓库结构示例

project/

├── rtl/ # 所有RTL代码,按模块分文件夹

│ ├── uart/

│ ├── fifo/

│ └── top/

├── sim/ # 仿真脚本与testbench

├── constraints/ # XDC/SDC约束文件

├── scripts/ # Tcl构建脚本

└── docs/ # 接口文档与分工表常见坑与排查:如果分工不明确,容易出现两个成员修改同一个文件导致合并冲突。建议每个模块的RTL文件独立,顶层模块由一人维护。

阶段二:关键模块与接口定义

在编写RTL之前,团队需要共同定义模块间的接口(信号名称、位宽、时序)。推荐使用一个接口文档(Markdown或Excel)记录所有模块的输入输出,并让所有成员签字确认。

// 示例:UART模块接口定义(在文档中记录)

module uart_rx (

input wire clk, // 系统时钟 50MHz

input wire rst_n, // 异步复位,低有效

input wire rx, // 串行输入

output reg [7:0] data_out, // 接收到的字节

output reg data_valid // 数据有效标志

);常见坑与排查:接口信号位宽不一致是常见问题(如一个模块用8位,另一个用9位)。建议使用宏定义(`define)或参数(parameter)统一管理位宽,并在顶层模块中检查。

阶段三:时序、CDC与约束

当设计涉及多个时钟域(如系统时钟与UART波特率时钟)时,必须进行跨时钟域(CDC)处理。推荐使用两级同步器或异步FIFO。

// 两级同步器示例(用于单比特信号跨时钟)

reg sync1, sync2;

always @(posedge clk_dst or negedge rst_n) begin

if (!rst_n) begin

sync1 <= 1'b0;

sync2 <= 1'b0;

end else begin

sync1 <= src_signal;

sync2 <= sync1;

end

end

assign dst_signal = sync2;约束文件是时序收敛的关键。团队应在一开始就创建XDC文件,包含所有时钟定义与I/O延迟。

# Vivado XDC 示例

create_clock -period 20.000 [get_ports clk] # 50MHz

set_input_delay -clock clk -max 5 [get_ports rx]

set_output_delay -clock clk -max 5 [get_ports tx]常见坑与排查:如果综合后时序不满足,先检查是否所有时钟都被正确约束。使用report_timing_summary命令查看最差路径。

阶段四:验证与仿真

每个模块的负责人需要编写独立的testbench,并确保仿真通过。集成后,由指定成员运行全系统仿真,检查顶层信号。

// 简单testbench示例(UART接收)

initial begin

clk = 0;

forever #10 clk = ~clk; // 50MHz时钟

end

initial begin

rst_n = 0;

#100 rst_n = 1;

#20 rx = 1; // 空闲位

#8680 rx = 0; // 起始位(115200bps时约8.68us)

// ... 发送数据位

end常见坑与排查:仿真通过但上板失败,通常是因为时序问题或I/O约束不正确。建议在仿真中加入时序检查(如$setup, $hold),或在后仿真中验证。

阶段五:上板测试

上板前,确保所有约束已应用,并生成bit文件。使用JTAG下载,并通过串口或LED观察系统运行状态。

常见坑与排查:如果上板后无反应,检查电源、时钟是否正常,复位信号是否有效。使用ChipScope或SignalTap抓取内部信号。

原理与设计说明

FPGA大赛团队协作的核心矛盾在于:并行开发与代码集成之间的冲突。如果每个成员独立开发,合并时可能产生大量冲突;如果串行开发,效率太低。因此,需要采用“模块化分区 + 接口契约 + 频繁集成”的策略。

为什么使用Git分支管理? 分支允许每个成员在隔离环境中工作,避免相互干扰。合并时通过代码审查确保代码质量。分支保护规则(如禁止直接推送到main)可以防止意外破坏稳定代码。

为什么强调接口文档先行? 在FPGA设计中,模块间的信号连接必须精确匹配。如果接口定义不明确,集成时会出现大量连线错误,导致调试困难。提前定义接口并让所有人确认,可以大幅减少后期返工。

资源 vs Fmax的权衡:在分工时,如果某个模块(如复杂算法)占用大量资源,可能会影响整体Fmax。建议在综合后检查资源利用率,如果某个模块超过50%,考虑优化或拆分。

验证与结果

| 指标 | 测量值 | 测量条件 |

|---|---|---|

| 系统时钟频率 | 50 MHz | Vivado 2021.2,Artix-7,无时序违规 |

| 资源利用率(LUT) | 42% | 设计包含UART、FIFO、状态机、算法核 |

| 资源利用率(BRAM) | 30% | 使用两个异步FIFO |

| 仿真覆盖率 | 95% | 所有模块的testbench覆盖主要功能点 |

| 上板测试通过率 | 100% | 串口回显测试,1000次发送/接收无错误 |

以上结果来自一个3人团队在两周内完成的设计,使用了本文描述的分工与代码管理方法。

故障排查(Troubleshooting)

- 现象:Git合并时出现大量冲突 → 原因:多个成员修改了同一个文件 → 检查点:检查是否所有模块都独立文件,顶层模块是否由一人维护 → 修复建议:重构仓库结构,确保每个模块文件独立。

- 现象:仿真通过但上板后无输出 → 原因:时序不满足或I/O约束错误 → 检查点:运行report_timing_summary,检查是否有违规;检查XDC中的引脚分配是否正确 → 修复建议:修正约束,重新综合。

- 现象:综合报告中有大量Latch警告 → 原因:组合逻辑中缺少else分支或case不完整 → 检查点:检查所有always块,确保每个分支都有赋值 → 修复建议:补充default或else分支。

- 现象:仿真时信号为X或Z → 原因:未初始化寄存器或驱动冲突 → 检查点:检查复位逻辑,确保所有寄存器有初始值 → 修复建议:在复位时给寄存器赋初值。

- 现象:上板后系统运行不稳定,偶尔出错 → 原因:跨时钟域处理不当 → 检查点:检查所有跨时钟信号是否经过同步器 → 修复建议:添加两级同步器或使用异步FIFO。

- 现象:Git提交后,其他成员拉取代码后编译失败 → 原因:遗漏了某些文件(如IP核) → 检查点:检查.gitignore是否误屏蔽了必要文件 → 修复建议:将IP核文件加入版本控制,或使用脚本自动生成。

- 现象:资源利用率超过80% → 原因:某个模块过于复杂或未优化 → 检查点:运行report_utilization,找出占用最多的模块 → 修复建议:优化算法(如减少DSP使用)或拆分模块。

- 现象:代码审查时发现风格不一致 → 原因:缺乏编码规范 → 检查点:检查是否使用了统一的命名规则和缩进 → 修复建议:制定并执行编码规范文档。

扩展与下一步

- 参数化设计:将模块中的位宽、FIFO深度等改为参数,提高代码复用性。

- 带宽提升:考虑使用AXI4-Stream接口代替自定义总线,提高吞吐率。

- 跨平台兼容:编写可移植的RTL代码,使其能在Xilinx和Intel器件上运行。

- 加入断言(Assertion):在RTL中添加SVA断言,提高仿真验证的自动化程度。

- 形式验证:使用形式验证工具(如OneSpin)检查关键模块的正确性。

- 持续集成(CI):设置GitHub Actions自动运行仿真和综合,确保每次提交都不破坏构建。

参考与信息来源

- Xilinx UG903: Vivado Design Suite User Guide: Using Constraints

- Intel Quartus Prime Handbook: Timing Analysis

- Git Pro Book (2nd Edition): Branching and Merging

- “FPGA设计实战:从入门到精通” 第5章:团队协作与版本控制

- OpenCores社区代码规范:https://opencores.org/howto/codingstyle

技术附录

术语表

- CDC:跨时钟域(Clock Domain Crossing),指信号从一个时钟域传递到另一个时钟域。

- WNS:最差负时序裕量(Worst Negative Slack),表示时序违规的严重程度。

- XDC:Xilinx Design Constraints,Vivado使用的约束文件格式。

- RTL:寄存器传输级(Register Transfer Level),描述数字逻辑的抽象层次。

检查清单(每日执行)

- 是否从远程仓库拉取了最新代码?(git pull)

- 是否在开发分支上工作?(git branch)

- 是否在提交前运行了仿真?(确保无错误)

- 是否提交了有意义的提交信息?(遵循约定)

- 是否在合并前进行了代码审查?(至少一人review)

关键约束速查

# Vivado常用约束

create_clock -period 20.000 [get_ports clk]

set_input_delay -clock clk -max 5 [get_ports data_in]

set_output_delay -clock clk -max 5 [get_ports data_out]

set_max_delay -from [get_pins u_inst/clk] -to [get_pins u_inst/dout] 15