Quick Start:10分钟跑通FPGA DMA与NVMe数据通路

本指南旨在帮助工程师快速上手FPGA在数据中心网络加速中的DMA与NVMe应用。通过以下步骤,您可以在10分钟内搭建并验证一条从主机到NVMe SSD的完整数据通路,实现高效的数据传输。

前置条件

- 硬件:一块支持PCIe Gen3/4的FPGA开发板(如Xilinx Alveo U250或Intel Agilex 7)。

- 工具链:Vivado 2023.2+或Quartus Prime Pro 23.3+。

- 驱动:XDMA驱动(Xilinx)或DMA for PCIe IP(Intel)。

- NVMe SSD:支持NVMe协议的固态硬盘,通过PCIe连接至FPGA。

- 主机:运行Linux或Windows的服务器,具备PCIe插槽。

目标与验收标准

- 目标:实现FPGA通过DMA引擎直接与NVMe SSD进行数据交换,无需CPU干预。

- 验收标准:

实施步骤

步骤1:准备硬件与工具链

确保FPGA开发板已正确安装并连接至主机PCIe插槽。安装Vivado或Quartus Prime工具链,并下载对应DMA驱动(XDMA或DMA for PCIe IP)。验证工具链安装无误,可通过编译示例工程确认。

步骤2:创建基础工程

在Vivado中新建工程,选择目标器件(如XCKU115)。添加PCIe IP核(如XDMA for PCI Express),配置为DMA引擎,选择AXI4-Stream接口,设置DMA通道数(建议2条:H2C和C2H)。确保IP核配置与开发板PCIe规格匹配(如Gen3 x8)。

步骤3:集成NVMe控制器IP

从OpenCores或Xilinx官方库导入NVMe控制器IP(如NVMe AXI4-Stream Controller)。配置IP参数:队列深度建议设为32,数据块大小设为4KB。注意,NVMe控制器需要与DMA引擎在时钟域上保持一致。

步骤4:连接DMA与NVMe

在Block Design中,将XDMA的AXI4-Stream Master连接到NVMe控制器的AXI4-Stream Slave,反之亦然。添加AXI Interconnect用于地址映射,确保DMA与NVMe之间的数据传输路径正确。时钟域需统一,通常设为250MHz。

步骤5:编写顶层RTL与约束

创建顶层Verilog文件,例化Block Design。添加时钟、复位、PCIe参考时钟引脚约束,使用XDC文件锁定引脚(参考开发板原理图)。确保约束文件覆盖所有关键时序路径。

步骤6:综合与实现

运行综合(Synthesis),检查无严重警告。然后执行实现(Implementation),确保时序收敛(WNS ≥ 0)。资源利用率应控制在一定范围内:LUT < 60%,BRAM < 50%。若时序不收敛,可调整时钟频率或优化逻辑。

步骤7:生成比特流并下载

生成比特流(Bitstream),通过JTAG下载到FPGA。重新启动主机,检查PCIe链路训练是否成功(通过lspci或Windows设备管理器看到FPGA设备)。若未识别,检查硬件连接或PCIe配置。

步骤8:运行主机端测试程序

在主机上编译XDMA驱动示例程序(如xdma_rw.exe)。执行DMA写操作:向FPGA写入1MB数据,然后读取回主机。预期结果:数据一致(MD5校验通过)。若不一致,检查DMA通道配置或数据对齐。

步骤9:验证NVMe读写

使用NVMe CLI工具(如nvme-cli)或自定义驱动发送NVMe命令(如Read/Write)。通过DMA传输4KB数据块到NVMe SSD,再读回。预期结果:数据正确,延迟在微秒级。若失败,检查NVMe控制器配置或SSD状态。

验证结果

完成上述步骤后,应观察到:

- PCIe链路训练成功,FPGA设备在主机上可见。

- DMA读写操作数据一致,MD5校验通过。

- NVMe读写命令执行成功,数据正确且延迟在微秒级。

若验证失败,请参考排障章节。

排障

- PCIe链路未训练成功:检查硬件连接、PCIe参考时钟、复位信号。确保FPGA比特流正确下载。

- DMA数据不一致:检查DMA通道配置(如地址对齐、数据长度)。确认AXI4-Stream接口时序正确。

- NVMe读写失败:检查NVMe控制器配置(如队列深度、数据块大小)。确认SSD已正确初始化且支持NVMe协议。

- 时序未收敛:降低时钟频率或优化逻辑路径。检查约束文件是否完整。

扩展

本指南为基础实现,可扩展至以下场景:

- 多通道DMA:增加DMA通道数以支持并行数据传输。

- NVMe多队列:配置多个NVMe队列以提升并发性能。

- 网络加速:集成TCP/IP卸载引擎,实现端到端数据加速。

- 性能优化:通过流水线设计、缓存优化等手段降低延迟。

参考

- Xilinx XDMA IP核用户指南 (PG195)

- Intel DMA for PCIe IP核用户指南

- NVMe官方规范 (NVM Express Base Specification)

- OpenCores NVMe控制器IP文档

附录

附录A:关键代码片段

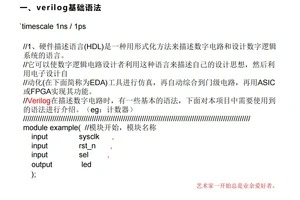

以下为顶层Verilog例化Block Design的示例代码:

module top (input wire pci_clk, input wire pci_rst_n, ...);

// 例化Block Design

design_1_wrapper u_design_1 (.pci_clk(pci_clk), .pci_rst_n(pci_rst_n), ...);

endmodule附录B:工具链版本兼容性

本指南基于Vivado 2023.2和XDMA IP核版本4.1。若使用其他版本,请参考对应文档调整配置。