在FPGA设计中,跨时钟域(Cross-Clock Domain, CDC)信号处理是保障系统长期稳定运行的关键技术。当信号在异步或频率/相位关系不确定的时钟域间传递时,若处理不当,极易引发亚稳态(Metastability),导致数据采样错误、状态机跑飞乃至系统功能失效。本文旨在提供一套从快速搭建到深入验证的CDC同步器设计实践流程,重点剖析亚稳态的产生机理、规避策略及系统性验证方法,帮助设计者构建可靠的CDC处理路径。

快速上手指南

- 步骤一:工程准备。创建一个包含两个独立异步时钟(例如 clk_a = 100MHz, clk_b = 50MHz)的FPGA工程。

- 步骤二:模块实例化。在RTL代码中,为从clk_a域到clk_b域的单比特控制信号(如 pulse_a)实例化一个两级同步器模块。

- 步骤三:核心同步逻辑。同步器核心是在clk_b时钟域内,使用两级(或更多)级联的触发器对异步输入信号进行采样。

- 步骤四:仿真验证。编写测试平台(Testbench),使用随机或周期性间隔驱动 pulse_a 信号。

- 步骤五:波形确认。运行仿真,观察同步器输出信号(如 pulse_b_synced)的波形。应确认输出相比输入有1-2个clk_b周期的固定延迟,且波形干净、无毛刺或振荡。

- 步骤六:时序分析。综合与实现后,查阅静态时序分析(STA)报告,确保没有因跨时钟域路径而产生的建立时间(Setup)或保持时间(Hold)违例。

- 步骤七:时序约束。添加必要的时序约束,使用

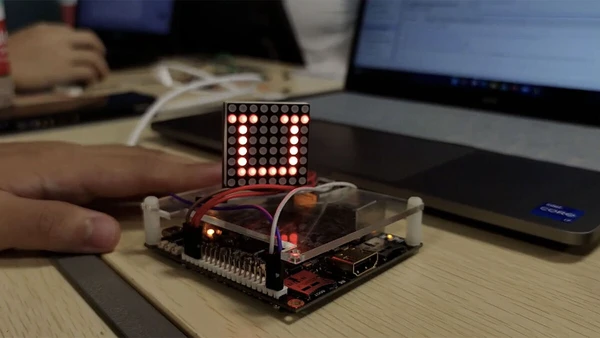

set_clock_groups -asynchronous或set_false_path对异步时钟域之间的路径进行正确约束。 - 步骤八:硬件调试。上板验证,通过集成逻辑分析仪(ILA/ChipScope/SignalTap)抓取同步前后的信号,确认功能正确且无异常脉冲。

前置条件与环境要求

| 项目 | 推荐值/要求 | 说明与替代方案 |

|---|---|---|

| FPGA器件/板卡 | Xilinx 7系列 / Intel Cyclone V及以上 | 需支持至少两个独立的全局时钟网络。开发板应有外部时钟源或可编程时钟芯片。 |

| EDA工具版本 | Vivado 2018.3 / Quartus Prime 18.1 及以上 | 确保工具链完整,支持CDC专项分析工具(如Vivado的CDC向导、Synopsys SpyGlass CDC)。 |

| 仿真工具 | Vivado Simulator / ModelSim / VCS | 用于行为级和时序后仿真,验证同步器功能与亚稳态恢复情况。 |

| 时钟源 | 两个异步时钟,频率比非整数 | 例如100MHz与50MHz,或77MHz与125MHz。避免使用同源且相位关系固定的时钟,否则失去CDC验证意义。 |

| 待同步信号 | 单比特脉冲信号(电平或边沿) | 这是最基本的CDC场景。多比特数据需采用握手、异步FIFO或格雷码同步方案。 |

| 约束文件 | 包含时钟定义与CDC路径约束 | 必须正确定义所有时钟,并对异步时钟域之间的路径进行适当约束(如 set_clock_groups -asynchronous)。 |

| 验证手段 | 仿真(前仿/后仿)、静态时序分析(STA)、上板调试(ILA/SignalTap) | 三者结合是验证CDC设计可靠性的黄金标准,缺一不可。 |

目标与验收标准

- 功能正确性:源时钟域的有效信号(脉冲或电平)能稳定、无丢失地传递到目标时钟域,允许固定的同步延迟(通常为1-2个目标时钟周期)。

- 亚稳态规避:通过同步器将亚稳态发生的概率降低到系统可接受的水平(例如平均无故障时间MTBF > 100年)。在仿真中,不应观察到因亚稳态导致的、在目标时钟域持续振荡或传播的异常信号。

- 时序收敛:静态时序分析(STA)报告中,无因跨时钟域路径而产生的建立时间(Setup)或保持时间(Hold)违例。工具报告的“跨时钟域”警告应被合理的时序约束所豁免。

- 资源可控:单个两级同步器消耗约2个触发器(FF)和少量查找表(LUT),资源开销应在预期范围内。

- 验证完备性:通过仿真波形、STA报告和上板逻辑分析仪抓取的数据,完成对同步器有效性的三重验证闭环。

详细实施步骤

1. 工程结构与模块划分

建议创建清晰的顶层模块(top),在其中实例化以下子模块:两个时钟生成模块(或直接使用外部输入时钟)、发送模块(工作在clk_a域)、接收模块(工作在clk_b域)以及核心的同步器模块。将同步器模块设计为独立的、参数化的模块,有利于代码复用和团队协作。

2. 关键模块:两级同步器RTL实现

以下是经典的参数化两级触发器同步器代码,用于同步单比特或多比特(但需注意,多比特直接同步可能产生数据一致性问题)信号。

// 经典的两级触发器同步器,用于同步单比特信号

// 注意:对于多比特总线,此方案不能保证数据一致性,需采用其他机制(如格雷码、握手、FIFO)。

module sync_2stage #(

parameter WIDTH = 1

) (

input wire clk_dst, // 目标时钟域时钟

input wire rst_n_dst, // 目标时钟域复位(推荐异步释放,同步生效)

input wire [WIDTH-1:0] din_async, // 来自源时钟域的异步输入

output reg [WIDTH-1:0] dout_sync // 同步到目标时钟域的输出

);

reg [WIDTH-1:0] sync_reg0; // 第一级同步寄存器(亚稳态可能发生在此)

reg [WIDTH-1:0] sync_reg1; // 第二级同步寄存器(输出稳定信号)

always @(posedge clk_dst or negedge rst_n_dst) begin

if (!rst_n_dst) begin

sync_reg0 <= {WIDTH{1'b0}};

sync_reg1 <= {WIDTH{1'b0}};

end else begin

sync_reg0 <= din_async; // 第一级采样,承受亚稳态风险

sync_reg1 <= sync_reg0; // 第二级采样,极大降低亚稳态传播概率

end

end

assign dout_sync = sync_reg1; // 输出第二级寄存器的值

endmodule3. 机制分析与设计要点

亚稳态成因:当异步输入信号的变化发生在目标时钟触发器的建立时间(Tsu)和保持时间(Th)窗口内时,触发器的输出可能进入一个非0非1的中间电压状态,并在不确定的时间后随机稳定到0或1,此即亚稳态。两级同步器的核心思想是为亚稳态提供额外的恢复时间。第一级寄存器负责采样异步信号并承受亚稳态风险,第二级寄存器在至少一个完整时钟周期后采样第一级的输出。此时,第一级输出已极大概率从亚稳态恢复为稳定逻辑电平,从而确保第二级输出是稳定的。

同步器级数选择:两级同步器是工程中最常用的折衷方案,能在合理资源开销下将MTBF提升至数百年甚至更长。对于极高可靠性要求或极高速时钟的系统,可考虑使用三级同步器,但这会额外增加一个周期的延迟。

4. 验证结果评估

- 仿真波形:在测试平台中,应故意让异步输入信号的变化随机落在目标时钟的采样窗口附近。观察

sync_reg0,可能在极少数情况下会出现短暂的“X”态(亚稳态的仿真表现),但sync_reg1和dout_sync必须始终保持为稳定的0或1。 - 时序报告:在STA报告中,重点关注被

set_clock_groups约束的路径,应显示为“无需检查”或“假路径”。确保没有其他未被约束的CDC路径产生违例。 - 硬件实测:通过ILA抓取信号,对比

din_async和dout_sync,确认功能逻辑正确,且输出信号干净,没有因亚稳态未能完全恢复而产生的窄脉冲或毛刺。

常见问题与排查

- 问题:仿真中同步器输出仍有毛刺或振荡。

排查:检查测试激励,确保异步输入信号的变化相对于目标时钟是真正随机的。检查同步器模块的复位逻辑是否正确,确保第二级寄存器不会直接采样到不稳定的复位状态。 - 问题:时序报告中仍有CDC路径违例。

排查:确认时序约束文件(.xdc/.sdc)已正确设置,并使用report_clock_interaction或类似命令检查时钟域分组是否生效。确保约束覆盖了所有异步时钟对。 - 问题:同步后的脉冲丢失。

排查:源时钟域的脉冲宽度必须大于目标时钟周期,否则可能无法被采样到。对于边沿检测信号,需在源时钟域先将边展宽为一个足够宽的电平脉冲,再进行同步。

方案扩展与进阶

单比特信号同步是CDC的基础。对于更复杂的场景,需要采用不同的同步策略:

- 多比特数据总线:严禁对总线中的每一位单独使用同步器,因为各位的延迟可能不同,导致目标时钟域采样到不一致的“撕裂数据”。应采用异步FIFO、握手协议(Req/Ack)或先将数据转换为格雷码再同步(仅适用于连续计数变化的数据)。

- 复位信号的同步:系统的全局复位信号通常是异步的,必须使用“异步复位,同步释放”电路将其同步到各个时钟域,以避免复位撤除时的亚稳态。

- 脉冲同步与边沿检测:若需将源时钟域的脉冲同步到目标时钟域,或检测源时钟域的边沿,通常采用“脉冲展宽 → 电平同步 → 边沿检测”的组合电路。

参考与附录

- 平均无故障时间(MTBF)计算:MTBF与触发器本身的亚稳态特性参数(TMET、τ)、时钟频率、数据变化率有关。可通过公式估算,现代FPGA中两级同步器通常能轻松实现数百年以上的MTBF。

- 工具CDC分析:强烈建议使用Vivado中的CDC向导(Report CDC)、或第三方工具如SpyGlass CDC进行专项分析。这些工具能自动识别CDC路径,并检查是否存在不安全的同步结构(如多比特直接同步)。

- 设计原则:牢记“单比特信号用同步器,多比特数据用协议(FIFO/握手)”的基本原则。在设计初期就规划好时钟域,并明确各域之间的通信接口与同步方案。