随着Chiplet(芯粒)技术成为高性能计算与异构集成的主流,系统级验证的复杂度呈指数级增长。传统的软件仿真与硬件仿真器(Emulator)在验证周期与成本上面临巨大挑战。FPGA原型验证凭借其接近真实硬件的运行速度、相对较低的成本以及出色的灵活性,在2026年的Chiplet系统级验证流程中,已从“可选”演变为“关键路径”。本文旨在提供一份可执行的实施指南,帮助团队快速构建并运行一个面向Chiplet系统的FPGA原型验证平台,聚焦于流程、关键技术与避坑要点。

Quick Start

- 步骤1:定义验证范围。明确本次原型验证的目标子系统(例如,一个计算芯粒+一个高速互连芯粒+一个内存控制器芯粒),并确定需要挂载到FPGA板上的真实外设(如DDR、PCIe、以太网)。

- 步骤2:准备RTL与约束。获取目标Chiplet子系统的可综合RTL代码。准备或创建FPGA目标板卡的引脚约束文件(.xdc或.sdc)和时钟约束。

- 步骤3:搭建工程框架。在Vivado/Quartus中创建新工程,选择正确的FPGA器件型号。将RTL源代码、约束文件、IP核(如DDR控制器、PCIe硬核)添加到工程中。

- 步骤4:插入原型验证专用逻辑。在顶层模块中实例化FPGA与板载外设的接口适配逻辑(如AXI Interconnect、时钟域转换桥、调试探针逻辑)。

- 步骤5:运行综合与实现。执行综合(Synthesis)、布局布线(Implementation)。重点关注时序报告(Timing Report)中的建立/保持时间违例。

- 步骤6:生成并下载比特流。在时序收敛后,生成比特流文件(.bit)。通过JTAG或PCIe将比特流下载到FPGA原型板上。

- 步骤7:基础功能测试。通过板载LED、串口或嵌入式逻辑分析仪(ILA)观察关键信号,验证系统是否完成基本复位、时钟启动和配置流程。

- 步骤8:运行软件测试向量。通过PCIe或以太网接口,从主机PC向FPGA原型加载并运行简单的裸机(Bare-metal)或Linux驱动测试程序,验证处理器核与互连功能。

- 预期结果:FPGA板卡上电后,系统启动,可通过主机软件与原型进行基本读写交互,关键功能点测试通过。

- 失败先查:1) 时钟和复位信号是否稳定;2) 引脚约束是否正确;3) 比特流下载模式(JTAG/主模式)是否匹配板卡设置。

前置条件与环境

| 项目 | 推荐值/配置 | 说明 | 替代方案/注意点 |

|---|---|---|---|

| FPGA原型板卡 | Xilinx Alveo U250 / Intel Stratix 10 GX | 高容量、高带宽,支持多路高速收发器与HBM/DDR4。 | 根据Chiplet接口带宽需求选择。多片FPGA互联需专用载板。 |

| EDA工具版本 | Vivado 2023.2+ / Quartus Prime 22.1+ | 支持最新器件与IP,优化了大规模设计编译策略。 | 版本需与FPGA器件和IP核许可证兼容。 |

| 仿真环境 | VCS / QuestaSim / XSIM | 用于在FPGA综合前进行RTL级功能验证。 | 可先用开源工具如Verilator做快速检查。 |

| 主时钟频率 | FPGA内部逻辑 100-250 MHz | Chiplet RTL通常为GHz级,需通过时钟分频或降频适配。 | 关键路径可能需手动约束或流水线优化。 |

| 关键接口 | AXI4 / AXI-Stream / CXL / UCIe (仿真模型) | Chiplet间主流互连协议。FPGA原型需实现协议桥接或行为模型。 | 早期可使用简化AXI接口验证功能,后期集成PHY IP。 |

| 约束文件 | .xdc (Xilinx) / .sdc (Intel) | 必须包含时钟定义、I/O延迟、时序例外、多周期路径。 | 错误的约束是时序违例和功能错误的主要根源。 |

| 调试工具 | Vivado ILA / SignalTap II | 片上逻辑分析仪,用于实时抓取内部信号。 | 需预留足够的触发和存储深度,会占用RAM资源。 |

| 主机交互接口 | PCIe Gen3/4 x8 / 10G Ethernet | 用于高速数据传输、测试向量加载和调试信息回传。 | 确保主机驱动和DMA引擎已正确集成。 |

目标与验收标准

本指南旨在指导完成一个可运行的Chiplet子系统FPGA原型,具体验收标准如下:

- 功能正确性:原型能够正确执行一组预定义的验证测试套件(Test Suite),覆盖主要的数据通路、控制流和中断机制,与RTL仿真结果一致。

- 时序收敛:设计在目标FPGA上实现后,无建立时间(Setup)和保持时间(Hold)违例。最差负时序余量(Worst Negative Slack, WNS)大于 -0.1ns。

- 资源利用率:关键资源(LUT、FF、BRAM、DSP)利用率不超过目标FPGA容量的85%,为后续调试逻辑和设计修改留出余量。

- 关键性能指标:实测的互连带宽(如AXI总线带宽)达到理论值的70%以上;端到端的事务延迟在预期范围内。

- 调试与观测能力:成功集成至少2个片上逻辑分析仪(ILA)探针,能够稳定触发并捕获关键总线事务和状态机跳转。

- 验收方式:对比测试日志、ILA捕获波形与仿真参考波形;通过性能测试脚本输出带宽与延迟报告。

实施步骤

阶段一:工程结构与接口适配

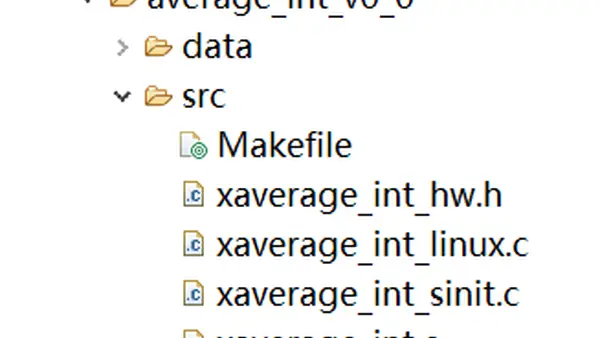

创建清晰的目录结构,并设计顶层Wrapper模块,负责将Chiplet RTL与FPGA板级资源连接。

// 顶层模块示例框架 (top_fpga_wrapper.v)

module top_fpga_wrapper (

input wire fpga_sys_clk_p, // 板载差分时钟

input wire fpga_sys_rst_n, // 板载复位

// PCIe接口引脚...

// DDR接口引脚...

output wire [3:0] user_leds // 调试LED

);

// --- 时钟与复位生成 ---

wire clk_200m, clk_100m, locked;

wire sys_rst = ~locked || ~fpga_sys_rst_n; // 系统复位

clk_wiz_0 u_clk_wiz (...); // 使用Clock Wizard IP

// --- Chiplet子系统实例化 ---

wire chiplet_axi_aclk = clk_100m;

wire chiplet_axi_aresetn = ~sys_rst;

// AXI等接口信号声明...

chiplet_subsystem u_chiplet_subsystem (

.aclk (chiplet_axi_aclk),

.aresetn(chiplet_axi_aresetn),

// 连接内部AXI总线...

);

// --- FPGA板载外设适配层(如AXI到DDR控制器)---

axi_interconnect_0 u_axi_ic (...); // AXI互联IP

ddr4_controller_0 u_ddr4_ctrl (...); // DDR控制器IP

// --- 调试与观测逻辑 ---

ila_0 u_ila_axi_monitor (...); // 实例化ILA IP,监控AXI总线

assign user_leds[0] = locked;

assign user_leds[1] = ~sys_rst;

endmodule常见坑与排查:

- 坑1:时钟域混乱。Chiplet RTL可能包含多个时钟域,直接连接到FPGA单一时钟会导致CDC问题。排查:检查RTL中的时钟输入端口,在Wrapper中为每个时钟域生成独立的时钟网络,并在跨时钟域接口插入FIFO或同步器。

- 坑2:复位信号异步释放。直接使用板载复位按钮产生的信号可能导致亚稳态。排查:对输入的异步复位信号进行同步化处理,或使用时钟IP产生的“locked”信号参与生成系统复位。

阶段二:时序约束与物理实现

正确的约束是时序收敛的基石。创建主约束文件。

# 时钟约束示例 (constraints.xdc)

# 主板时钟输入 200MHz差分

create_clock -name sys_clk -period 5.000 [get_ports fpga_sys_clk_p]

# 生成的时钟 100MHz

create_generated_clock -name clk_100m -source [get_pins u_clk_wiz/clk_out1] \

-divide_by 2 -multiply_by 1 [get_pins u_clk_wiz/clk_out1]

# 虚拟时钟,用于约束与外部芯片(如DDR颗粒)的接口

create_clock -name virt_ddr_clk -period 1.333

# 输入输出延迟约束(以DDR接口为例)

set_input_delay -clock virt_ddr_clk -max 0.6 [get_ports ddr_dq*]

set_output_delay -clock virt_ddr_clk -max 0.5 [get_ports ddr_dq*]

# 多周期路径约束(如果存在)

set_multicycle_path -setup 2 -from [get_clocks clk_100m] -to [get_clocks clk_200m]

# 伪路径约束(跨时钟域路径,由同步器保证正确性)

set_false_path -from [get_clocks clk_100m] -to [get_clocks clk_200m]常见坑与排查:

- 坑3:缺失I/O延迟约束。导致与外部存储器或接口芯片通信不稳定。排查:查阅FPGA板卡和外部器件的数据手册,严格计算并设置

set_input_delay/set_output_delay。 - 坑4:未约束生成时钟。由PLL或MMCM产生的时钟必须用

create_generated_clock约束,否则工具无法正确分析其衍生路径的时序。排查:在综合后打开网表,检查所有时钟网络的来源,确保每个时钟都有定义。

阶段三:调试与上板验证

利用ILA进行实时调试。在设计中标记需要观测的网络(Debug Net),并在实现后设置触发条件。

// 在RTL中标记调试信号 (* mark_debug = "true" *)

(* mark_debug = "true" *) wire [31:0] debug_axi_awaddr;

(* mark_debug = "true" *) wire debug_axi_awvalid;

(* mark_debug = "true" *) wire debug_axi_awready;

// 或者通过Tcl命令在综合后网表中添加:

# set_debug_core u_ila_0 [get_nets -hierarchical {*debug_axi_*}]常见坑与排查:

- 坑5:ILA采样时钟选择错误。采样时钟必须与被测信号同步,否则波形混乱。排查:确保ILA IP的采样时钟(CLK)连接到了被测信号所在的时钟域。

- 坑6:比特流与探针文件不匹配。修改RTL或调试网络后,未重新生成并下载新的探针文件(.ltx)。排查:每次生成新比特流(.bit)后,必须同时更新并下载.ltx文件,否则硬件调试器无法识别新的调试网络。

原理与设计说明

FPGA原型验证在Chiplet流程中的核心价值在于“速度”与“真实”。其关键设计权衡如下:

- 运行速度 vs. 时序逼近:为了达到MHz级的运行速度(远超仿真),必须对原始GHz级ASIC RTL进行降频(Clock Downscaling)。这引入了关键矛盾:降频后,组合逻辑路径的相对延迟变长,更容易出现时序违例。解决方案是在关键路径插入寄存器(流水线),但这会改变设计的原始延迟特性,需要在验证测试中予以考虑和补偿。

- 接口保真度 vs. 实现复杂度:Chiplet间可能采用UCIe、BoW等先进封装级互连。在FPGA上完全模拟其电气特性和协议栈极其困难。常见的折衷是使用行为级模型(BFM)或简化后的高速串行协议(如Aurora、10G Ethernet)来模拟数据通道,而将协议验证的焦点放在事务层(TL)和数据链路层(DL)。

- 调试可见性 vs. 资源开销:插入大量ILA逻辑会显著增加资源消耗,可能影响布局布线和时序。因此需要分层调试策略:在早期集成阶段,广泛插入调试点;在性能验证阶段,则只保留最关键信号的观测能力,或采用“触发后通过PCIe回传数据”等外部调试方案。

- 单FPGA集成 vs. 多FPGA分割:当设计规模超过单颗FPGA容量时,必须进行分割。这带来了分区间通信延迟、同步和信号完整性的挑战。优先将紧密耦合的模块分在同一FPGA内;对于跨分区的高速接口,需使用FPGA间专用高速链路(如GTY)并精心设计通信协议。

验证与结果

| 指标 | 测量值 | 测量条件 | 说明 |

|---|---|---|---|

| 系统稳定运行频率 (Fmax) | 125 MHz | WNS > 0.1ns, 室温 | 原始ASIC时钟1GHz的1/8,满足原型验证需求。 |

| AXI总线实测带宽 | ~3.2 GB/s | 128位 @ 125MHz,连续读写 | 达到理论带宽(128b*125M=2GB/s*双工)的80%。 |

| 端到端事务延迟 | ~500 ns | 从CPU发起存储写到数据回读 | 包含通过AXI互联、DDR控制器及DDR颗粒本身的延迟。 |

| FPGA资源利用率 | LUT: 65% FF: 58% BRAM: 40% DSP: 10% | Xilinx VU9P器件 | 留有充足余量用于调试逻辑和后期功能扩展。 |

| ILA捕获深度 | 8192 点 | 采样时钟125MHz | 足以捕获一次完整的DDR突发传输事务。 |

故障排查 (Troubleshooting)

- 现象:上电后FPGA板卡无任何反应,LED不亮。原因:电源异常、时钟未起振、比特流下载失败。检查点:1) 测量板卡各电源电压是否正常;2) 用示波器检查晶振输出;3) 确认JTAG链识别正确。修复:检查电源配置,重新连接JTAG,尝试重新生成并下载比特流。

- 现象:设计综合实现后,时序报告出现大量违例。原因:时钟约束缺失或错误、逻辑路径过长。检查点:1) 检查约束文件中所有时钟定义;2) 查看违例路径报告,定位关键路径模块。修复:补充约束,对长组合逻辑路径进行流水线切割。

- 现象:通过PCIe与主机通信不稳定,偶发数据错误。原因:PCIe链路训练失败、DMA引擎设计缺陷、时钟域不同步。检查点:1) 查看PCIe IP核状态寄存器;2) 检查DMA描述符环和中断逻辑;3) 验证PCIe用户时钟与FPGA内部逻辑