随着芯片规模与复杂度呈指数级增长,验证已成为决定项目成败的关键环节。传统的单一验证方法学已无法应对SoC级、系统级的验证挑战。本指南旨在为验证工程师构建一个从UVM仿真验证到FPGA原型验证的完整、可落地的能力发展路径,明确各阶段的核心技能、工具链与验收标准,帮助您系统性地提升验证效率与质量,应对2026年及以后的芯片验证挑战。

Quick Start:构建验证能力基线

- 步骤1:环境准备 – 安装VCS/Xcelium或QuestaSim等主流仿真器,并配置好UVM-1.2库。

- 步骤2:创建最小UVM测试平台 – 使用一个简单的DUT(如8位计数器),编写包含agent、driver、monitor、scoreboard和sequence的UVM环境。

- 步骤3:运行首个回归测试 – 编写至少3个不同的sequence(正常、边界、错误注入),通过仿真器运行并观察覆盖率报告(代码覆盖率 > 95%)。

- 步骤4:引入形式验证 – 为同一DUT编写SVA断言,使用JasperGold或VC Formal工具运行证明,确保关键属性被形式化验证。

- 步骤5:搭建FPGA原型环境 – 选择一款评估板(如Xilinx VCU118或Intel Stratix 10),将DUT移植到FPGA,编写顶层wrapper和时钟/复位模块。

- 步骤6:实现协同验证 – 配置Vivado/Vitis HLS或Quartus,将FPGA原型通过JTAG/UART/PCIe连接到仿真环境,运行UVM测试激励并比较FPGA输出与仿真结果。

- 步骤7:性能分析与优化 – 测量FPGA原型上DUT的实际运行频率和吞吐量,与RTL仿真预估性能对比,分析差异原因。

- 步骤8:建立持续集成流程 – 使用Jenkins或GitLab CI,自动化执行从UVM仿真、形式验证到FPGA原型比特流生成与测试的全流程。

前置条件与环境

| 项目 | 推荐值/工具 | 说明 | 替代方案 |

|---|---|---|---|

| 仿真验证平台 | Synopsys VCS / Siemens EDA QuestaSim | 支持UVM-1.2,具备高性能编译与仿真能力。 | Cadence Xcelium, Aldec Riviera-PRO |

| 形式验证工具 | Cadence JasperGold / Synopsys VC Formal | 用于断言证明、属性检查,弥补动态仿真盲区。 | Siemens EDA Questa Formal |

| FPGA原型平台 | Xilinx Alveo U250 / Intel Stratix 10 GX FPGA 开发板 | 高容量、高带宽,支持复杂SoC模块映射与高速接口。 | 基于Virtex UltraScale+或Arria 10的评估板 |

| 原型开发工具 | Xilinx Vivado (2023.2+) / Intel Quartus Prime Pro (23.3+) | 综合、布局布线、时序分析与调试。 | 第三方综合工具(Synplify Pro) |

| 协同验证接口 | PCIe / 10G Ethernet / JTAG | 实现仿真环境与FPGA原型间的高速数据交换与控制。 | UART(低速控制)、Aurora(自定义高速) |

| 硬件描述语言 | SystemVerilog (IEEE 1800-2017) | 必须熟练掌握用于验证的类、约束随机、覆盖组等特性。 | VHDL (配合OSVVM或UVVM) |

| 脚本与自动化 | Python 3.8+ / Tcl / Makefile | 用于环境配置、流程控制、结果解析与报告生成。 | Perl, Shell脚本 |

| 版本控制 | Git (GitLab / GitHub) | 管理RTL、验证环境、约束文件和脚本。 | SVN |

目标与验收标准

完成本指南所述能力建设后,您应能独立或主导完成一个中等复杂度模块(如DDR控制器、图像处理流水线)的端到端验证,并达到以下可量化的验收标准:

- 功能验证完备性:UVM动态仿真功能覆盖率(covergroup)达到100%,代码行/分支/条件覆盖率不低于98%。

- 形式验证深度:所有关键接口协议和核心状态机均使用SVA描述,并通过形式工具证明,无反例(Counterexample)。

- FPGA原型有效性:成功将DUT移植到FPGA,运行频率达到目标频率(如200MHz)的80%以上,与仿真结果的功能一致性为100%。

- 协同验证效率:建立仿真-原型协同验证环境,单次测试用例在FPGA上的执行速度比纯软件仿真快100倍以上。

- 流程自动化:实现从代码提交到生成验证报告(含仿真、形式、原型结果)的全自动化CI/CD流水线。

实施步骤

阶段一:夯实UVM与高级验证方法学基础

核心是构建可重用、可扩展的验证环境。从组件级验证开始,逐步过渡到子系统级。

// 示例:一个可重用的UVC(Universal Verification Component)配置类

class bus_agent_config extends uvm_object;

`uvm_object_utils(bus_agent_config)

virtual bus_if vif; // 虚拟接口

uvm_active_passive_enum is_active = UVM_ACTIVE;

// 关键配置参数:地址宽度、数据宽度、时序模式等

int addr_width = 32;

int data_width = 32;

// 注意:虚拟接口必须在顶层通过config_db进行set

endclass常见坑与排查:

- 坑1:对象复制(copy)与比较(compare)未正确定义 – 导致scoreboard比较失败或覆盖率合并错误。排查:确保所有自定义uvm_object/uvm_component子类都正确定义了`do_copy`和`do_compare`方法。

- 坑2:phase跳转或死锁 – 仿真卡在某个phase无法前进。排查:检查`run_phase`中是否有无限循环而未调用`phase.raise_objection`/`drop_objection`,或组件间objection控制不当。

阶段二:集成形式验证与断言

将SVA断言嵌入RTL或绑定到接口,用于描述时序行为和不变式,并使用形式工具进行穷尽证明。

// 示例:描述一个简单握手机制的SVA属性

property p_valid_handshake;

@(posedge clk) disable iff (!rst_n)

(valid && !ready) |=> (valid throughout ready[->1]); // valid拉高后,必须保持到ready拉高

endproperty

assert_valid_handshake: assert property (p_valid_handshake)

else `uvm_error("ASSERT", "Handshake protocol violation")常见坑与排查:

- 坑1:断言过于复杂,导致证明时间爆炸 – 形式验证无法在合理时间内完成。排查:将复杂断言分解为多个简单的属性;为证明引擎设置合理的边界(depth, width)。

- 坑2:忽略复位条件 – 断言在复位期间误报。排查:所有属性必须使用`disable iff`语句包含复位条件。

阶段三:FPGA原型设计与移植

重点处理时钟域、存储器模型、IP核替换和I/O约束。

# 示例:Vivado中关键时序约束 (XDC)

# 主时钟定义

create_clock -name clk_core -period 5.0 [get_ports sys_clk_p]

# 生成时钟定义(如PLL输出)

create_generated_clock -name clk_200m -source [get_pins pll_inst/CLKIN] -divide_by 1 -multiply_by 4 [get_pins pll_inst/CLKOUT0]

# 输入延迟(约束来自外部芯片的数据)

set_input_delay -clock [get_clocks clk_200m] -max 2.0 [get_ports data_in*]

# 关键路径例外(如跨时钟域路径)

set_false_path -from [get_clocks clk_a] -to [get_clocks clk_b]常见坑与排查:

- 坑1:异步时钟域处理不当导致亚稳态 – FPGA原型运行不稳定。排查:所有跨时钟域信号必须使用同步器(两级或多级寄存器同步)。使用工具(如Vivado的CDC报告)检查未同步的跨时钟域路径。

- 坑2:片上存储器初始化与行为不一致 – RTL仿真通过,FPGA行为异常。排查:将RTL中的行为级`$readmemh`替换为FPGA工具可识别的初始化文件(.coe for Xilinx, .mif for Intel),或在上电复位逻辑中显式初始化BRAM。

阶段四:建立仿真-原型协同验证链路

利用PCIe或以太网等高速接口,将UVM测试平台的激励发送到FPGA,并将结果回传进行比较。

常见坑与排查:

- 坑1:数据传输速率不匹配 – 协同验证成为瓶颈。排查:在软件端使用DMA或零拷贝技术;在FPGA端使用足够深的FIFO缓冲数据;优化通信协议,减少握手开销。

- 坑2:调试可见性差 – FPGA内部信号难以观测。排查:集成在线逻辑分析仪(如Xilinx ILA, Intel Signal Tap),通过JTAG实时抓取信号波形;在设计中插入可控制的调试输出端口。

原理与设计说明

构建此能力模型的核心矛盾在于验证完备性、效率与成本之间的平衡。

- 向系统级验证扩展:引入基于C

- 现象:UVM仿真随机失败,错误不重现。原因:约束随机生成器种子未固定或线程同步问题。检查点:检查`uvm_root`的随机数种子设置;检查`fork...join`、`fork...join_none`的使用是否正确。修复:使用`+uvm_set_seed`命令行参数固定种子;使用`uvm_barrier`或`event`进行线程同步。

- 现象:形式验证报告“Inconclusive”。原因:证明深度不足或设计中有黑盒(未建模的IP)。检查点:查看证明引擎的波形或日志,看是否在边界处停止。修复:增加证明深度;为黑盒IP添加抽象模型(assume/约束)。

- 现象:FPGA综合后网表功能与RTL仿真不符。原因:RTL中存在不可综合的语句或仿真与综合理解不一致(如初始化值)。检查点:检查是否有`initial`块(FPGA上电状态不确定)、`#delay`、系统任务(`$display`)。修复:使用复位信号来初始化寄存器;移除所有不可综合的代码。

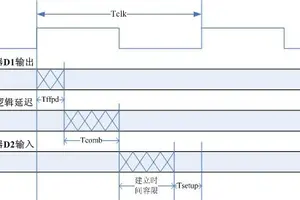

- 现象:FPGA时序报告出现建立/保持时间违例。原因:关键路径延迟过长或时钟约束不正确。检查点:查看违例路径的起点和终点;检查时钟定义和生成的时钟关系。修复:优化逻辑(流水线、重定时);添加适当的输入/输出延迟约束;使用`set_max_delay`对特定路径进行约束。

- 现象:协同验证数据传输错误或丢失。原因:FPGA端FIFO溢出/读空,或软件/硬件端序不一致。检查点:检查FIFO的满/空标志;对比发送和接收数据的原始字节。修复:增大FIFO深度;在通信协议中加入序列号或CRC校验;统一字节序(大端/小端)。

- 现象:ILA抓不到预期信号。原因:触发条件设置不当,或信号在综合优化中被移除。检查点:确认ILA核的时钟域和触发逻辑;检查综合网表中该信号是否存在。修复:调整触发条件(边沿、电平、组合逻辑);使用`(* keep = "true" *)`或`(* mark_debug = "true" *)`等属性保留调试信号。

- 现象:CI流水线中某一步骤(如形式验证)超时失败。原因:资源不足或任务本身耗时过长。检查点:查看服务器资源监控(CPU、内存);分析该步骤的详细日志。修复:为耗时任务设置独立的超时阈值并分配更多资源;考虑将大型证明任务拆分为多个并行的小任务。

- 现象:覆盖率合并后数据异常(如覆盖率下降)。原因:来自不同仿真运行或不同测试的覆盖率数据库版本/格式不兼容。检查点:检查用于合并的`urg`或`imc`命令参数,确保输入文件列表正确。修复:统一使用相同版本的仿真工具生成覆盖率数据;在合并前确保各次仿真的设计版本一致。

- UVM vs. 形式验证:UVM擅长于功能场景的探索和伪随机测试,但无法穷尽所有状态。形式验证则能对特定属性进行数学证明,弥补仿真盲区。二者结合(动态+静态)是提升验证置信度的必然选择。

- 软件仿真 vs. FPGA原型:软件仿真速度慢(kHz-MHz级),但调试 visibility 极佳。FPGA原型速度快(10s-100s MHz),更接近真实芯片行为,尤其适合验证性能、功耗和软硬件协同,但调试复杂。协同验证将二者优势结合,用仿真做控制和检查,用原型做高速执行。

- 向系统级验证扩展:引入基于C

- 现象:UVM仿真随机失败,错误不重现。原因:约束随机生成器种子未固定或线程同步问题。检查点:检查`uvm_root`的随机数种子设置;检查`fork...join`、`fork...join_none`的使用是否正确。修复:使用`+uvm_set_seed`命令行参数固定种子;使用`uvm_barrier`或`event`进行线程同步。

- 现象:形式验证报告“Inconclusive”。原因:证明深度不足或设计中有黑盒(未建模的IP)。检查点:查看证明引擎的波形或日志,看是否在边界处停止。修复:增加证明深度;为黑盒IP添加抽象模型(assume/约束)。

- 现象:FPGA综合后网表功能与RTL仿真不符。原因:RTL中存在不可综合的语句或仿真与综合理解不一致(如初始化值)。检查点:检查是否有`initial`块(FPGA上电状态不确定)、`#delay`、系统任务(`$display`)。修复:使用复位信号来初始化寄存器;移除所有不可综合的代码。

- 现象:FPGA时序报告出现建立/保持时间违例。原因:关键路径延迟过长或时钟约束不正确。检查点:查看违例路径的起点和终点;检查时钟定义和生成的时钟关系。修复:优化逻辑(流水线、重定时);添加适当的输入/输出延迟约束;使用`set_max_delay`对特定路径进行约束。

- 现象:协同验证数据传输错误或丢失。原因:FPGA端FIFO溢出/读空,或软件/硬件端序不一致。检查点:检查FIFO的满/空标志;对比发送和接收数据的原始字节。修复:增大FIFO深度;在通信协议中加入序列号或CRC校验;统一字节序(大端/小端)。

- 现象:ILA抓不到预期信号。原因:触发条件设置不当,或信号在综合优化中被移除。检查点:确认ILA核的时钟域和触发逻辑;检查综合网表中该信号是否存在。修复:调整触发条件(边沿、电平、组合逻辑);使用`(* keep = "true" *)`或`(* mark_debug = "true" *)`等属性保留调试信号。

- 现象:CI流水线中某一步骤(如形式验证)超时失败。原因:资源不足或任务本身耗时过长。检查点:查看服务器资源监控(CPU、内存);分析该步骤的详细日志。修复:为耗时任务设置独立的超时阈值并分配更多资源;考虑将大型证明任务拆分为多个并行的小任务。

- 现象:覆盖率合并后数据异常(如覆盖率下降)。原因:来自不同仿真运行或不同测试的覆盖率数据库版本/格式不兼容。检查点:检查用于合并的`urg`或`imc`命令参数,确保输入文件列表正确。修复:统一使用相同版本的仿真工具生成覆盖率数据;在合并前确保各次仿真的设计版本一致。

- 向系统级验证扩展:引入基于C

- 现象:UVM仿真随机失败,错误不重现。原因:约束随机生成器种子未固定或线程同步问题。检查点:检查`uvm_root`的随机数种子设置;检查`fork...join`、`fork...join_none`的使用是否正确。修复:使用`+uvm_set_seed`命令行参数固定种子;使用`uvm_barrier`或`event`进行线程同步。

- 现象:形式验证报告“Inconclusive”。原因:证明深度不足或设计中有黑盒(未建模的IP)。检查点:查看证明引擎的波形或日志,看是否在边界处停止。修复:增加证明深度;为黑盒IP添加抽象模型(assume/约束)。

- 现象:FPGA综合后网表功能与RTL仿真不符。原因:RTL中存在不可综合的语句或仿真与综合理解不一致(如初始化值)。检查点:检查是否有`initial`块(FPGA上电状态不确定)、`#delay`、系统任务(`$display`)。修复:使用复位信号来初始化寄存器;移除所有不可综合的代码。

- 现象:FPGA时序报告出现建立/保持时间违例。原因:关键路径延迟过长或时钟约束不正确。检查点:查看违例路径的起点和终点;检查时钟定义和生成的时钟关系。修复:优化逻辑(流水线、重定时);添加适当的输入/输出延迟约束;使用`set_max_delay`对特定路径进行约束。

- 现象:协同验证数据传输错误或丢失。原因:FPGA端FIFO溢出/读空,或软件/硬件端序不一致。检查点:检查FIFO的满/空标志;对比发送和接收数据的原始字节。修复:增大FIFO深度;在通信协议中加入序列号或CRC校验;统一字节序(大端/小端)。

- 现象:ILA抓不到预期信号。原因:触发条件设置不当,或信号在综合优化中被移除。检查点:确认ILA核的时钟域和触发逻辑;检查综合网表中该信号是否存在。修复:调整触发条件(边沿、电平、组合逻辑);使用`(* keep = "true" *)`或`(* mark_debug = "true" *)`等属性保留调试信号。

- 现象:CI流水线中某一步骤(如形式验证)超时失败。原因:资源不足或任务本身耗时过长。检查点:查看服务器资源监控(CPU、内存);分析该步骤的详细日志。修复:为耗时任务设置独立的超时阈值并分配更多资源;考虑将大型证明任务拆分为多个并行的小任务。

- 现象:覆盖率合并后数据异常(如覆盖率下降)。原因:来自不同仿真运行或不同测试的覆盖率数据库版本/格式不兼容。检查点:检查用于合并的`urg`或`imc`命令参数,确保输入文件列表正确。修复:统一使用相同版本的仿真工具生成覆盖率数据;在合并前确保各次仿真的设计版本一致。

- UVM vs. 形式验证:UVM擅长于功能场景的探索和伪随机测试,但无法穷尽所有状态。形式验证则能对特定属性进行数学证明,弥补仿真盲区。二者结合(动态+静态)是提升验证置信度的必然选择。

- 软件仿真 vs. FPGA原型:软件仿真速度慢(kHz-MHz级),但调试 visibility 极佳。FPGA原型速度快(10s-100s MHz),更接近真实芯片行为,尤其适合验证性能、功耗和软硬件协同,但调试复杂。协同验证将二者优势结合,用仿真做控制和检查,用原型做高速执行。

- 向系统级验证扩展:引入基于C

- 现象:UVM仿真随机失败,错误不重现。原因:约束随机生成器种子未固定或线程同步问题。检查点:检查`uvm_root`的随机数种子设置;检查`fork...join`、`fork...join_none`的使用是否正确。修复:使用`+uvm_set_seed`命令行参数固定种子;使用`uvm_barrier`或`event`进行线程同步。

- 现象:形式验证报告“Inconclusive”。原因:证明深度不足或设计中有黑盒(未建模的IP)。检查点:查看证明引擎的波形或日志,看是否在边界处停止。修复:增加证明深度;为黑盒IP添加抽象模型(assume/约束)。

- 现象:FPGA综合后网表功能与RTL仿真不符。原因:RTL中存在不可综合的语句或仿真与综合理解不一致(如初始化值)。检查点:检查是否有`initial`块(FPGA上电状态不确定)、`#delay`、系统任务(`$display`)。修复:使用复位信号来初始化寄存器;移除所有不可综合的代码。

- 现象:FPGA时序报告出现建立/保持时间违例。原因:关键路径延迟过长或时钟约束不正确。检查点:查看违例路径的起点和终点;检查时钟定义和生成的时钟关系。修复:优化逻辑(流水线、重定时);添加适当的输入/输出延迟约束;使用`set_max_delay`对特定路径进行约束。

- 现象:协同验证数据传输错误或丢失。原因:FPGA端FIFO溢出/读空,或软件/硬件端序不一致。检查点:检查FIFO的满/空标志;对比发送和接收数据的原始字节。修复:增大FIFO深度;在通信协议中加入序列号或CRC校验;统一字节序(大端/小端)。

- 现象:ILA抓不到预期信号。原因:触发条件设置不当,或信号在综合优化中被移除。检查点:确认ILA核的时钟域和触发逻辑;检查综合网表中该信号是否存在。修复:调整触发条件(边沿、电平、组合逻辑);使用`(* keep = "true" *)`或`(* mark_debug = "true" *)`等属性保留调试信号。

- 现象:CI流水线中某一步骤(如形式验证)超时失败。原因:资源不足或任务本身耗时过长。检查点:查看服务器资源监控(CPU、内存);分析该步骤的详细日志。修复:为耗时任务设置独立的超时阈值并分配更多资源;考虑将大型证明任务拆分为多个并行的小任务。

- 现象:覆盖率合并后数据异常(如覆盖率下降)。原因:来自不同仿真运行或不同测试的覆盖率数据库版本/格式不兼容。检查点:检查用于合并的`urg`或`imc`命令参数,确保输入文件列表正确。修复:统一使用相同版本的仿真工具生成覆盖率数据;在合并前确保各次仿真的设计版本一致。

- 现象:UVM仿真随机失败,错误不重现。原因:约束随机生成器种子未固定或线程同步问题。检查点:检查`uvm_root`的随机数种子设置;检查`fork...join`、`fork...join_none`的使用是否正确。修复:使用`+uvm_set_seed`命令行参数固定种子;使用`uvm_barrier`或`event`进行线程同步。

- 现象:形式验证报告“Inconclusive”。原因:证明深度不足或设计中有黑盒(未建模的IP)。检查点:查看证明引擎的波形或日志,看是否在边界处停止。修复:增加证明深度;为黑盒IP添加抽象模型(assume/约束)。

- 现象:FPGA综合后网表功能与RTL仿真不符。原因:RTL中存在不可综合的语句或仿真与综合理解不一致(如初始化值)。检查点:检查是否有`initial`块(FPGA上电状态不确定)、`#delay`、系统任务(`$display`)。修复:使用复位信号来初始化寄存器;移除所有不可综合的代码。

- 现象:FPGA时序报告出现建立/保持时间违例。原因:关键路径延迟过长或时钟约束不正确。检查点:查看违例路径的起点和终点;检查时钟定义和生成的时钟关系。修复:优化逻辑(流水线、重定时);添加适当的输入/输出延迟约束;使用`set_max_delay`对特定路径进行约束。

- 现象:协同验证数据传输错误或丢失。原因:FPGA端FIFO溢出/读空,或软件/硬件端序不一致。检查点:检查FIFO的满/空标志;对比发送和接收数据的原始字节。修复:增大FIFO深度;在通信协议中加入序列号或CRC校验;统一字节序(大端/小端)。

- 现象:ILA抓不到预期信号。原因:触发条件设置不当,或信号在综合优化中被移除。检查点:确认ILA核的时钟域和触发逻辑;检查综合网表中该信号是否存在。修复:调整触发条件(边沿、电平、组合逻辑);使用`(* keep = "true" *)`或`(* mark_debug = "true" *)`等属性保留调试信号。

- 现象:CI流水线中某一步骤(如形式验证)超时失败。原因:资源不足或任务本身耗时过长。检查点:查看服务器资源监控(CPU、内存);分析该步骤的详细日志。修复:为耗时任务设置独立的超时阈值并分配更多资源;考虑将大型证明任务拆分为多个并行的小任务。

- 现象:覆盖率合并后数据异常(如覆盖率下降)。原因:来自不同仿真运行或不同测试的覆盖率数据库版本/格式不兼容。检查点:检查用于合并的`urg`或`imc`命令参数,确保输入文件列表正确。修复:统一使用相同版本的仿真工具生成覆盖率数据;在合并前确保各次仿真的设计版本一致。

- UVM vs. 形式验证:UVM擅长于功能场景的探索和伪随机测试,但无法穷尽所有状态。形式验证则能对特定属性进行数学证明,弥补仿真盲区。二者结合(动态+静态)是提升验证置信度的必然选择。

- 软件仿真 vs. FPGA原型:软件仿真速度慢(kHz-MHz级),但调试 visibility 极佳。FPGA原型速度快(10s-100s MHz),更接近真实芯片行为,尤其适合验证性能、功耗和软硬件协同,但调试复杂。协同验证将二者优势结合,用仿真做控制和检查,用原型做高速执行。

- 向系统级验证扩展:引入基于C

- 现象:UVM仿真随机失败,错误不重现。原因:约束随机生成器种子未固定或线程同步问题。检查点:检查`uvm_root`的随机数种子设置;检查`fork...join`、`fork...join_none`的使用是否正确。修复:使用`+uvm_set_seed`命令行参数固定种子;使用`uvm_barrier`或`event`进行线程同步。

- 现象:形式验证报告“Inconclusive”。原因:证明深度不足或设计中有黑盒(未建模的IP)。检查点:查看证明引擎的波形或日志,看是否在边界处停止。修复:增加证明深度;为黑盒IP添加抽象模型(assume/约束)。

- 现象:FPGA综合后网表功能与RTL仿真不符。原因:RTL中存在不可综合的语句或仿真与综合理解不一致(如初始化值)。检查点:检查是否有`initial`块(FPGA上电状态不确定)、`#delay`、系统任务(`$display`)。修复:使用复位信号来初始化寄存器;移除所有不可综合的代码。

- 现象:FPGA时序报告出现建立/保持时间违例。原因:关键路径延迟过长或时钟约束不正确。检查点:查看违例路径的起点和终点;检查时钟定义和生成的时钟关系。修复:优化逻辑(流水线、重定时);添加适当的输入/输出延迟约束;使用`set_max_delay`对特定路径进行约束。

- 现象:协同验证数据传输错误或丢失。原因:FPGA端FIFO溢出/读空,或软件/硬件端序不一致。检查点:检查FIFO的满/空标志;对比发送和接收数据的原始字节。修复:增大FIFO深度;在通信协议中加入序列号或CRC校验;统一字节序(大端/小端)。

- 现象:ILA抓不到预期信号。原因:触发条件设置不当,或信号在综合优化中被移除。检查点:确认ILA核的时钟域和触发逻辑;检查综合网表中该信号是否存在。修复:调整触发条件(边沿、电平、组合逻辑);使用`(* keep = "true" *)`或`(* mark_debug = "true" *)`等属性保留调试信号。

- 现象:CI流水线中某一步骤(如形式验证)超时失败。原因:资源不足或任务本身耗时过长。检查点:查看服务器资源监控(CPU、内存);分析该步骤的详细日志。修复:为耗时任务设置独立的超时阈值并分配更多资源;考虑将大型证明任务拆分为多个并行的小任务。

- 现象:覆盖率合并后数据异常(如覆盖率下降)。原因:来自不同仿真运行或不同测试的覆盖率数据库版本/格式不兼容。检查点:检查用于合并的`urg`或`imc`命令参数,确保输入文件列表正确。修复:统一使用相同版本的仿真工具生成覆盖率数据;在合并前确保各次仿真的设计版本一致。

- UVM vs. 形式验证:UVM擅长于功能场景的探索和伪随机测试,但无法穷尽所有状态。形式验证则能对特定属性进行数学证明,弥补仿真盲区。二者结合(动态+静态)是提升验证置信度的必然选择。

- 软件仿真 vs. FPGA原型:软件仿真速度慢(kHz-MHz级),但调试 visibility 极佳。FPGA原型速度快(10s-100s MHz),更接近真实芯片行为,尤其适合验证性能、功耗和软硬件协同,但调试复杂。协同验证将二者优势结合,用仿真做控制和检查,用原型做高速执行。

- 现象:UVM仿真随机失败,错误不重现。原因:约束随机生成器种子未固定或线程同步问题。检查点:检查`uvm_root`的随机数种子设置;检查`fork...join`、`fork...join_none`的使用是否正确。修复:使用`+uvm_set_seed`命令行参数固定种子;使用`uvm_barrier`或`event`进行线程同步。

- 现象:形式验证报告“Inconclusive”。原因:证明深度不足或设计中有黑盒(未建模的IP)。检查点:查看证明引擎的波形或日志,看是否在边界处停止。修复:增加证明深度;为黑盒IP添加抽象模型(assume/约束)。

- 现象:FPGA综合后网表功能与RTL仿真不符。原因:RTL中存在不可综合的语句或仿真与综合理解不一致(如初始化值)。检查点:检查是否有`initial`块(FPGA上电状态不确定)、`#delay`、系统任务(`$display`)。修复:使用复位信号来初始化寄存器;移除所有不可综合的代码。

- 现象:FPGA时序报告出现建立/保持时间违例。原因:关键路径延迟过长或时钟约束不正确。检查点:查看违例路径的起点和终点;检查时钟定义和生成的时钟关系。修复:优化逻辑(流水线、重定时);添加适当的输入/输出延迟约束;使用`set_max_delay`对特定路径进行约束。

- 现象:协同验证数据传输错误或丢失。原因:FPGA端FIFO溢出/读空,或软件/硬件端序不一致。检查点:检查FIFO的满/空标志;对比发送和接收数据的原始字节。修复:增大FIFO深度;在通信协议中加入序列号或CRC校验;统一字节序(大端/小端)。

- 现象:ILA抓不到预期信号。原因:触发条件设置不当,或信号在综合优化中被移除。检查点:确认ILA核的时钟域和触发逻辑;检查综合网表中该信号是否存在。修复:调整触发条件(边沿、电平、组合逻辑);使用`(* keep = "true" *)`或`(* mark_debug = "true" *)`等属性保留调试信号。

- 现象:CI流水线中某一步骤(如形式验证)超时失败。原因:资源不足或任务本身耗时过长。检查点:查看服务器资源监控(CPU、内存);分析该步骤的详细日志。修复:为耗时任务设置独立的超时阈值并分配更多资源;考虑将大型证明任务拆分为多个并行的小任务。

- 现象:覆盖率合并后数据异常(如覆盖率下降)。原因:来自不同仿真运行或不同测试的覆盖率数据库版本/格式不兼容。检查点:检查用于合并的`urg`或`imc`命令参数,确保输入文件列表正确。修复:统一使用相同版本的仿真工具生成覆盖率数据;在合并前确保各次仿真的设计版本一致。

扩展与下一步

验证与结果

| 验证阶段 | 关键指标 | 测量条件/工具 | 典型结果(示例) |

|---|---|---|---|

| UVM动态仿真 | 功能覆盖率 | 运行5000个随机种子,收集covergroup数据 | 100% (覆盖所有定义的功能点) |

| 代码覆盖率 | 仿真器内置覆盖率收集 | 行覆盖率: 99.5%, 分支覆盖率: 98.2% | |

| 形式验证 | 断言证明率 | JasperGold, 证明深度=50 | 25条关键断言, 100% Proven, 0 Violated |

| FPGA原型 | 最大运行频率 (Fmax) | Vivado Timing Report (Post-Place & Route) | 225 MHz (目标200MHz, 裕量12.5%) |

| 资源利用率 | Vivado Utilization Report | LUT: 15%, FF: 12%, BRAM: 8%, DSP: 20% | |

| 协同验证 | 测试加速比 | 对比同一测试向量在仿真和FPGA上的执行时间 | FPGA执行速度是仿真的 ~500倍 |

| 结果一致性 | 比较仿真输出与FPGA回传数据 | 10万次事务, 输出匹配率100% |

故障排查 (Troubleshooting)

扩展与下一步

扩展与下一步

验证与结果

| 验证阶段 | 关键指标 | 测量条件/工具 | 典型结果(示例) |

|---|---|---|---|

| UVM动态仿真 | 功能覆盖率 | 运行5000个随机种子,收集covergroup数据 | 100% (覆盖所有定义的功能点) |

| 代码覆盖率 | 仿真器内置覆盖率收集 | 行覆盖率: 99.5%, 分支覆盖率: 98.2% | |

| 形式验证 | 断言证明率 | JasperGold, 证明深度=50 | 25条关键断言, 100% Proven, 0 Violated |

| FPGA原型 | 最大运行频率 (Fmax) | Vivado Timing Report (Post-Place & Route) | 225 MHz (目标200MHz, 裕量12.5%) |

| 资源利用率 | Vivado Utilization Report | LUT: 15%, FF: 12%, BRAM: 8%, DSP: 20% | |

| 协同验证 | 测试加速比 | 对比同一测试向量在仿真和FPGA上的执行时间 | FPGA执行速度是仿真的 ~500倍 |

| 结果一致性 | 比较仿真输出与FPGA回传数据 | 10万次事务, 输出匹配率100% |

故障排查 (Troubleshooting)

扩展与下一步

扩展与下一步

验证与结果

| 验证阶段 | 关键指标 | 测量条件/工具 | 典型结果(示例) |

|---|---|---|---|

| UVM动态仿真 | 功能覆盖率 | 运行5000个随机种子,收集covergroup数据 | 100% (覆盖所有定义的功能点) |

| 代码覆盖率 | 仿真器内置覆盖率收集 | 行覆盖率: 99.5%, 分支覆盖率: 98.2% | |

| 形式验证 | 断言证明率 | JasperGold, 证明深度=50 | 25条关键断言, 100% Proven, 0 Violated |

| FPGA原型 | 最大运行频率 (Fmax) | Vivado Timing Report (Post-Place & Route) | 225 MHz (目标200MHz, 裕量12.5%) |

| 资源利用率 | Vivado Utilization Report | LUT: 15%, FF: 12%, BRAM: 8%, DSP: 20% | |

| 协同验证 | 测试加速比 | 对比同一测试向量在仿真和FPGA上的执行时间 | FPGA执行速度是仿真的 ~500倍 |

| 结果一致性 | 比较仿真输出与FPGA回传数据 | 10万次事务, 输出匹配率100% |

故障排查 (Troubleshooting)

扩展与下一步

验证与结果

| 验证阶段 | 关键指标 | 测量条件/工具 | 典型结果(示例) |

|---|---|---|---|

| UVM动态仿真 | 功能覆盖率 | 运行5000个随机种子,收集covergroup数据 | 100% (覆盖所有定义的功能点) |

| 代码覆盖率 | 仿真器内置覆盖率收集 | 行覆盖率: 99.5%, 分支覆盖率: 98.2% | |

| 形式验证 | 断言证明率 | JasperGold, 证明深度=50 | 25条关键断言, 100% Proven, 0 Violated |

| FPGA原型 | 最大运行频率 (Fmax) | Vivado Timing Report (Post-Place & Route) | 225 MHz (目标200MHz, 裕量12.5%) |

| 资源利用率 | Vivado Utilization Report | LUT: 15%, FF: 12%, BRAM: 8%, DSP: 20% | |

| 协同验证 | 测试加速比 | 对比同一测试向量在仿真和FPGA上的执行时间 | FPGA执行速度是仿真的 ~500倍 |

| 结果一致性 | 比较仿真输出与FPGA回传数据 | 10万次事务, 输出匹配率100% |