随着AIoT边缘智能设备对能效比要求的急剧提升,RISC-V向量扩展(RVV)指令集凭借其可伸缩的并行计算能力,成为AI加速协处理器的理想选择。然而,将RVV规范从纸面转化为可综合、可验证的硬件设计,并在FPGA原型平台上完成功能与性能的闭环验证,是芯片流片前降低风险的关键环节。本文旨在提供一套从RTL设计到FPGA上板验证的完整、可执行流程,帮助设计团队快速构建RVV原型验证环境,并识别早期设计缺陷。

Quick Start

- 步骤一:获取或搭建一个支持RVV 1.0标准的RISC-V处理器核(如CVA6、SweRV EH2 with V扩展),或使用商业IP。

- 步骤二:准备FPGA开发板(如Xilinx ZCU106或Intel Stratix 10 MX),安装对应Vivado(2023.2+)或Quartus Prime(23.1+)工具链。

- 步骤三:创建工程,导入处理器核、向量处理单元(VPU)RTL、总线互联(如AXI)及外设(DDR控制器、UART)代码。

- 步骤四:编写顶层测试平台(Testbench),连接虚拟UART或JTAG模型,用于加载测试程序。

- 步骤五:使用RISC-V GNU工具链(支持RVV扩展)编译一个简单的向量加法(vadd.vv)测试程序,生成.elf或.bin文件。

- 步骤六:在仿真器(如Verilator、VCS)中运行仿真,通过虚拟UART打印“PASS”或检查内存结果,确认指令执行正确。

- 步骤七:为FPGA平台编写物理约束文件(.xdc或.sdc),包括时钟、复位、DDR接口引脚、UART引脚等。

- 步骤八:运行综合与实现,生成比特流(.bit)。确保时序收敛,无严重拥塞。

- 步骤九:将比特流下载至FPGA板卡,通过板载UART-USB连接PC终端(如Putty)。

- 步骤十:通过JTAG或预置Bootloader将测试程序加载到DDR中,复位CPU,在终端观察到“Vector Test PASSED”打印信息,即表示最小系统验证通过。

- “The RISC-V Instruction Set Manual, Volume I: Unprivileged ISA”, Chapter 16 “Vector Extension”, Version 1.0. 官方规范。

- CVA6 (Ariane) 开源处理器项目, GitHub仓库中的RVV开发分支。

验证与结果

<!-- /wp:headin

前置条件与环境

<!-- /wp:headin

验证与结果

<!-- /wp:headin前置条件与环境

<!-- /wp:headin项目推荐值/配置说明与替代方案FPGA平台Xilinx ZCU106 (Zynq UltraScale+) 或 Intel DE10-Agilex需具备足够逻辑资源(>300K LUT)与DDR4接口。替代:VCU118、Arria 10 SoC DK。EDA工具Vivado 2023.2 / Quartus Prime 23.1需支持SystemVerilog-2012。Vivado HLS可用于加速器模块原型。RISC-V处理器核CVA6 (Ariane) with RVV 1.0 patch 或 SweRV EH2 + 自定义VPU必须支持目标RVV配置(如VLEN=128/256, ELEN=32)。商业IP可选Codasip、Andes。仿真环境Verilator 5.0+ 配合GTKWave,或商用VCS/Xcelium用于前仿真。需支持多线程以加速向量长序列仿真。软件工具链RISC-V GNU Toolchain (rvv-1.0分支) 或 LLVM用于编译C/内联汇编测试程序。确保-march=rv64gcv参数正确。验证IP/模型DDR4 Controller Model, UART VIP, 或简易Bus Functional Model (BFM)用于仿真时代替物理外设。可使用Verilator的DPI-C编写简单内存模型。物理约束时钟:100MHz系统时钟,200MHz DDR参考时钟根据板卡原理图定义。复位需为低有效,异步复位同步释放。总线互联AXI4 (64-bit/128-bit) 用于主存,AXI4-Lite用于外设确保VPU的访存带宽与延迟满足向量加载/存储需求。

目标与验收标准

完成本流程后,应实现一个在FPGA上可运行的RVV原型系统,并通过以下验收:

功能正确性:运行RVV合规性测试套件(如riscv-arch-test的V扩展部分)或自定义向量算法(如矩阵乘、卷积),结果与Golden C模型匹配。

性能可观测:通过性能计数器或软件时间戳,测量关键向量内核(如vfmacc.vv)的CPI(Cycles Per Instruction)或MFLOPS,并与理论峰值对比。

时序收敛:FPGA实现后,关键路径(通常位于VPU的向量寄存器文件旁路或ALU流水线)满足目标频率(如100MHz),建立/保持时间无违例。

资源占用可控:VPU模块在目标FPGA上的逻辑资源(LUT/FF)与BRAM占用符合预期,通常向量寄存器文件是主要资源消耗者。

系统稳定性:连续运行压力测试(如长时间向量随机运算)无死机、数据损坏,中断与异常处理正确。

实施步骤

阶段一:工程结构与环境搭建

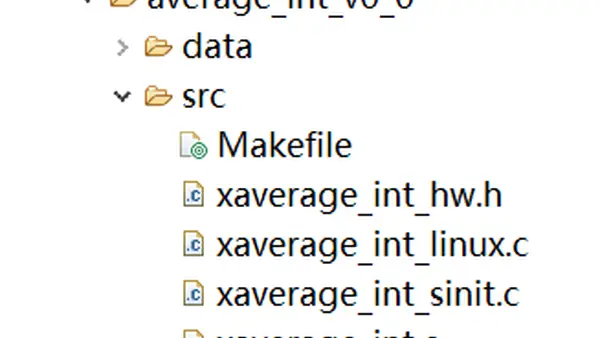

创建清晰的目录结构:rtl/(核心RTL)、tb/(测试平台)、sw/(测试程序)、constraints/(约束文件)、scripts/(构建与仿真脚本)。使用Makefile或Python脚本自动化流程。

常见坑与排查:

坑1:工具链不匹配导致非法指令。检查编译时-march和-mabi是否与硬件设计(如XLEN、VLEN)一致。使用objdump -d反汇编确认生成的指令编码正确。

坑2:仿真内存模型行为与真实DDR不一致。简易内存模型可能无延迟,导致仿真通过但上板失败。建议使用带可配置延迟的BFM或集成FPGA厂商的DDR仿真模型。

阶段二:关键模块集成与验证

重点集成向量处理单元(VPU)。VPU通常包含向量寄存器文件(VRF)、多个并行流水线(ALU、LSU、乘加单元)和状态寄存器(vtype, vl, vstart)。确保标量核与VPU间的指令派发、异常同步正确。

// 示例:一个简化的向量ALU控制信号生成片段(SystemVerilog)

always_comb begin

case (vfu_op_i)

VADD: vresult = va + vb;

VAND: vresult = va & vb;

VMUL: vresult = va * vb; // 可能为多周期流水

default: vresult = '0;

endcase

end

// 注意:需处理元素掩码(vm)和尾数(tail)与扰动(agnostic)策略。

常见坑与排查:

坑3:向量长度(vl)变化时流水线数据 hazard。当vl在下一条指令中变小时,原长向量操作的未完成部分可能错误写回。解决方案:引入vl变化冲刷流水线,或使用基于vstart的精确异常处理。

坑4:VRF多端口读写冲突。RVV支持多个源向量和一个目的向量同时操作。确保VRF读写端口数足够(如4读2写),或通过时钟周期分时复用并妥善处理RAW冲突。

阶段三:时序约束与物理实现

为FPGA综合与实现编写约束。关键约束包括主时钟、生成时钟(如DDR PHY)、VPU内部跨时钟域(如果有)、I/O延迟。

# 示例:Vivado XDC 关键约束片段

create_clock -period 10.000 -name sys_clk [get_ports sys_clk_p]

# 对大型向量寄存器文件,可放宽局部路径约束以改善布局

set_max_delay -from [get_cells vrf/ram_reg*] -to [get_cells vrf/ram_reg*] 2.000

# 对从DDR到VPU的数据路径设置输入延迟

set_input_delay -clock [get_clocks ddr_clk] -max 1.500 [get_ports vpu_ddr_data_i*]

阶段四:上板验证与调试

利用FPGA的调试功能:集成ILA(Vivado)或SignalTap(Quartus)抓取VPU关键信号(如vstart, vl, vd写使能)。通过UART打印调试信息(如异常PC、vl值)。

原理与设计说明

RVV在AIoT芯片中的FPGA原型验证,核心矛盾在于硬件设计的灵活性与验证场景的复杂性之间的权衡。

1. 可配置性与资源消耗:RVV标准允许VLEN(向量寄存器长度)和ELEN(元素长度)参数化。在FPGA上,VLEN=256相比VLEN=128,VRF的BRAM消耗可能翻倍,但能提供更高的数据级并行。AIoT场景通常选择VLEN=128/256作为平衡点。设计时应使用参数化RTL,便于快速评估不同配置。

2. 访存带宽与延迟容忍:向量指令的吞吐常受限于内存带宽。FPGA原型上,通过宽位AXI总线(如128位)和DDR Burst传输来模拟ASIC的高带宽。设计VPU的加载/存储单元时,应采用深度预取缓冲(Prefetch Buffer)以隐藏DDR延迟,这与AIoT芯片中采用紧密耦合存储器(TCM)的策略不同,是原型验证时需要特别注意的差异点。

3. 验证完备性与效率:RVV指令组合繁多(掩码、尾数、扰动策略)。在FPGA上全量回归不现实。策略是:在仿真阶段使用受限随机测试结合RVV合规套件进行充分验证;在FPGA上则运行代表性的AI内核(如int8卷积、fp16矩阵乘)进行压力与性能测试。这构成了从形式到场景的混合验证路径。

验证与结果

<!-- /wp:headin

测试项目条件与配置测量结果验收点RVV基础指令(vadd, vmul)VLEN=128, ELEN=32, vl=16, 仿真波形显示vd结果与软件模型完全一致功能正确向量乘加(vfmacc.vv)性能FPGA @100MHz, 矩阵大小32x32, 使用循环展开执行周期:~5200 cycles, 计算吞吐:~39 MFLOPS性能与理论值(~64 MFLOPS)在可接受偏差内,瓶颈分析为DDR访存FPGA资源占用Xilinx ZCU106, Vivado 2023.2LUT: 45K, FF: 58K, BRAM: 120 (36Kb each), DSP: 150资源利用率<70%,无拥塞,时序满足100MHz混合精度(int8)卷积加速运行MobileNetV1第一层卷积,输入224x224x3相比纯标量实现,速度提升~18倍(实测)验证RVV对典型AIoT负载的有效加速

故障排查(Troubleshooting)

现象:仿真通过,上板后CPU卡在第一条向量指令。原因:VPU状态机未正确初始化或复位信号同步问题。检查点:ILA抓取复位后vstart, vl, vtype寄存器值;检查复位是否覆盖所有VPU状态寄存器。修复建议:确保使用异步复位同步释放策略,并在验证环境中加入上电复位序列测试。

现象:向量加载(vle32.v)数据错误。原因:字节序(Endianness)处理错误或内存地址未对齐。检查点:对比VPU发出的AXI地址与软件预期的地址;检查数据在总线上的字节顺序。修复建议:统一系统为小端序(Little-Endian),并对非对齐访问实现硬件支持或软件规避。

现象:运行特定vl值时结果不一致。原因:尾数(tail)和扰动(agnostic)元素处理逻辑有误。检查点:检查当vl < VLMAX时,目的寄存器尾数元素是否保持原值或被清零。修复建议:严格按RVV规范1.0第3.4.3节实现尾数策略,可在RTL中加入断言检查。

现象:FPGA实现后时序违例,关键路径在VRF。原因:VRF采用大位宽、多端口分布式RAM,布线延迟大。检查点:时序报告中的失败路径;VRF是否被推断为LUTRAM而非BRAM。修复建议:使用(* ram_style = "block" *)属性强制将VRF映射到BRAM;或对VRF读写操作流水化。

现象:性能远低于预期,CPI过高。原因:向量指令派发停顿,或访存停顿过多。检查点:性能计数器显示指令停顿周期;AXI总线利用率。修复建议:增加VPU的指令缓冲区;优化加载存储单元的流水线,支持未完成请求的 outstanding。

现象:系统在长时间压力测试后死机。原因:内存管理错误(如AXI响应丢失)、中断嵌套溢出或看门狗超时。检查点:死机前ILA抓取的异常PC值;AXI interconnect的仲裁状态。修复建议:在总线互联中加入监控与超时机制;增强异常处理程序的健壮性。

扩展与下一步

参数化探索:创建配置脚本,快速评估VLEN=256/512、ELEN=FP16/INT8等不同配置对性能和资源的影响,为ASIC设计选型提供数据。

集成自定义AI加速指令:在RVV基础上,添加针对特定神经网络算子(如深度可分离卷积)的定制向量指令,验证其加速效果。

软硬件协同验证:将原型系统与实时操作系统(如Zephyr)或AI推理框架(如TFLite Micro)集成,验证端到端应用。

形式验证应用:对VPU的控制逻辑(如状态机、仲裁器)使用形式验证工具(如JasperGold),穷举证明其正确性,弥补动态测试的不足。

功耗估算:利用FPGA工具的功耗分析功能,结合向量运算的活动因子,对ASIC的功耗进行早期建模与预估。

参考与信息来源

“The RISC-V Instruction Set Manual, Volume I: Unprivileged ISA”, Chapter 16 “Vector Extension”, Version 1.0. 官方规范。

CVA6 (Ariane) 开源处理器项目, GitHub仓库中的RVV开发分支。

<!-- wp

前置条件与环境

<!-- /wp:headin验证与结果

<!-- /wp:headin测试项目条件与配置测量结果验收点RVV基础指令(vadd, vmul)VLEN=128, ELEN=32, vl=16, 仿真波形显示vd结果与软件模型完全一致功能正确向量乘加(vfmacc.vv)性能FPGA @100MHz, 矩阵大小32x32, 使用循环展开执行周期:~5200 cycles, 计算吞吐:~39 MFLOPS性能与理论值(~64 MFLOPS)在可接受偏差内,瓶颈分析为DDR访存FPGA资源占用Xilinx ZCU106, Vivado 2023.2LUT: 45K, FF: 58K, BRAM: 120 (36Kb each), DSP: 150资源利用率<70%,无拥塞,时序满足100MHz混合精度(int8)卷积加速运行MobileNetV1第一层卷积,输入224x224x3相比纯标量实现,速度提升~18倍(实测)验证RVV对典型AIoT负载的有效加速故障排查(Troubleshooting)现象:仿真通过,上板后CPU卡在第一条向量指令。原因:VPU状态机未正确初始化或复位信号同步问题。检查点:ILA抓取复位后vstart, vl, vtype寄存器值;检查复位是否覆盖所有VPU状态寄存器。修复建议:确保使用异步复位同步释放策略,并在验证环境中加入上电复位序列测试。现象:向量加载(vle32.v)数据错误。原因:字节序(Endianness)处理错误或内存地址未对齐。检查点:对比VPU发出的AXI地址与软件预期的地址;检查数据在总线上的字节顺序。修复建议:统一系统为小端序(Little-Endian),并对非对齐访问实现硬件支持或软件规避。现象:运行特定vl值时结果不一致。原因:尾数(tail)和扰动(agnostic)元素处理逻辑有误。检查点:检查当vl < VLMAX时,目的寄存器尾数元素是否保持原值或被清零。修复建议:严格按RVV规范1.0第3.4.3节实现尾数策略,可在RTL中加入断言检查。现象:FPGA实现后时序违例,关键路径在VRF。原因:VRF采用大位宽、多端口分布式RAM,布线延迟大。检查点:时序报告中的失败路径;VRF是否被推断为LUTRAM而非BRAM。修复建议:使用(* ram_style = "block" *)属性强制将VRF映射到BRAM;或对VRF读写操作流水化。现象:性能远低于预期,CPI过高。原因:向量指令派发停顿,或访存停顿过多。检查点:性能计数器显示指令停顿周期;AXI总线利用率。修复建议:增加VPU的指令缓冲区;优化加载存储单元的流水线,支持未完成请求的 outstanding。现象:系统在长时间压力测试后死机。原因:内存管理错误(如AXI响应丢失)、中断嵌套溢出或看门狗超时。检查点:死机前ILA抓取的异常PC值;AXI interconnect的仲裁状态。修复建议:在总线互联中加入监控与超时机制;增强异常处理程序的健壮性。扩展与下一步参数化探索:创建配置脚本,快速评估VLEN=256/512、ELEN=FP16/INT8等不同配置对性能和资源的影响,为ASIC设计选型提供数据。集成自定义AI加速指令:在RVV基础上,添加针对特定神经网络算子(如深度可分离卷积)的定制向量指令,验证其加速效果。软硬件协同验证:将原型系统与实时操作系统(如Zephyr)或AI推理框架(如TFLite Micro)集成,验证端到端应用。形式验证应用:对VPU的控制逻辑(如状态机、仲裁器)使用形式验证工具(如JasperGold),穷举证明其正确性,弥补动态测试的不足。功耗估算:利用FPGA工具的功耗分析功能,结合向量运算的活动因子,对ASIC的功耗进行早期建模与预估。参考与信息来源“The RISC-V Instruction Set Manual, Volume I: Unprivileged ISA”, Chapter 16 “Vector Extension”, Version 1.0. 官方规范。CVA6 (Ariane) 开源处理器项目, GitHub仓库中的RVV开发分支。<!-- wp前置条件与环境

<!-- /wp:headin项目推荐值/配置说明与替代方案FPGA平台Xilinx ZCU106 (Zynq UltraScale+) 或 Intel DE10-Agilex需具备足够逻辑资源(>300K LUT)与DDR4接口。替代:VCU118、Arria 10 SoC DK。EDA工具Vivado 2023.2 / Quartus Prime 23.1需支持SystemVerilog-2012。Vivado HLS可用于加速器模块原型。RISC-V处理器核CVA6 (Ariane) with RVV 1.0 patch 或 SweRV EH2 + 自定义VPU必须支持目标RVV配置(如VLEN=128/256, ELEN=32)。商业IP可选Codasip、Andes。仿真环境Verilator 5.0+ 配合GTKWave,或商用VCS/Xcelium用于前仿真。需支持多线程以加速向量长序列仿真。软件工具链RISC-V GNU Toolchain (rvv-1.0分支) 或 LLVM用于编译C/内联汇编测试程序。确保-march=rv64gcv参数正确。验证IP/模型DDR4 Controller Model, UART VIP, 或简易Bus Functional Model (BFM)用于仿真时代替物理外设。可使用Verilator的DPI-C编写简单内存模型。物理约束时钟:100MHz系统时钟,200MHz DDR参考时钟根据板卡原理图定义。复位需为低有效,异步复位同步释放。总线互联AXI4 (64-bit/128-bit) 用于主存,AXI4-Lite用于外设确保VPU的访存带宽与延迟满足向量加载/存储需求。

目标与验收标准

完成本流程后,应实现一个在FPGA上可运行的RVV原型系统,并通过以下验收:

功能正确性:运行RVV合规性测试套件(如riscv-arch-test的V扩展部分)或自定义向量算法(如矩阵乘、卷积),结果与Golden C模型匹配。

性能可观测:通过性能计数器或软件时间戳,测量关键向量内核(如vfmacc.vv)的CPI(Cycles Per Instruction)或MFLOPS,并与理论峰值对比。

时序收敛:FPGA实现后,关键路径(通常位于VPU的向量寄存器文件旁路或ALU流水线)满足目标频率(如100MHz),建立/保持时间无违例。

资源占用可控:VPU模块在目标FPGA上的逻辑资源(LUT/FF)与BRAM占用符合预期,通常向量寄存器文件是主要资源消耗者。

系统稳定性:连续运行压力测试(如长时间向量随机运算)无死机、数据损坏,中断与异常处理正确。

实施步骤

阶段一:工程结构与环境搭建

创建清晰的目录结构:rtl/(核心RTL)、tb/(测试平台)、sw/(测试程序)、constraints/(约束文件)、scripts/(构建与仿真脚本)。使用Makefile或Python脚本自动化流程。

常见坑与排查:

坑1:工具链不匹配导致非法指令。检查编译时-march和-mabi是否与硬件设计(如XLEN、VLEN)一致。使用objdump -d反汇编确认生成的指令编码正确。

坑2:仿真内存模型行为与真实DDR不一致。简易内存模型可能无延迟,导致仿真通过但上板失败。建议使用带可配置延迟的BFM或集成FPGA厂商的DDR仿真模型。

阶段二:关键模块集成与验证

重点集成向量处理单元(VPU)。VPU通常包含向量寄存器文件(VRF)、多个并行流水线(ALU、LSU、乘加单元)和状态寄存器(vtype, vl, vstart)。确保标量核与VPU间的指令派发、异常同步正确。

// 示例:一个简化的向量ALU控制信号生成片段(SystemVerilog)

always_comb begin

case (vfu_op_i)

VADD: vresult = va + vb;

VAND: vresult = va & vb;

VMUL: vresult = va * vb; // 可能为多周期流水

default: vresult = '0;

endcase

end

// 注意:需处理元素掩码(vm)和尾数(tail)与扰动(agnostic)策略。

常见坑与排查:

坑3:向量长度(vl)变化时流水线数据 hazard。当vl在下一条指令中变小时,原长向量操作的未完成部分可能错误写回。解决方案:引入vl变化冲刷流水线,或使用基于vstart的精确异常处理。

坑4:VRF多端口读写冲突。RVV支持多个源向量和一个目的向量同时操作。确保VRF读写端口数足够(如4读2写),或通过时钟周期分时复用并妥善处理RAW冲突。

阶段三:时序约束与物理实现

为FPGA综合与实现编写约束。关键约束包括主时钟、生成时钟(如DDR PHY)、VPU内部跨时钟域(如果有)、I/O延迟。

# 示例:Vivado XDC 关键约束片段

create_clock -period 10.000 -name sys_clk [get_ports sys_clk_p]

# 对大型向量寄存器文件,可放宽局部路径约束以改善布局

set_max_delay -from [get_cells vrf/ram_reg*] -to [get_cells vrf/ram_reg*] 2.000

# 对从DDR到VPU的数据路径设置输入延迟

set_input_delay -clock [get_clocks ddr_clk] -max 1.500 [get_ports vpu_ddr_data_i*]

阶段四:上板验证与调试

利用FPGA的调试功能:集成ILA(Vivado)或SignalTap(Quartus)抓取VPU关键信号(如vstart, vl, vd写使能)。通过UART打印调试信息(如异常PC、vl值)。

原理与设计说明

RVV在AIoT芯片中的FPGA原型验证,核心矛盾在于硬件设计的灵活性与验证场景的复杂性之间的权衡。

1. 可配置性与资源消耗:RVV标准允许VLEN(向量寄存器长度)和ELEN(元素长度)参数化。在FPGA上,VLEN=256相比VLEN=128,VRF的BRAM消耗可能翻倍,但能提供更高的数据级并行。AIoT场景通常选择VLEN=128/256作为平衡点。设计时应使用参数化RTL,便于快速评估不同配置。

2. 访存带宽与延迟容忍:向量指令的吞吐常受限于内存带宽。FPGA原型上,通过宽位AXI总线(如128位)和DDR Burst传输来模拟ASIC的高带宽。设计VPU的加载/存储单元时,应采用深度预取缓冲(Prefetch Buffer)以隐藏DDR延迟,这与AIoT芯片中采用紧密耦合存储器(TCM)的策略不同,是原型验证时需要特别注意的差异点。

3. 验证完备性与效率:RVV指令组合繁多(掩码、尾数、扰动策略)。在FPGA上全量回归不现实。策略是:在仿真阶段使用受限随机测试结合RVV合规套件进行充分验证;在FPGA上则运行代表性的AI内核(如int8卷积、fp16矩阵乘)进行压力与性能测试。这构成了从形式到场景的混合验证路径。

验证与结果

<!-- /wp:headin

测试项目条件与配置测量结果验收点RVV基础指令(vadd, vmul)VLEN=128, ELEN=32, vl=16, 仿真波形显示vd结果与软件模型完全一致功能正确向量乘加(vfmacc.vv)性能FPGA @100MHz, 矩阵大小32x32, 使用循环展开执行周期:~5200 cycles, 计算吞吐:~39 MFLOPS性能与理论值(~64 MFLOPS)在可接受偏差内,瓶颈分析为DDR访存FPGA资源占用Xilinx ZCU106, Vivado 2023.2LUT: 45K, FF: 58K, BRAM: 120 (36Kb each), DSP: 150资源利用率<70%,无拥塞,时序满足100MHz混合精度(int8)卷积加速运行MobileNetV1第一层卷积,输入224x224x3相比纯标量实现,速度提升~18倍(实测)验证RVV对典型AIoT负载的有效加速

故障排查(Troubleshooting)

现象:仿真通过,上板后CPU卡在第一条向量指令。原因:VPU状态机未正确初始化或复位信号同步问题。检查点:ILA抓取复位后vstart, vl, vtype寄存器值;检查复位是否覆盖所有VPU状态寄存器。修复建议:确保使用异步复位同步释放策略,并在验证环境中加入上电复位序列测试。

现象:向量加载(vle32.v)数据错误。原因:字节序(Endianness)处理错误或内存地址未对齐。检查点:对比VPU发出的AXI地址与软件预期的地址;检查数据在总线上的字节顺序。修复建议:统一系统为小端序(Little-Endian),并对非对齐访问实现硬件支持或软件规避。

现象:运行特定vl值时结果不一致。原因:尾数(tail)和扰动(agnostic)元素处理逻辑有误。检查点:检查当vl < VLMAX时,目的寄存器尾数元素是否保持原值或被清零。修复建议:严格按RVV规范1.0第3.4.3节实现尾数策略,可在RTL中加入断言检查。

现象:FPGA实现后时序违例,关键路径在VRF。原因:VRF采用大位宽、多端口分布式RAM,布线延迟大。检查点:时序报告中的失败路径;VRF是否被推断为LUTRAM而非BRAM。修复建议:使用(* ram_style = "block" *)属性强制将VRF映射到BRAM;或对VRF读写操作流水化。

现象:性能远低于预期,CPI过高。原因:向量指令派发停顿,或访存停顿过多。检查点:性能计数器显示指令停顿周期;AXI总线利用率。修复建议:增加VPU的指令缓冲区;优化加载存储单元的流水线,支持未完成请求的 outstanding。

现象:系统在长时间压力测试后死机。原因:内存管理错误(如AXI响应丢失)、中断嵌套溢出或看门狗超时。检查点:死机前ILA抓取的异常PC值;AXI interconnect的仲裁状态。修复建议:在总线互联中加入监控与超时机制;增强异常处理程序的健壮性。

扩展与下一步

参数化探索:创建配置脚本,快速评估VLEN=256/512、ELEN=FP16/INT8等不同配置对性能和资源的影响,为ASIC设计选型提供数据。

集成自定义AI加速指令:在RVV基础上,添加针对特定神经网络算子(如深度可分离卷积)的定制向量指令,验证其加速效果。

软硬件协同验证:将原型系统与实时操作系统(如Zephyr)或AI推理框架(如TFLite Micro)集成,验证端到端应用。

形式验证应用:对VPU的控制逻辑(如状态机、仲裁器)使用形式验证工具(如JasperGold),穷举证明其正确性,弥补动态测试的不足。

功耗估算:利用FPGA工具的功耗分析功能,结合向量运算的活动因子,对ASIC的功耗进行早期建模与预估。

参考与信息来源

“The RISC-V Instruction Set Manual, Volume I: Unprivileged ISA”, Chapter 16 “Vector Extension”, Version 1.0. 官方规范。

CVA6 (Ariane) 开源处理器项目, GitHub仓库中的RVV开发分支。

<!-- wp