在FPGA系统设计中,功耗优化已成为与性能、面积同等重要的设计目标。总功耗主要由动态功耗(开关活动引起)和静态功耗(漏电流引起)构成。随着工艺节点不断微缩,静态漏电功耗的占比日益凸显。本文旨在提供一份结构化的工程实践指南,深入解析时钟门控(降低动态功耗)与电源门控(降低静态功耗)两大核心技术,并引导设计者在Xilinx或Intel FPGA平台上,完成从代码编写、工具配置到仿真验证的全流程低功耗设计实现。

快速上手指南 (Quick Start)

若你已熟悉基本流程,可遵循以下步骤快速搭建一个包含基础功耗管理功能的设计框架:

- 步骤一:创建工程与器件选择。在Vivado中新建工程,目标器件选择支持高级功耗管理特性的系列,如Xilinx UltraScale+或Intel Agilex。

- 步骤二:编写支持时钟门控的RTL代码。设计一个寄存器模块,使用

if (en) clk的编码风格来显式描述时钟门控逻辑,为综合工具提供明确的插入指引。 - 步骤三:启用自动时钟门控插入。在Vivado的Tcl控制台中,输入命令

set_property CLOCK_GATE_TYPE auto [get_cells your_reg*],指示工具对指定寄存器自动插入时钟门控单元。 - 步骤四:定义电源域。对于需要深度休眠的模块(例如协处理器),在XDC约束文件中使用

create_power_domain命令为其创建独立的电源域,这是实施电源门控的前提。 - 步骤五:分析功耗报告。完成设计实现后,打开“Implemented Design”并运行“Report Power”。重点查看“Clock Gating”和“Power Gating”部分提供的功耗节省估算。

- 步骤六:进行门级时序仿真。使用Vivado Simulator或ModelSim进行带SDF反标的门级仿真,验证时钟门控使能信号与时钟之间的时序关系,确保无功能错误或毛刺产生。

- 步骤七:上板实测验证。将比特流下载至FPGA开发板,使用电流探头或板载电源管理单元(PMU)分别测量动态工作模式与休眠模式下的系统电流,量化实际的功耗优化效果。

- 验收点:功耗分析报告应显示时钟网络功耗显著降低;门级仿真波形中,当时钟门控使能无效时,相关寄存器的时钟引脚上应无跳变活动。

前置条件与环境准备

| 项目 | 推荐值/要求 | 说明与替代方案 |

|---|---|---|

| FPGA器件系列 | Xilinx UltraScale/UltraScale+; Intel Stratix 10/Agilex | 这些系列内置了对时钟门控与电源门控的硬件原语支持。替代方案:7系列/Arria 10等仅支持基础时钟门控。 |

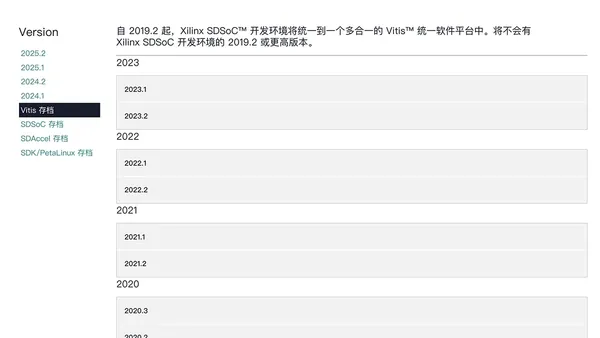

| EDA工具版本 | Vivado 2020.1+; Quartus Prime 20.1+ | 需支持UPF/CPF等功耗意图描述文件的读入、分析与实现。 |

| 仿真工具 | Vivado Simulator (XSim), ModelSim/QuestaSim | 用于验证时钟门控使能时序。VCS/Xcelium可用于更复杂的电源状态仿真。 |

| 时钟架构 | 全局时钟网络(BUFGCE/BUFGCE_1) | 时钟门控推荐使用专用的时钟使能缓冲器,避免使用通用逻辑门控时钟,以消除毛刺风险并保证时钟质量。 |

| 电源架构 | 支持多电压区域(Voltage Area) | 电源门控的前提。需确认板卡电源设计能为休眠域提供独立的下电与上电控制。 |

| 约束文件 | XDC (Vivado) 或 QSF/SDC (Quartus), 可选UPF/CPF | 定义时钟、时序例外以及电源域。UPF/CPF用于描述复杂的电源管理策略(如关断序列、保持寄存器)。 |

| 验证环境 | 带功耗感知的仿真流程 | 需能模拟电源关断、保持寄存器的状态丢失与恢复等场景。 |

| 板级监控 | 数字万用表、电流探头或板载PMU/I2C电源监控芯片 | 用于实测功耗,验证设计效果。替代:在项目早期可使用工具提供的功耗估算报告进行初步评估。 |

设计目标与验收标准

本实践旨在达成以下具体、可量化且可验证的设计目标:

- 功能正确性:在时钟门控使能有效/无效、电源域上电/关断等所有功耗管理状态下,系统核心功能必须符合预期,无数据丢失、逻辑错误或死锁。

- 动态功耗降低:通过有效的时钟门控,目标模块在空闲时段内的动态功耗(主要来自时钟网络分布和寄存器翻转)应降低30%-70%,具体比例取决于模块的空闲占比。

- 静态功耗降低:通过对非活跃模块实施电源门控,使其在关断状态下的静态漏电功耗降低90%以上(理论上可接近零)。

- 时序收敛:引入时钟门控和电源门控逻辑及约束后,设计必须满足所有建立时间与保持时间约束,关键路径无时序违例。

验收方式:

- 仿真波形验证:1) 验证时钟门控使能(CE)信号与时钟(CLK)的时序满足目标寄存器的建立/保持时间要求;2) 验证电源关断与上电序列中,保持寄存器(若使用)的值被正确保存与恢复。

- 工具报告分析:综合与实现后的功耗分析报告(如Vivado的“Report Power”)中,需明确显示时钟门控与电源门控带来的功耗节省估算。

- 上板实测比对:使用仪器实际测量系统在活跃模式与休眠模式下的总电流或功耗,实测数据应与工具报告的趋势基本一致。

详细实施步骤

阶段一:RTL设计与时钟门控插入

1. 采用引导性编码风格:最可靠的方式是编写易于综合工具识别的RTL代码,让其自动插入经过优化的时钟门控单元。避免手动例化门电路来门控时钟,这极易产生毛刺。

// 推荐:使用带显式使能信号的always块,引导综合工具插入时钟门控单元

reg [7:0] data_reg;

always @(posedge clk or posedge rst) begin

if (rst) begin

data_reg <= 8‘h0;

end else if (clk_en) begin // 工具会识别此条件,并在clk_en为假时关闭时钟

data_reg <= data_in;

end

end2. 配置综合工具:在Vivado中,可通过Tcl命令或GUI设置,为特定模块或寄存器启用自动时钟门控插入策略,并选择插入的单元类型(如LATCH-based或AND-based)。

阶段二:电源域划分与电源门控实现

1. 架构规划:识别设计中可以独立断电的功能模块(如长时间闲置的协处理器、备份逻辑)。在物理上,这些模块应位于FPGA中支持独立供电的区域。

2. 使用UPF定义功耗意图:创建Unified Power Format (UPF)文件,明确定义电源域、电源开关、隔离单元和保持寄存器。

# 示例UPF片段:创建一个可关断的电源域

create_power_domain PD_COPROC

-elements {.coprocessor_inst}

-supply {primary VDD_COPROC}

create_power_switch SW_COPROC

-domain PD_COPROC

-input_supply_port {in VDD}

-output_supply_port {out VDD_COPROC}

-control_port {sleep_ctrl sleep_signal}

-on_state {on_state in {!sleep_signal}}3. 设计电源状态控制器(PSM):实现一个有限状态机,严格按照器件要求的时间序,控制电源开关、隔离使能和保持寄存器保存/恢复信号的产生。

阶段三:约束、实现与验证

1. 加载功耗约束:在Vivado中,通过read_power命令加载UPF文件。确保时序约束(SDC/XDC)已覆盖所有电源状态下的路径。

2. 实现与功耗分析:运行综合与实现。实现后,详细分析“Power Report”,关注时钟门控效率、电源门控的漏电节省以及任何由功耗管理逻辑引入的新时序路径。

3. 功耗感知仿真:使用支持UPF的仿真器,运行覆盖电源关断、上电、休眠唤醒等场景的仿真,验证状态机序列、数据隔离与恢复功能的正确性。

结果验证与问题排查

- 时钟门控未生效:检查RTL代码风格是否被工具识别;检查综合设置中是否禁用了时钟门控;查看网表,确认目标寄存器前是否插入了BUFGCE或等效单元。

- 电源门控时序违例:检查电源开关控制信号、隔离使能信号的时序约束是否完备。这些信号通常需要被设置为“false path”或施加特定的多周期路径约束。

- 仿真与实测功耗差异大:确认仿真激励是否真实反映了实际工作场景的活动率;检查板级测量时,是否已确保目标电源域确实被关断(可通过测量该域供电引脚电压验证)。

扩展应用与进阶考量

在掌握基础实践后,可进一步探索:

- 层次化时钟门控:在模块级、时钟域级进行更大粒度的时钟门控,进一步降低时钟树功耗。

- 动态电压与频率缩放(DVFS):结合电源门控,根据性能需求动态调整电压和频率,实现更精细的功耗性能权衡。

- 保持寄存器的选择策略:分析状态丢失的成本,决定是使用简单的隔离(数据清零)还是昂贵的保持寄存器(数据保存)。

参考资源

- Xilinx, UltraScale Architecture Power Management User Guide (UG583)

- Intel, Stratix 10 Power Management User Guide

- IEEE Standard for Unified Power Format (UPF), IEEE Std 1801-2018

附录:关键机制与风险边界分析

时钟门控的工作原理与风险:其本质是在寄存器时钟路径上插入一个使能控制的门电路(通常由工具映射为专用的时钟使能缓冲器)。主要风险在于使能信号与时钟的竞争冒险可能产生毛刺时钟,导致寄存器误触发。因此,必须由工具自动插入基于锁存器的门控单元,其结构能确保使能信号在时钟高电平时稳定,从根本上消除毛刺。

电源门控的实施路径与代价:实施路径分为架构规划(划分电源域)、意图描述(UPF)、物理实现(布局布线满足电源网络隔离)和验证(序列与功能)。其代价包括:1) 面积开销:电源开关、隔离单元、保持寄存器会消耗额外的芯片面积;2) 状态恢复延迟:模块从关断到唤醒工作需要供电稳定、状态恢复的时间,带来性能延迟;3) 设计复杂性剧增:需要完备的电源状态机、跨电压域信号处理策略和更复杂的验证流程。因此,电源门控通常应用于粗粒度、长时间空闲的功能模块,以抵消其引入的额外开销。