在数字信号处理(DSP)的世界里,滤波器就像一位聪明的“信号化妆师”,能帮你提取有用的频率、抑制讨厌的噪声。今天,我们要聊的主角是FIR滤波器——它结构稳定、相位特性好,是通信、音频等领域的“明星选手”。

想在FPGA上玩转FIR滤波器,让它既跑得快又省资源吗?这篇实战指南,就是为你准备的。我们会从基础原理聊到优化“骚操作”,手把手带你走通设计全流程。

一、FIR入门:从理论到硬件实现流程

FIR滤波器的输出只和当前及过去的输入有关,没有“历史包袱”(反馈回路)。一个N阶FIR的核心运算就是卷积:y[n] = Σ (h[k] * x[n-k]),其中h[k]就是决定滤波器性格的系数。

在FPGA上实现它,你可以遵循下面这个清晰的“六步法”:

- 定指标:先想清楚你要什么——通带、阻带、波纹大小?这是设计的起点。

- 算系数:打开MATLAB或Python(SciPy),用窗函数法或等波纹法生成理想的滤波器系数。

- 选结构:这是关键一步!直接型、转置型、对称结构还是分布式算法?不同的结构在速度和资源上各有千秋。

- 写代码:用Verilog/VHDL把你选好的结构“翻译”成RTL代码。

- 仿真验:搭个Testbench,和MATLAB的结果对比一下,确保逻辑正确,时序过关。

- 综合优化:上Vivado/Quartus跑一遍,看资源用了多少,时序是否满足。不满意?那就迭代优化吧!

二、四大实现结构,你Pick哪一个?

结构选得好,性能没烦恼。下面这四种经典结构,决定了你设计的“基本盘”。

1. 直接型:最直观的“直男”结构

想到就做,直接实现卷积公式。它需要N个乘法器和一串加法器。缺点也很明显:关键路径太长,就像一条拥挤的单车道,时钟频率很难提上去。代码里常用移位寄存器来缓存数据流。

2. 转置型:高速流水线的“宠儿”

这是直接型的“转置”版本。最大优点是关键路径极短(就一个乘法加一个加法),特别适合飙高时钟频率,是FPGA里最常用的高性能结构之一。

3. 对称结构:省资源的“小机灵鬼”

如果你的滤波器具有线性相位,系数会呈现对称性。利用这个特点,可以把乘法器的数量几乎砍半!实现时,先把对称位置的数据加起来,再乘系数,能大大节省宝贵的DSP Slice。

4. 分布式算法(DA):用存储换计算的“策略家”

DA是个经典思路:它把卷积运算变成了查表(LUT)和累加,完全不用通用乘法器。原理是把输入数据按位拆开,提前把系数所有可能的组合算好存进查找表。适合系数固定、数据位宽不大的场景,能高效利用LUT,但可能会多用一些BRAM。

三、性能飙升!核心优化策略盘点

代码能跑只是开始,让它跑得又快又省才是我们的目标。下面这些优化技巧,就是你的“性能加速包”。

- 精度与量化:MATLAB给的浮点系数得转成定点数(比如Q格式)才能用。量化会引入误差,需要你在性能和资源之间做权衡。内部累加器的位宽记得留足,防止“溢出”尴尬。

- 流水线化:在长长的组合逻辑里插入寄存器,把工作分成几个时钟周期完成。这是打破时序瓶颈、提升频率的“神器”。转置型结构天生就适合流水线。

- 资源复用:如果采样率不高,可以让一个乘法器“打几份工”,分时复用计算所有卷积项。能极大节省资源,当然吞吐量会降低。

- 拥抱DSP Slice:现代FPGA(如Xilinx UltraScale+、Intel Agilex)里的DSP Slice是高度优化的硬核,用好它们(正确推断或实例化)能获得最佳性能和能效。用它内部的预加法器来实现对称结构,效率超高。

- 系统级大招:多相结构:在采样率转换系统里,把滤波器和抽取/插值器结合成多相结构,能让滤波器在更低速率下工作,大幅降低计算量和功耗。软件无线电(SDR)里这招是标配。

四、验证调试:给设计上份“保险”

可靠的验证是成功的一半,千万别跳过这一步。

- 写好Testbench:用SystemVerilog/Verilog搭建自动化测试环境,生成正弦波、扫频信号,并自动对比FPGA输出和MATLAB“黄金参考”的误差。

- MATLAB协同仿真:让MATLAB生成测试数据,或者把FPGA仿真结果导回去做频谱分析,双剑合璧,查错更准。

- 时序约束不能少:务必给时钟、接口加上正确的约束(SDC/XDC),高速设计还要处理好多周期路径和虚假路径。

- 片上实时调试:最后,用ILA或SignalTap II在真实芯片上抓波形,这是排查疑难杂症的终极手段。

五、学习路径与实战建议

FIR滤波器的FPGA实现,是一场算法、硬件与工程思维的融合之旅。从“能工作”到“很优秀”,这条路我们可以这样走:

- 用MATLAB设计一个低通FIR,把系数量化好。

- Verilog实现一个直接型结构,完成功能仿真,感受一下。

- 把它改成转置型,加上流水线,亲眼看看时序的提升。

- 为线性相位滤波器加上对称优化,对比一下资源报告的变化。

- 试试Vivado HLS等高层次综合工具,和手写RTL比比看。

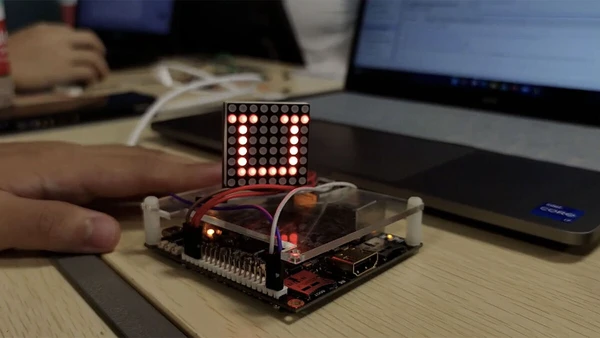

- 终极挑战:实现一个带多相抽取的高阶FIR,并烧写到开发板实测!

通过这样一步步的实战,你会深刻体会到FPGA在数字信号处理中的强大与灵活。这不仅是掌握一个滤波器,更是为你将来设计更复杂的通信、图像或AI加速系统打下坚实的地基。

在成电国芯FPGA培训的DSP专题课程中,我们将带你完整走通这条实战路径,并提供专家级的代码评审与优化指导。一起动手,让想法在硬件上飞驰吧!