在vivado中,有的IP核已经包含了模块的引脚配置,这样在约束文件中就不用写相应的约束设置。然而在生成位码流的时候就可能会出现如下的错误提示:

[DRC UCIO-1] Unconstrained Logical Port: 16 out of 22 logical ports have no user assigned specific location constraint (LOC). This may cause I/O contention or incompatibility with the board power or connectivity affecting performance, signal integrity or in extreme cases cause damage to the device or the components to which it is connected. To correct this violation, specify all pin locations. This design will fail to generate a bitstream unless all logical ports have a user specified site LOC constraint defined. To allow bitstream creation with unspecified pin locations (not recommended), use this command:

set_property SEVERITY {Warning} [get_drc_checks UCIO-1]. NOTE: When using the Vivado Runs

infrastructure (e.g. launch_runs Tcl command), add this command to a .tcl file and add that file as a pre-hook for write_bitstream step for the implementation run. Problem ports: RXN_IN[3:0],RXP_IN[3:0], TXN_OUT[3:0], and TXP_OUT[3:0].

以上错误提示的大概意思如下:

没有约束的逻辑端口:22个逻辑端口中有16个没有用特殊的指定位置约束。这样可能导致IO口出现竞争、板子功耗不兼容或者影响到彼此之间的连接性能,同时还有信号完整性或者极端情况下会损坏与之相连接的设备或元件。若要更正以上这次的违规操作,就需要具体说明所有引脚的位置。除非用户指定了所有的逻辑端口,否则生成位码流的设计会失败。用“set_property SEVERITY {Warning} [get_drc_checks UCIO-1]”这个命令可以不指定引脚位置来生成位码流(一般这种方式是不推荐的)。

注意:当运行Vivado的基础结构(例如启动运行TCL命令)时,要增加上面提到的这个命令到一个tcl文件中,同时添加该文件到tcl.pre参数下从而实现运行写位码流这一步骤。

有问题的端口:RXN_IN[3:0]、RXP_IN[3:0]、 TXN_OUT[3:0]、和TXP_OUT[3:0],换句话说,有问题的引脚有16个,分别为:RXN_IN0、RXN_IN1、RXN_IN2、RXN_IN3、RXP_IN0、RXP_IN1、RXP_IN2、RXP_IN3、TXN_OUT0、TXN_OUT1、TXN_OUT2、TXN_OUT3、TXP_OUT0、TXP_OUT1、TXP_OUT2、TXP_OUT3。

以上错误提示中提到两方面的内容:

1、需要的相关命令保存到一个新的tcl文件中;

2、把新生成的tcl文件路径添加到tcl.pre下。

具体的操作如下所示:

打开新的txt文件,输入以下命令:

set_property SEVERITY {Warning} [get_drc_checks NSTD-1]

set_property SEVERITY {Warning} [get_drc_checks UCIO-1]

set_property SEVERITY {Warning} [get_drc_checks RTSTAT-1]

注意:

可以根据提示写相应的命令,也可以把以上三条命令都写上。然后把此txt文件另存为tcl文件,如命名为“test.tcl”。

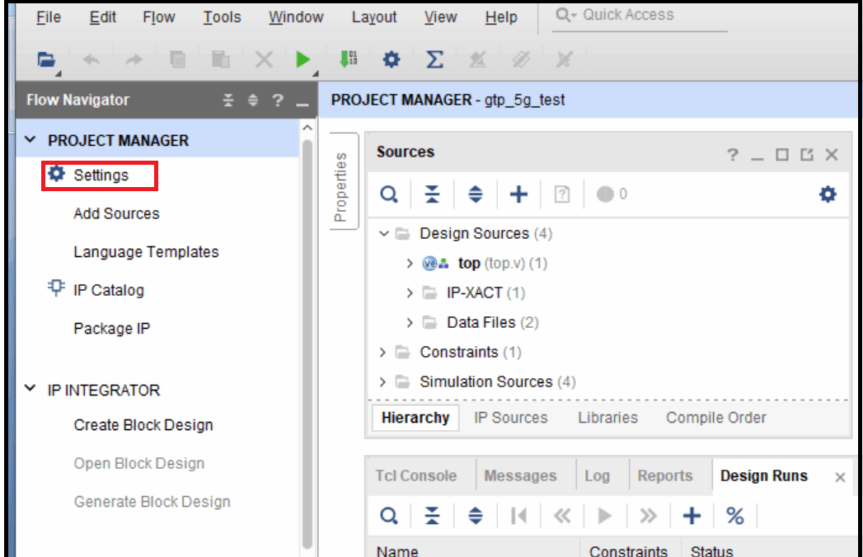

在vivado界面中,点击PROJECT MANAGER下面的setting,如下图所示:

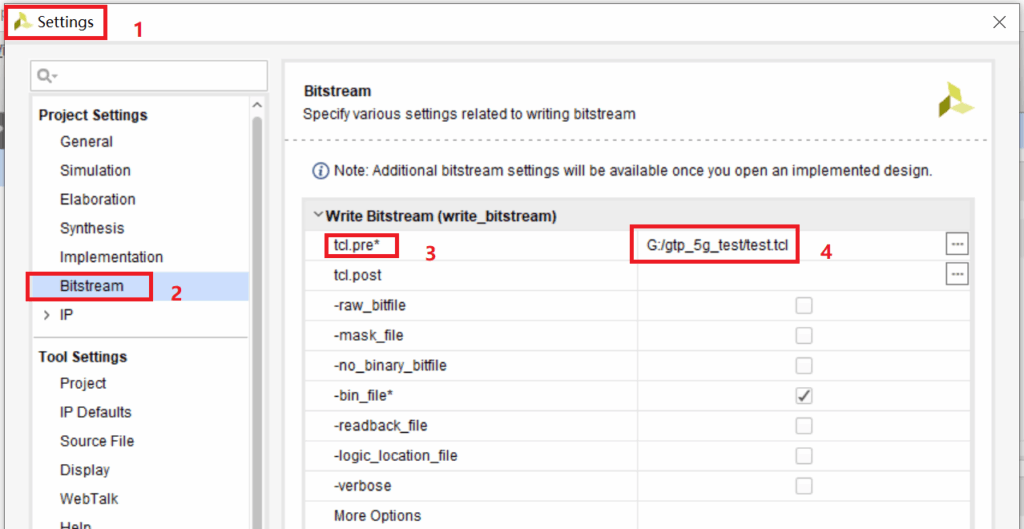

在弹出的1号标记界面中,找到标记“project settings”目录下的2号标记“Bitstream”,把相关路径下的新建4号标记的“test.tcl”文件添加到3号标记的tcl.pre参数下,然后点击“OK”按钮即可,如下图所示:

重新编译即可生成位码流。