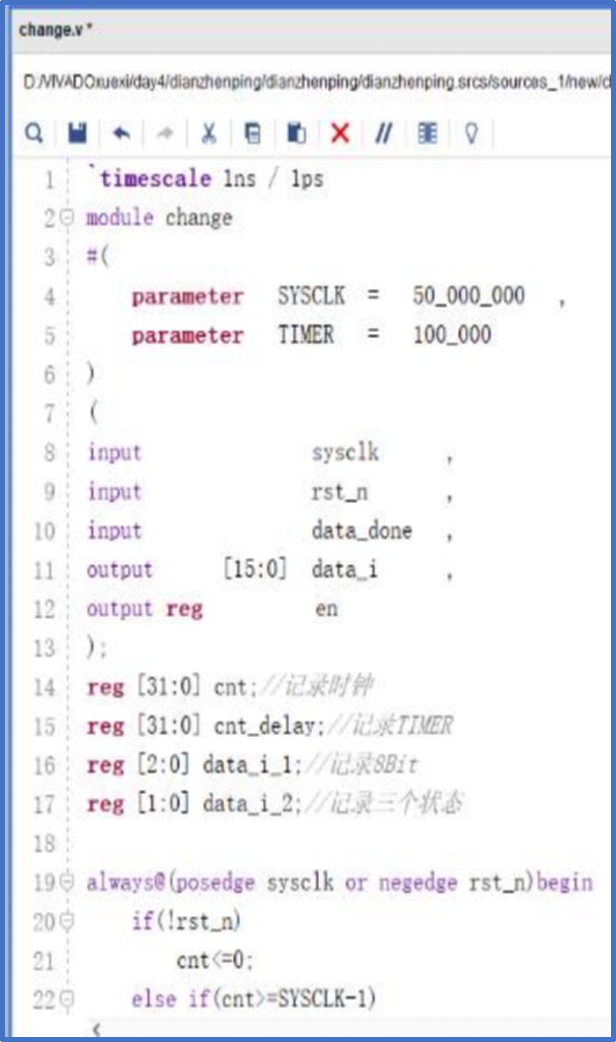

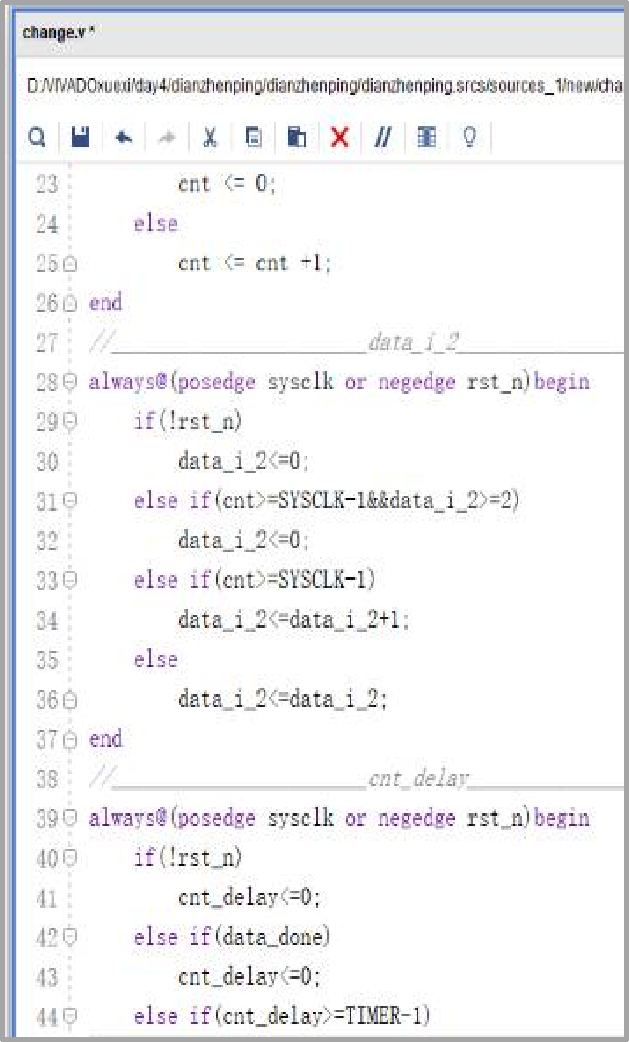

verilog代码:(注意格式)

`timescale 1ns / 1ps

module HC_595

#(

parameter SYSCLK = 50_000_000,//系统时钟频率

parameter CLK_HZ = 100_000 //用系统时钟产生一个100k的频率的时钟

)

(

input sysclk ,

input rst_n ,

input [15:0] Data ,

input en ,//开始信号

output reg SCK ,

output reg RCK ,

output reg DA ,

output reg Done //结束信号

);

localparam DELAY = SYSCLK/CLK_HZ;

localparam MID = DELAY/2;

reg [31:0] cnt_delay;

reg [31:0] cnt_mid;

reg [1:0] en_temp;

reg [15:0] data_temp;//用于存储输入进来的16bit数据

localparam IDLE = 3'b001,

DATA = 3'b010,

STOP = 3'b100;

reg [2:0] cur_state,next_state;

reg [4:0] cnt_bit;

//______________________________滤除毛刺__________________________________//

always@(posedge sysclk)

if(!rst_n)

en_temp <= 2'b00;

else

en_temp <= {en_temp[0],en};

//___________________________DELAY__________________________________//

always@(posedge sysclk)

if(!rst_n)

cnt_delay <= 32'd0;

else if(cnt_delay >= DELAY - 1 )

cnt_delay <= 32'd0;

else cnt_delay <= cnt_delay + 32'd1;

//___________________________MID__________________________________//

always@(posedge sysclk)

if(!rst_n)

cnt_mid <= 32'd0;

else if(cnt_mid >= MID - 1 )

cnt_mid <= 32'd0;

else

cnt_mid <= cnt_mid + 32'd1;

//______________________________产生SCK__________________________________//

always@(posedge sysclk)

if(!rst_n)

SCK <= 1'b0;

else if(cnt_mid >= MID - 1)

SCK <= ~SCK;

else

SCK <= SCK;

//_________________________state1____________________________________//

always@(posedge sysclk)

if(!rst_n)

cur_state <= IDLE;

else

cur_state <= next_state;

//_______________________________state2_____________________________________//

always@(*)

case(cur_state)

IDLE:begin

if(en_temp == 2'b01 ) //开始信号稳定的时候跳到数据状态去传输数据

next_state = DATA;

else

next_state = cur_state;

end

DATA:begin

if(cnt_bit == 5'd16 && cnt_delay >= DELAY - 1)

next_state = STOP;

else

next_state = cur_state;

end

STOP:begin

if(cnt_delay >= DELAY - 1)

next_state = IDLE;

else

next_state = cur_state;

end

endcase

//__________________________state3_________________________________//

always@(posedge sysclk)

if(!rst_n)begin

cnt_bit <= 5'd0;

RCK <= 1'b0;

data_temp <= 16'd0;

Done <= 1'b0;

DA <= 1'b0;

end

elsecase(cur_state)

IDLE:begin

cnt_bit <= 5'd0;

RCK <= 1'b0;

data_temp <= Data;

Done <= 1'b0;

DA <= 1'b0;

end

DATA:begin

if(cnt_delay >= DELAY - 1)begin

DA <= data_temp[15];

data_temp <= {data_temp[14:0],1'b0};

end

else begin

DA <= DA;

data_temp <= data_temp;

end

if(cnt_delay >= DELAY - 1 && cnt_bit >= 5'd16)

cnt_bit <= 5'd0;

else if(cnt_delay >= DELAY - 1)

cnt_bit <= cnt_bit + 5'd1;

else

cnt_bit <= cnt_bit;

Done <= 1'b0;

RCK <= 1'b0;

end

STOP:begin

if(cnt_delay == 1)

RCK <= 1'b1;

else

RCK <= 1'b0;

if(cnt_delay >= DELAY - 1)

Done <= 1'b1;

else

Done <= 1'b0;

cnt_bit <= 5'd0;

end

endcase

endmodule

用户_15432

二牛学FPGA

用户_15432

用户_15425

Keven

二牛学FPGA

用户_15425

用户_15425

用户_15432

Keven